Proceedings of the

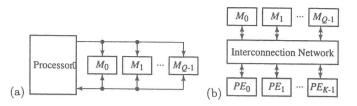

# Second International Samos Workshop on

Systems, Architectures, Modeling, and Simulation

# **SAMOS 2002**

July 22-25, 2002 Research and Training Institute of east Aegean Samos, Greece

supported by

**Dutch Technology Foundation (STW)**

# Copyright

Copyright © 2002 by the SAMOS Initiative. Permission to make digital or hard copies of parts of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page.

SAMOS ISBN : 90 - 9016023 - X SAMOS Order Number 2002-0722

# **Previous Publications**

A selection of papers presented at the SAMOS 2001 workshop have been published in Springer's Lecture Notes in Computer Science LNCS 2268 *Embedded Processor Design Challenges*

Copy ordering

Additional copies of this proceedings may be ordered from:

SAMOS Initiative, P.O. Box 9512 2300 Leiden, The Netherlands

Phone (+31 71) 527 5778 Fax (+31 71) 527 6985 E-mail edd@liacs.nl

# Message from the organizers

# **Modeling & Simulation**

Modeling of Intra-task Parallelism in Sesame Andy D. Pimentel, Frank P. Terpstra, Simon Polstra, Joe E. Coffland

Energy Estimation for Piecewise Regular Processor Arrays Frank Hannig, Jürgen Teich

Automatic Synthesis of Efficient Interfaces for Compiled Regular

Architectures Steven Derrien, Anne-Claire Quillon, Patrice Quinton, Tanguy Risset, Charles Wagner

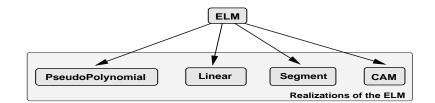

Realizations of the Extended Linearization Model in the Compaan Tool

Chain Alexandru Turjan, Bart Kienhuis, Ed Deprettere

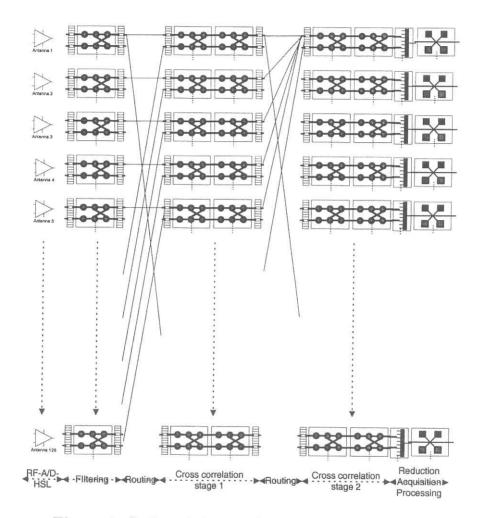

A scalable platform for large scale array signal processing systems

specification and prototyping Sylvain Alliot, Ed Deprettere

# **Reconfigurable Architecture**

Future Directions of (Programmable and Reconfigurable) Embedded Processors Stephan Wong, Stamatis Vassiliadis, Sorin Cotofana

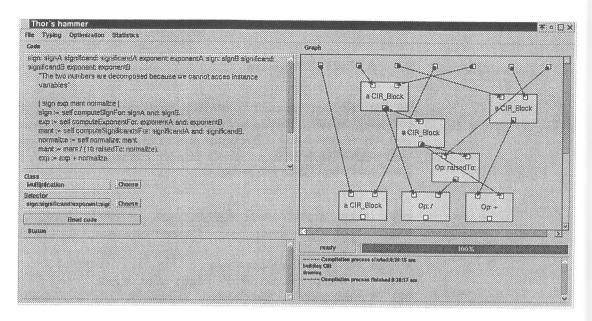

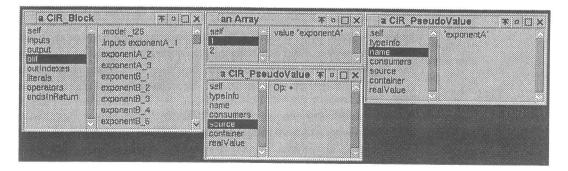

A high level synthesis framework for reconfigurable architectures Loïc Lagadec, Bernard Pottier, Oscar Villellas-Guillen

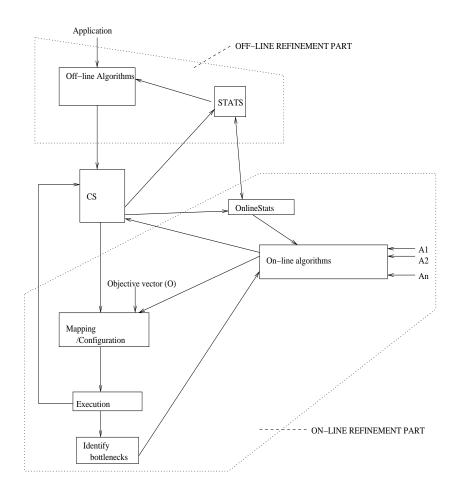

Goal-Driven Reconfiguration of Polymorphous Architectures Sumit Lohani, Shuvra S. Bhattacharvva

# Processors

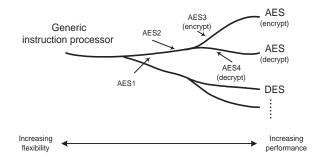

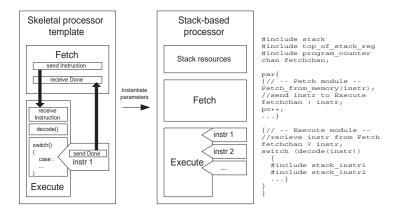

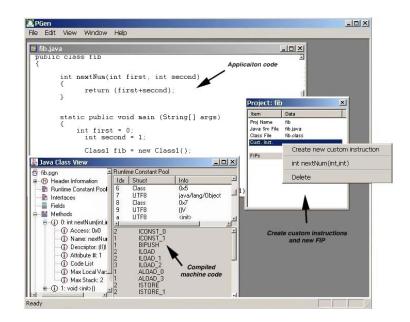

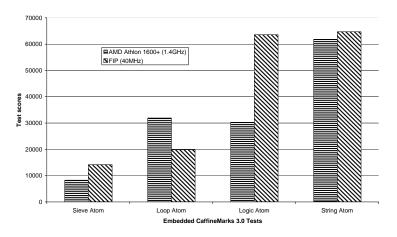

Customising Flexible Instruction Processors: a Tutorial Introduction Shay Ping Seng, Wahne Luk, Peter Y.K. Cheung

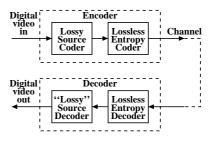

Entropy Decoding on TriMedia/CPU64 Miha Sima, Evert-Jan Pol, Jos T.J. van Eijndhoven, Sorin Cotofana, Stamatis Vassiliadis

Stride Permutation Access in Interleaved Memory Systems Jarmo Takala, Tuomas Järvinen

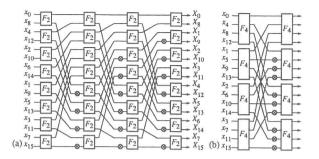

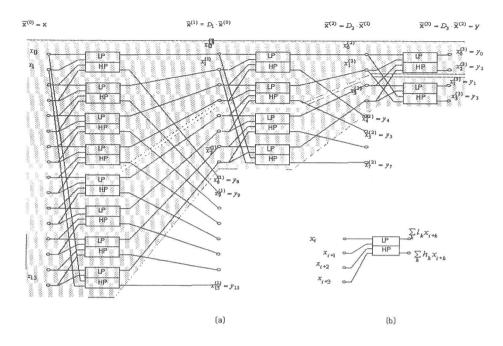

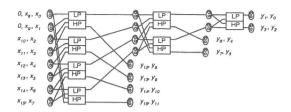

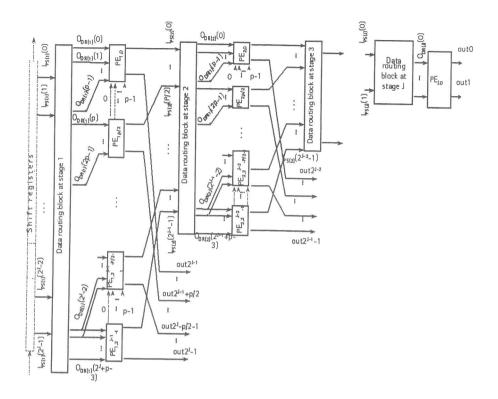

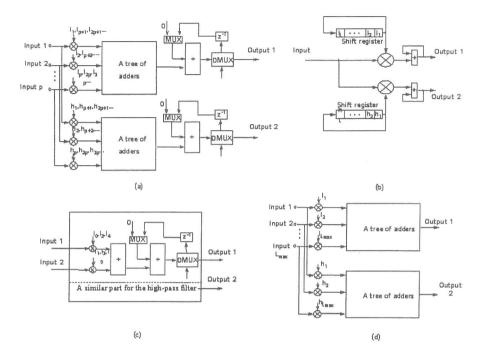

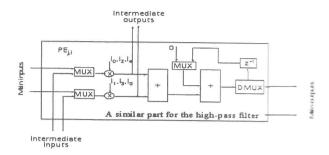

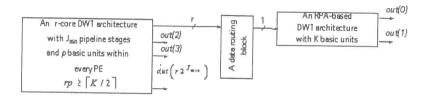

Highly Efficient Scalable Parallel-Pipelined Architectures for Discrete

Wavelet Transforms David Guevorkian, Petri Liuha, Aki Launiainen, Ville Lappalainen

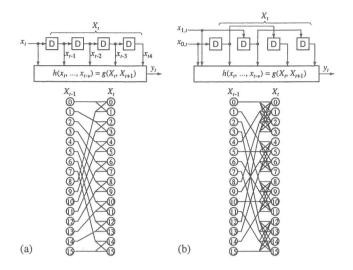

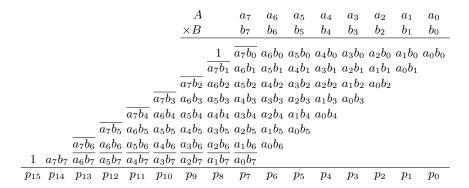

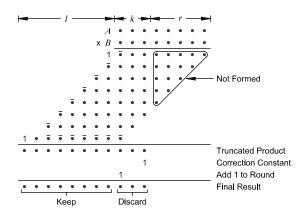

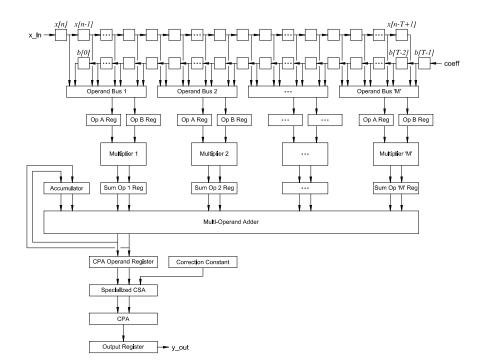

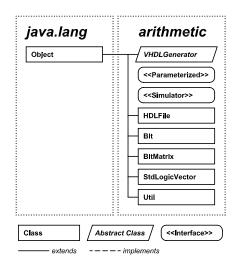

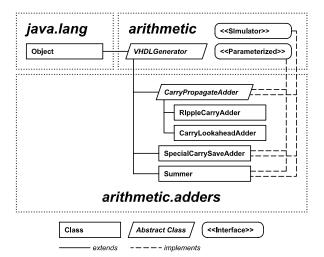

Automatic VHDL Model Generation of Parameterized FIR Filters E.George Walters III, John Glossner, Michael J. Schulte

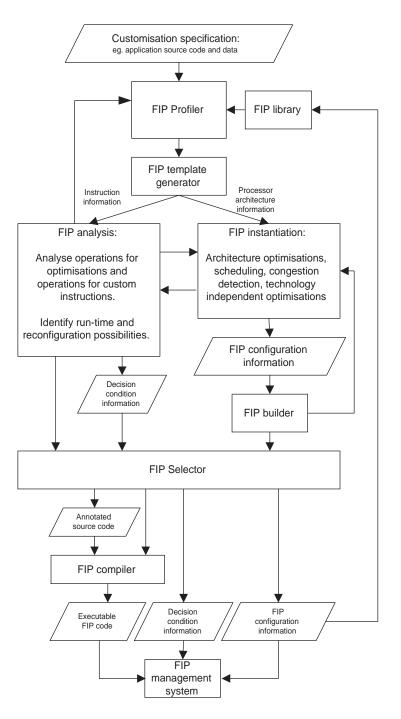

# Abstract

Hardware support for monitoring applications Kostas Anagnostakis, Herbert Bos

# Message from the Organizers

The SAMOS Initiative is an *International Informal Initiative* that emerged from de facto dependencies between leading research programs conducted in Maryland (University of Maryland), The Netherlands (Delft, Leiden, and Amsterdam Universities), Paderborn (Paderborn University), and Rennes (IRISA), headed by Shuvra Bhattacharyya, Stamatis Vassiliadis, Ed Deprettere, Andy Pimentel, Juergen Teich, and Patrice Quinton, respectively.

The SAMOS 2001 workshop emerged from an attempt to organize a visiting program among the above mentioned researchers: Why not meeting each other in one place instead of organizing point-to-point meetings? Stamatis Vassiliadis originating from the Island of Samos in Greece proposed to meet there, and so it happened. The SAMOS 2001 informal workshop was a successful event, and the initiators decided to go for a 2002 workshop as well. The workshop is by invitation only, and the selection criterion is that the chance for research co-operation is maximized.

Embedded systems design is an emerging field of research that addresses many challenging problems. No single expert is capable of covering the whole field and, therefore, co-operation is indispensable. Who can model applications; who can model architectures; who can model mappings of applications into architectures; who can perform exploration, and who can synthesize. Why would a researcher try to master all aspects of embedded systems design when an approach can be conceived in which abstraction layers can be assigned to layer experts. The Embedded systems design problem is a divide and rule game with a win-win flavor. The SAMOS Initiative aims at identifying the players and to get them involved in the game.

# Modeling of Intra-task Parallelism in Sesame

Andy D. Pimentel, Frank P. Terpstra, Simon Polstra, and Joe E. Coffland

Computer Architecture & Parallel Systems group Dept. of Computer Science, University of Amsterdam Kruislaan 403, 1098 SJ Amsterdam, The Netherlands {andy,ftrpstra,spolstra,jcofflan}@science.uva.nl

**Abstract.** The Sesame environment provides modeling and simulation methods and tools for the efficient design space exploration of heterogeneous embedded multimedia systems. It specifically targets the performance evaluation of embedded systems architectures in which task-level parallelism is available. In this paper, we present techniques that allow Sesame to also model intra-task parallelism exploited at the architecture level. Moreover, we describe a case study using a QR decomposition application to validate our modeling concepts. To this end, we were able to compare the performance estimates of our abstract system models with the results of an actual FPGA implementation. The results are promising in the sense that they show good accuracy with minimal modeling effort.

# **1** Introduction

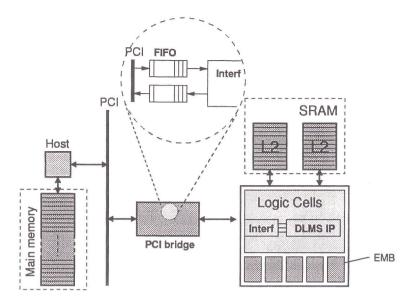

Modern embedded systems, like those for media and signal processing, often have a heterogeneous system architecture, consisting of components in the range from fully programmable processor cores to dedicated hardware components. Increasingly, these components are integrated as a system-on-chip exploiting task-level parallelism in applications. Due to the high degree of programmability that is usually provided by such embedded systems, they typically allow for targeting a whole range of applications with varying demands. All of the above characteristics greatly complicate the design of these embedded systems, making it more and more important to have good tools available for exploring different design choices at an early stage in the design.

In the context of the Artemis (ARchitectures and meThods for Embedded MedIa Systems) project [19], we are developing an architecture workbench which provides modeling and simulation methods and tools for the efficient design space exploration of heterogeneous embedded multimedia systems. This architecture workbench should allow for rapid performance evaluation of different architecture designs, application to architecture mappings, and hardware/software partitionings and it should do so at multiple levels of abstraction *and* for a wide range of multimedia applications.

In this paper, our focus is on a prototype modeling and simulation environment, called Sesame [18]. According to the Artemis modeling methodology [19], this environment uses separate application models and architecture models and an explicit mapping step to map an application model onto an architecture model. This mapping is realized by means of trace-driven co-simulation of the application and architecture models, where the execution of the application model generates application events that represent

the application workload imposed on the architecture. Application models consist of communicating parallel processes, thereby expressing the task-level parallelism available in the applications. By mapping the event traces generated by different application model processes onto the various system architecture components, this task-level parallelism is exploited at the architecture level. In addition, the underlying architecture may also exploit intra-task parallelism inside a single trace. This paper presents the newly added techniques Sesame applies to model architectures that exploit such intra-task parallelism. Moreover, using a case study with the QR decomposition algorithm as application, we demonstrate the effectiveness of our modeling methodology.

The remainder of this paper is organized as follows. Section 2 briefly describes related work in the area of modeling and simulation of complex embedded systems. Section 3 gives a general overview of the Sesame modeling and simulation environment, while in Section 4 we present a more detailed description of Sesame's synchronization layer. In Sections 5 and 6, we describe the methods applied to model intra-task parallelism and discuss their impact on Sesame's synchronization and architecture model layers. Section 7 presents some validation results we obtained from the case study with the QR decomposition application. Finally, Section 8 discusses several open issues and Section 9 concludes the paper.

## 2 Related work

Various research groups are active in the field of modeling and simulating heterogeneous embedded systems, of which some are academic efforts (e.g., [6, 11, 9]) and others commercial [8] and industrial efforts (e.g., [5]). Many efforts in this field *co-simulate* the software parts, which are mapped onto a programmable processor, and the hardware components and their interactions together in one simulation. Because an explicit distinction is made between software and hardware simulation, it must be known which application components will be performed in software and which ones in hardware before a system model is built. This significantly complicates the performance evaluation of different hardware/software partitioning schemes since a new system model may be required for the assessment of each partitioning.

A number of exploration environments, such as VCC [1], Polis [4] and eArchitect [2], facilitate more flexible system-level design space exploration by providing support for mapping a behavioral application specification to an architecture specification. Within the Artemis project, however, we try to push the separation of modeling application behavior and modeling architectural constraints at the system level to even greater extents. To this end, we apply trace-driven co-simulation of application and architecture models. Like was shown in [18], this leads to efficient exploration of different design alternatives while also yielding a high degree of reusability. The work of [15] also uses a trace-driven approach, but this is done to extract communication behavior for studying on-chip communication architectures. Rather than using the traces as input to an architecture simulator, their traces are analyzed statically. In addition, a traditional hardware/software co-simulation stage is required in order to generate the traces.

Finally, the Archer project [23] shows a lot of similarities with our work. This is due to the fact that both our work and Archer are spin-offs from the Spade project [17].

A major difference is, however, that Archer follows an entirely different applicationto-architecture mapping approach. Instead of using event-traces, it maps symbolic programs, which are derived from the application model, onto architecture resources.

### **3** The Sesame modeling and simulation environment

The Sesame modeling and simulation environment [18], which builds upon the groundlaying work of the Spade framework [17], facilitates the performance analysis of embedded systems architectures in a way that directly reflects the so-called Y-chart design approach [13]. In Y-chart based design, a designer studies the target applications, makes some initial calculations, and proposes an architecture. The performance of this architecture is then quantitatively evaluated and compared against alternative architectures. For such performance analysis, each application is mapped onto the architecture under investigation and the performance of each application-architecture combination is evaluated. Subsequently, the resulting performance numbers may inspire the designer to improve the architecture, restructure the application(s) or modify the mapping of the application(s).

In accordance to the Y-chart approach, Sesame recognizes separate application and architecture models within a system simulation. An application model describes the functional behavior of an application, including both computation and communication behavior. The architecture model defines architecture resources and captures their performance constraints. Essential in this modeling methodology is that an application model is independent from architectural specifics, assumptions on hardware/software partitioning, and timing characteristics. As a result, a single application model can be used to exercise different hardware/software partitionings and can be mapped onto a range of architecture models, possibly representing different system architectures or simply modeling the same system architecture at various levels of abstraction. After mapping, an application model is co-simulated with an architecture model allowing for evaluation of the system performance of a particular application, mapping, and underlying architecture.

For application modeling, Sesame uses the Kahn Process Network (KPN) model of computation [12] in which parallel processes – implemented in a high level language – communicate with each other via unbounded FIFO channels. In the Kahn paradigm, reading from channels is done in a blocking manner, while writing is non-blocking. The computational behavior of an application is captured by instrumenting the code of each Kahn process with annotations which describe the application's computational actions. The reading from or writing to Kahn channels represents the communication behavior of a process within the application model. By executing the Kahn model, each process records its actions in order to generate a trace of application events, which is necessary for driving an architecture model. Initially, the application events typically are coarse grained, such as *execute(DCT)* or *read(pixel-block,channel.id)*, and they may be refined as the underlying architecture models are refined. We note that in the remainder of this paper, computational application events will be referred to as *execute events*.

To execute Kahn application models, and thereby generating the application events that represent the workload imposed on the architecture, Sesame features a process

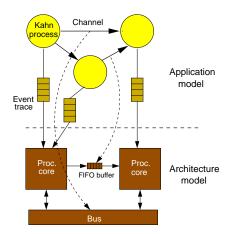

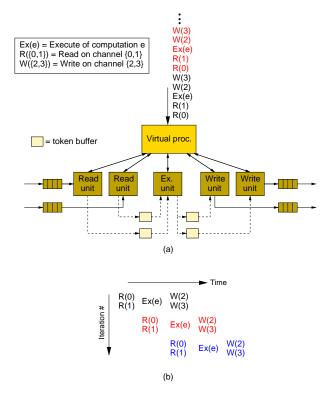

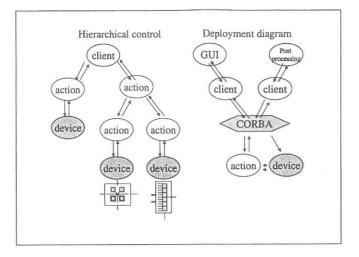

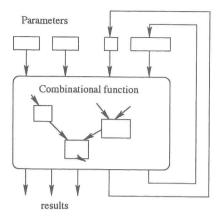

Fig. 1. Mapping a Kahn application model onto an architecture model.

network execution engine supporting Kahn semantics. This execution engine runs the Kahn processes as separate threads using the Pthreads package. For now, there is a limitation that the Kahn processes need to be written in C++. In the near future, C and Java support will be added. The structure of the application models (i.e., which processes are used in the model and how they are connected to each other) is described in a language called YML (Y-chart Modeling Language)[22]. This is an XML-based language which is similar to Ptolemy's MoML [16] but is slightly less generic in the sense that YML only needs to support a few simulation domains. As a consequence, YML only supports a subset of MoML's features. However, YML provides one additional feature in comparison to MoML as it contains built-in scripting support. This allows for loop-like constructs, mapping & connectivity functions, and so on, which facilitate the description of large and complex models.

The performance of an architecture can be evaluated by simulating the performance consequences of the incoming execute and communication events from an application model. This requires an explicit mapping of the processes and channels of a Kahn application model onto the components of the architecture model. The generated trace of application events from a specific Kahn process is therefore routed towards a specific component inside the architecture model by using a trace-event queue. This is illustrated in Figure 1. Since the application-model execution engine and the architecture simulator run as separate processes<sup>1</sup>, these trace-event queues are currently implemented via Unix named-pipes. Alternative implementations of the queues, such as using shared memory, are foreseen in the future. If two or more Kahn processes are mapped onto a single architecture component (e.g., when several application tasks are mapped onto a

<sup>&</sup>lt;sup>1</sup> Running the application-model execution engine as a separate process also makes it easy to analyze the application model in isolation. This can be beneficial as it allows for investigation of the upper bounds of the performance and may lead to early recognition of bottlenecks within the application itself.

microprocessor), then the events from the different trace-event queues need to be scheduled. The next section explains how this is done.

An architecture model solely accounts for architectural (performance) constraints and therefore does not need to model functional behavior. This is possible because the functional behavior is already captured in the application model, which subsequently drives the architecture simulation. An architecture model is constructed from generic building blocks provided by a library. This library contains template performance models for processing cores, communication media (like busses) and different types of memory. These template models can be freely extended and adapted. All architecture models in Sesame are implemented using a small but powerful discrete-event simulation language, called Pearl, which provides easy construction of the models and fast simulation [18]. The structure of architecture models – specifying which building blocks are used from the library and the way they are connected – is also described in YML.

## 4 The synchronization layer

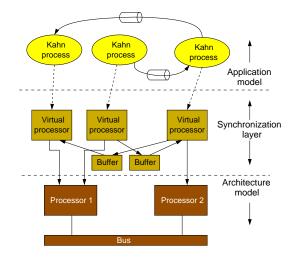

When multiple Kahn application model processes are mapped onto a single architecture model component, the event traces need to be scheduled. For this purpose, Sesame provides an intermediate synchronization layer, which is illustrated in Figure 2. This layer guarantees deadlock-free scheduling of the application events and forms the application and architecture dependent structure that connects the architecture-independent application model with the application-independent architecture model. The synchronization layer, which can be automatically generated from the YML description of an application model, consists of virtual processor components and FIFO buffers for communication between the virtual processors. There is a one-to-one relationship between the Kahn processes in the application model and the virtual processors in the synchronization layer. This is also true for the Kahn channels and the FIFO channels in the synchronization layer, except for the fact that the buffers of the latter channels are limited in size. Their size is parameterized and dependent on the modeled architecture. A virtual processor reads in an application trace from a Kahn process and dispatches the events to a processing component in the architecture model. The mapping of a virtual processor onto a processing component in the architecture model is parameterized and thus freely adjustable. Currently, this virtual processor to architectural processor mapping is specified in the YML description of the architecture model. We are working, however, towards an approach in which this mapping is specified in a separate YML mapping description.

As can be seen from Figure 2, multiple virtual processors can be mapped onto a single processor in the architecture model. In this scheme, execute events are directly dispatched by a virtual processor to the processor model. The latter subsequently schedules the events originating from different virtual processors according to some given policy (FCFS by default) and models their timing consequences. For communication events, however, the appropriate buffer at the synchronization layer is first consulted to check whether or not a communication is safe to take place so that no deadlock can occur. Only if it is found to be safe (i.e., for read events the data should be available and for write events there should be room in the target buffer), then communication events

**Fig. 2.** The three layers within Sesame: the application model layer, the architecture model layer, and the synchronization layer which interfaces between application and architecture models.

may be dispatched to the processor component in the architecture model. As long as a communication event cannot be dispatched, the virtual processor blocks. This is possible because the synchronization layer is, like the architecture model, implemented in the Pearl simulation language and executes in the same simulation-time domain as the architecture model. As a consequence, the synchronization layer accounts for synchronization delays of communicating application processes mapped onto the underlying architecture, while the architecture model accounts for the computational latencies and the pure communication latencies (i.e., how long does it take to transfer an amount of data from X to Y). Each time a virtual processor dispatches an application event (either computation or communication) to a processor in the architecture model, it is blocked (in simulated time) until the event's simulation at the architecture level has finished.

The idea of concentrating synchronization behavior in a synchronization layer and separating it from (the latencies caused by) data transmission behavior is somewhat similar to the synchronization graph concept of [20]. However, our synchronization layer seems to be more flexible since it is dynamically scheduled and behaves like a "Kahn" process network in which the FIFO buffers are bounded. As a consequence of the dynamic scheduling of the synchronization layer and the architecture model (remember that they both are executed in the same discrete-event simulation domain), dynamics at the architecture level such as contention can easily be taken into account within the synchronization layer.

# 5 Exploiting intra-task parallelism

Initially, Sesame only modeled the architecture's processing cores as black boxes which sequentially simulate the timing consequences of the incoming (linear) trace of application events. However, the architecture under investigation may also want to exploit

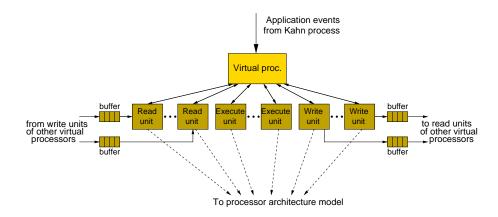

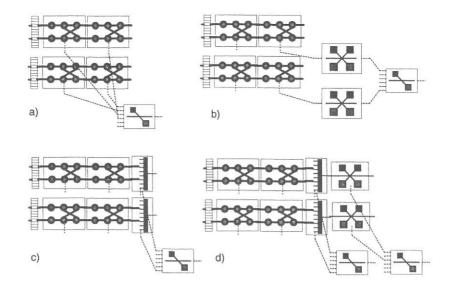

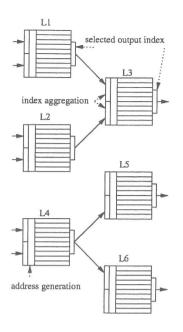

Fig. 3. Refining a virtual processor in the synchronization layer.

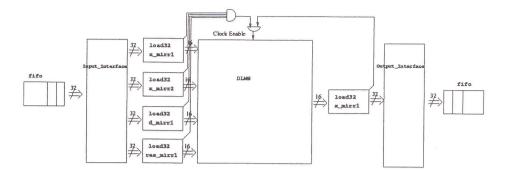

intra-task parallelism which is present in a single event trace from a Kahn application process. For example, a processing element may have multiple communication units which allow for performing independent reads and writes in parallel, or it may have multiple execution units for concurrently processing independent computations. To support the modeling and simulation of such intra-task parallelism, we extended Sesame's model library with component models that allow for refining the virtual processors in the synchronization layer and the processor components within the architecture models.

Figure 3 shows how a virtual processor in the synchronization layer, like the ones depicted in Figure 2, is refined. The virtual processor component now acts as a frontend to a range of (virtual) functional units. These functional units consist of read, write and execution units which can operate in parallel. The new virtual processor component has a symbolic-instruction window of parameterizable size in which it stores incoming application events and with which it analyzes them for parallel execution. According to the event type (execute event type, channel from/to which is read/written, etc.), the virtual processor dispatches incoming events to the appropriate functional unit. The number of entries in the symbolic-instruction window limits the number of outstand-ing (dispatched but not finished) events in the virtual processor. A window size of one implies sequential handling of the application events. In Figure 3, the arrows from the functional units transmit whenever the simulation of an event has finished.

The read and write units are connected via buffers<sup>2</sup> with other virtual processors, like discussed in Section 4, in order to establish the modeling of synchronizations between Kahn application processes in accordance to their mapping onto the underlying architecture. Hence, the read and write units do not dispatch a communication event to the architecture model unless it is safe to do so, i.e., the event cannot cause a deadlock. In addition, the execution and write units do not dispatch their incoming application events to the architecture model before all dependencies for these events are resolved.

<sup>&</sup>lt;sup>2</sup> Per read or write unit, there may be multiple buffers connected.

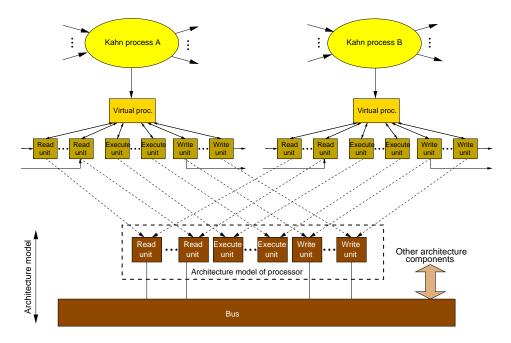

Fig. 4. Mapping multiple refined virtual processors onto a refined processor architecture model.

We will elaborate on this issue in the next section, which discusses the internal synchronizations within a refined virtual processor component.

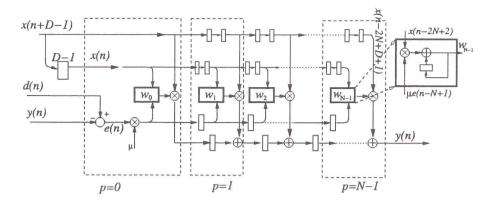

Figure 4 illustrates how the refined virtual processors can be mapped onto a processor component in the architecture model which has been refined as well. The read units from the virtual processors that are mapped onto the same processor at the architecture level, are connected to the read units of the processor in the architecture model. Likewise, the virtual execution units are connected to the execution units of the processor architecture model, and so on. The functional units in the architecture model may again be black-box models which sequentially account for the timing consequences of the incoming application events dispatched by the synchronization layer. Alternatively, they may also be further refined. For example, a refined execution unit may model internally pipelined execution of execute events. Furthermore, in the example of Figure 4 all communication units in the architecture model are connected to a bus model. In reality, communication units within the architecture model may have different connections with each other (directly across a bus or via shared memory, point-to-point, etc.).

### 6 Dataflow for functional unit synchronization

To properly model parallel execution of application events from a single event trace, the dependencies between the events should be taken into account. For example, an execution unit in the synchronization layer may only dispatch an execute event to the execution unit in the architecture model when the read events it depends on have been sim-

**Fig. 5.** Dataflow-based synchronization to resolve dependencies between functional units in a virtual processor. The architecture shown in (a) exploits pipeline parallelism, which is illustrated in (b).

ulated and delivered the required input for the execute. Likewise, a write event may be dispatched to the architecture model when it is safe to do so and when the read/execute events it depends on have been simulated.

Consider the example in Figure 5(a) in which a virtual processor is shown for a processor architecture with a pipeline of two read units, one execution unit and two write units. In this example, the trace generating Kahn process reads/writes from/to two channels which are mapped onto separate read and write units. The execute events in this example are dependent on the two preceding read events, while the two write events are dependent on the preceding execute event. In Figure 5(b) the resulting pipeline parallelism is illustrated.

The synchronization between the functional units in order to resolve dependencies is done via buffered token channels. In Figure 5(a), for example, the read units have a token channel to the execution unit. A read unit sends a token along its token channel whenever a read event finished, i.e., has been simulated at architecture level. The size of the token channel's buffer determines how far the read unit can run ahead, or in other words, the amount of internal buffering a read unit has. If the token channel's buffer is

```

class v_read_unit

[...]

sig_room : (unit_id : integer)

{ }

read : ()

{

block(sig_room); // block until there's room in token buffer

input_buffer ! get(); // wait until there's data in input FIFO

ex_unit !! sig_data(unit_id); // send token to execution unit

virt_proc !! op_done(); // signal completion to virt. processor

}

{

while (1) {

block( read, signal_room );

}

```

Fig. 6. Pearl code for a read unit object from the synchronization layer.

full, then the read unit stalls until the execution unit has removed one or more tokens from the channel's buffer. During such a stall, a read unit cannot handle new read events.

In our example, the execution unit reads the tokens generated by the read units. Associated with each execute event type, there are two *bitmaps*. The first one describes on which token channels the particular execute event is dependent, i.e., which read units produce data needed by the execute event. The second bitmap describes which functional units are dependent on the execute event. So, it relates to output token channels.

The execution unit must have received a token from all of the required token channels, implying that dependencies have been resolved, before the execute event may be dispatched to the architecture model. Likewise, after an execute event has been simulated at the architecture level, the execution unit sends tokens along the required output token channels (as specified by the second bitmap). As a consequence, the write units, which are waiting for tokens from the execution unit, are enabled to dispatch dependent write events to the architecture model. To summarize, synchronizations due to dependencies between functional units in the synchronization layer are handled using the dataflow principle with token transmissions between the functional units. To be more specific, this dataflow mechanism adheres to integer-controlled dataflow [7]. Of course, the placement of token channels between functional units and their buffer sizes are freely adjustable. For the time being, however, we slightly restricted the choice of functional units as we currently assume that there can be only one execution unit per processor. In Section 8, we come back to this issue and indicate how our modeling concepts may be extended to support multiple execution units per processor.

To give an impression of how the implemented models look like, Figure 6 shows the Pearl code for a read unit from the synchronization layer (the variable declarations have been omitted). As Pearl is an object-based language and architecture components are modeled by objects, the code shown in Figure 6 embodies the class of read unit objects. As the explanation of the code is beyond the scope of this paper, the interested reader is referred to [18] for a more detailed discussion of a Pearl code sample.

In our implementation, it is straightforward to change the policy defining when token buffers can be read from or written to. More specifically, a functional unit can wait until all of its required tokens are available before it retrieves the tokens from the buffers or it can retrieve a required token whenever it becomes available. In the latter case, the producer of the token may be unblocked earlier and thereby allowing it to proceed with processing new application events.

We note that the synchronizations between functional units are only performed in the synchronization layer and are not needed within the underlying architecture model. This is because once application events are dispatched from the synchronization layer to the architecture model, they are safe to simulate, i.e., they cannot cause deadlocks and their dependencies have been resolved. This scheme nicely fits our approach in which all synchronization overheads are accounted for in the synchronization layer.

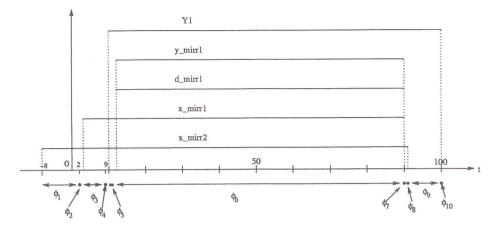

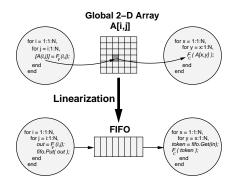

## 7 A case study: QR decomposition

To validate the previously presented concepts on how to model the exploitation of intratask parallelism, we have performed a case study using a set of application model instances of the well-understood QR decomposition algorithm. These application models are the result of the Compaan work [14] done at Leiden University. The Compaan tool is able to automatically generate Kahn application models from nested loop programs written in Matlab, which in our case is the QR decomposition algorithm. In addition, it can perform code transformations such as loop unrolling to increase task-level parallelism inside applications [21].

The Kahn application models generated by the Compaan tool are suitable for a direct implementation in hardware on an FPGA. For this purpose, application models are translated into VHDL [10]. This gives us the unique opportunity to validate our abstract architecture models against an actual FPGA implementation. In the VHDL implementation of a Kahn application model, pre-defined node components are connected in a network. This is done according to the connections between the processes in the application model. The node components, which represent the functional behavior of the Kahn processes in the application model, are implemented in a pipelined fashion that is similar to the one shown in Figure 5. Conceptually, this means that each node component contains a number of read and write units and a single execution unit. So, besides exploiting task-level parallelism by the VHDL network of node components, each node component also exploits intra-task parallelism using its internally pipelined architecture.

Regarding the QR application, we studied five different instances of its application model generated by Compaan. In each instance, the loops in the code have been unrolled a different number of times. This loop unrolling creates new Kahn processes, thereby increasing the task-level parallelism available in the application [21]. Additional information on the Kahn application model of the QR decomposition algorithm can be found in [10]. For each of the application model instances, we described the structure of the application model in YML to be able to run the model with Sesame's application-model execution engine. As a side-note, it is worth mentioning that the gen-

eration of the YML descriptions of the application model instances is performed fully automatically by means of a visitor tool.

Our Sesame architecture model, onto which the QR application model instances are mapped, is similar to the VHDL implementation of a Kahn application model in the sense that it also consists of processor components connected in a network with a topology identical to that of the application model. Each processor component is modeled with our refined (virtual) processor model (see Section 5) and uses the pipelined architecture as shown in Figure 5(a). Between processor components in the architecture model there are point-to-point FIFO channels.

Recall that the structure of Sesame's architecture models is described in YML. Because of YML's built-in scripting support, this allowed us to construct a generic reusable template for the refined (virtual) processor model. The processor network in the architecture model is thus obtained by repetitively instantiating this template with possibly different parameters and linking these processor instances together according to the topology of the application model. This topology information is derived from our YML description of the Kahn application model.

#### 7.1 Experiments

Our first experiments were performed using a Sesame synchronization layer and architecture model with the following characteristics. The size of the FIFO buffers is 256 elements, which guarantees deadlock-free execution of the studied application model instances [10]. The functional units of processor components as well as the FIFO buffers are modeled as black boxes. Read and write operations to the FIFO buffers take 3 cycles each as specified in [10], while all execute events<sup>3</sup> are handled in a single cycle. The latter reflects the performance of a fully-utilized internal execution pipeline with a single-cycle throughput. Moreover, the token channels between the functional units at the synchronization layer have single-entry buffers. This means that the read and execution units cannot produce more than one result before consumption, i.e., they have only limited internal buffering.

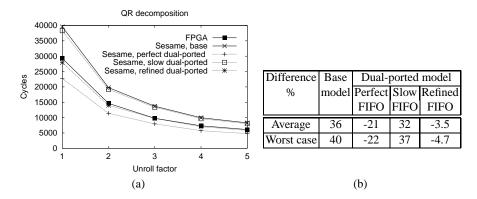

In Figure 7(a), the performance of the FPGA implementation (modeled in VHDL) of the five QR application instances – with loop unroll factors of one to five – is shown. The figure also shows the performance estimates of our black-box Sesame model for these application model instances. These results are referred to as the *base* model in Figure 7. As shown in Figure 7(b), the black-box model yields an average error of 36% and a worst-case error of 40% with respect to the performance results of the FPGA implementation. The Sesame (base) performance estimates show the correct trend behavior but are consistently more pessimistic than those for the FPGA.

According to [10], the FPGA buffer implementation is based around a dual-ported RAM, where our base model models single-ported buffers. This explains why the results of the base model are pessimistic. As a next step, we "opened up" the black-box FIFO model and adapted it to include dual-ported behavior. To this end, we modeled three variants of dual-ported FIFO buffers. Two of these variants represent implementation extremes, while the third one reflects the performance behavior of the actual FPGA

<sup>&</sup>lt;sup>3</sup> In the QR application model, the execute events consist of vectorize and rotate operations.

**Fig. 7.** Validation results of our Sesame models for the QR decomposition application against the results from an actual FPGA implementation. The graph in (a) shows the (estimated) performance for five application instances with different loop unroll factors. The table in (b) gives the differences (in %) between estimates from our models and the FPGA numbers.

implementation. The results of these three dual-ported FIFO models are also shown in Figure 7. The curve labeled with *perfect dual-ported* shows the performance estimates when modeling the FIFO buffers as being perfectly dual-ported. The latter means that read and write operations on a buffer can be performed entirely in parallel, even when the buffer is empty. So, when receiving a read request in the empty buffer state, the read is blocked until a write request is coming in after which the incoming (written) data is immediately forwarded to the reading party. Consequently, both read and write latencies are entirely overlapped.

At the other extreme, the curve labeled with *slow dual-ported* in Figure 7 shows the Sesame performance estimates when modeling dual-ported FIFO buffers which are entirely sequential at the empty state. So, when receiving a read request in the empty buffer state, the read is blocked until a write has occurred and finished writing its data into the buffer (in our model, this takes 3 cycles).

Finally, the curve labeled with *refined dual-ported*, shows the Sesame results when incorporating more detailed knowledge on the actual FPGA buffer implementation into our model. Details on the FPGA implementation indicated that a monolithic 3-cycle read/write latency for the FIFO buffers does not reflect the actual behavior. In reality, the throughput at both sides of a FIFO buffer is 1 operation per 3 cycles, while the read latency turned out to be only 1 cycle. In our *refined dual-ported* model we have therefore split the 3-cycle delay into three 1-cycle delays and placed them at the appropriate places according to specification of the FPGA buffer implementation. This means that we refined the timing within our model while keeping its abstract structure intact.

Three important conclusions can be drawn from the results in Figure 7. First, the results reconfirm the modeling flexibility of Sesame. This is because we were able to model the three dual-ported buffer designs by changing less than ten lines in the code of the base model. Second, the results from the 'perfect' and 'slow' models – representing the two FIFO buffer implementation extremes – immediately indicate that the average

accuracy of Sesame's performance estimates must lie in the range of -21% and +32%. In fact, our 'refined' model demonstrates how close our performance estimates can approximate reality since it yields an average error of only 3.5% and a worst case error of 4.7%. Knowing that Sesame targets performance evaluation in an early design stage and therefore models at a high level of abstraction, these accuracy numbers are very promising. Third, our results indicate that the studied hardware implementations of the QR decomposition application are highly sensitive to different FIFO buffer designs. Since the performance estimates of the 'perfect' buffer model show a speedup of 68% over the results of the 'slow' buffer model, the handling of the empty state in the FIFO buffer seems to be an important design issue.

Since Sesame targets performance evaluation in an early design stage, where the design space that needs to be explored typically is very large, the required modeling effort and the simulation speed of Sesame is worth noting. The architecture models in this case study, including the components in the synchronization layer, consist of less than 500 lines of Pearl code. It takes Sesame about 16 seconds on a 333MHz Sun Ultra 10 to perform the architecture simulation for all five application model instances in a batch.

#### 8 Discussion

So far, we have assumed that in the set of functional units of a refined (virtual) processor there is only one execution unit. Processing cores, however, might have multiple execution units that can perform computations in parallel. We are currently investigating whether or not our dataflow approach is sufficient for dealing with dependencies between execution units. In any case, for such inter-execution dependencies we need to extend our dataflow scheme such that tokens are typed, like in the tagged-token model [3]. With the typed tokens, an execution unit can differentiate between the production of results from different execute event types. To support such typed tokens, the bitmaps need to be extended from single-bit values to multiple-bit values to be able to specify which token types are required for an application event.

Moreover, we currently use static bitmaps per execute event type. We found, however, that this causes problems when, for example, execute events of the same type require data from different read units in different stages of the application model's execution. This can be solved by dynamically adding the bitmap information to the execute events in the traces.

# 9 Conclusions

In this paper, we presented the techniques applied by the Sesame modeling and simulation environment to model intra-task parallelism exploited at the architecture level for task-parallel applications. To this end, our processor models are refined to the level of functional units which can operate in parallel and which are synchronized to resolve dependencies by means of a dataflow mechanism. Using a case study, in which we were able to compare our simulation results with the results from an actual FPGA implementation, we demonstrated that our modeling methodology is flexible and shows good accuracy.

### Acknowledgments

This research is supported by PROGRESS, the embedded systems research program of the Dutch organization for Scientific Research NWO, the Dutch Ministry of Economic Affairs and the Technology Foundation STW. We thank the people from the Embedded Real-time Computing group at Leiden University, and in particular Todor Stefanov, Bart Kienhuis, Vladimir Živković, Laurentiu Nicolae and Ed Deprettere, for providing the application models for the QR case study and for their invaluable feedback on this work. In addition, we would like to thank Tim Hariss from QinetiQ Ltd (UK) for providing us with the details on the FPGA implementation of the QR application.

#### References

- 1. Cadence Design Systems, Inc., http://www.cadence.com/.

- 2. Innoveda Inc., http://www.innoveda.com/.

- 3. Arvind and K. P. Gostelow. The U-Interpreter. IEEE Computer, 15(2):42-49, Feb. 1982.

- F. Balarin, E. Sentovich, M. Chiodo, P. Giusto, H. Hsieh, B. Tabbara, A. Jurecska, L. Lavagno, C. Passerone, K. Suzuki, and A. Sangiovanni-Vincentelli. *Hardware-Software Co-design of Embedded Systems – The POLIS approach*. Kluwer Academic Publishers, 1997.

- J.-Y. Brunel, E.A. de Kock, W.M. Kruijtzer, H.J.H.N. Kenter, and W.J.M. Smits. Communication refinement in video systems on chip. In *Proc. 7th Int. Workshop on Hardware/Software Codesign*, pages 142–146, May 1999.

- J. Buck, S. Ha, E. A. Lee, and D. G. Messerschmitt. Ptolemy: A framework for simulating and prototyping heterogeneous systems. *Int. Journal of Computer Simulation*, 4:155–182, Apr. 1994.

- 7. J. T. Buck. Static scheduling and code generation from dynamic dataflow graphs with integer valued control streams. In *Proc. of the 28th Asilomar conference on Signals, Systems, and Computers*, Oct. 1994.

- 8. P. Dreike and J. McCoy. Co-simulating software and hardware in embedded systems. *Embedded Systems Programming*, 10(6), June 1997.

- R.K. Gupta, C.N. Coelho Jr., and G. De Micheli. Synthesis and simulation of digital systems containing interacting hardware and software components. In *Proc. of the Design Automation Conference*, pages 225–230, June 1992.

- T. Harriss, R. Walke, B. Kienhuis, and E.F. Deprettere. Compilation from Matlab to process networks realized in FPGA. In Proc. of the 35th Asilomar conference on Signals, Systems, and Computers, Nov. 2001.

- 11. K. Hines and G. Borriello. Dynamic communication models in embedded system cosimulation. In *Proc. of the Design Automation Conference*, pages 395–400, June 1997.

- 12. G. Kahn. The semantics of a simple language for parallel programming. In *Proc. of the IFIP Congress 74*, 1974.

- B. Kienhuis, E.F. Deprettere, K.A. Vissers, and P. van der Wolf. An approach for quantitative analysis of application-specific dataflow architectures. In *Proc. of the Int. Conf. on Application-specific Systems, Architectures and Processors*, July 1997.

- B. Kienhuis, E. Rijpkema, and E.F. Deprettere. Compaan: Deriving process networks from Matlab for embedded signal processing architectures. In *Proc. of the 8th International Work*shop on Hardware/Software Codesign (CODES'2000), May 2000.

- K. Lahiri, A. Raghunathan, and S. Dey. System-level performance analysis for designing on-chip communication architectures. *IEEE Trans. on Computer-Aided Design of Integrated Circuits and Systems*, 20(6):768–783, June 2001.

- E. A. Lee and S. Neuendorffer. MoML a Modeling Markup Language in XML, version 0.4. Technical Report UCB/ERL M00/8, Electronics Research Lab, University of California, Berkeley, March 2000.

- P. Lieverse, P. van der Wolf, E.F. Deprettere, and K.A. Vissers. A methodology for architecture exploration of heterogeneous signal processing systems. *Journal of VLSI Signal Processing for Signal, Image and Video Technology*, 29(3):197–207, November 2001. Special issue on SiPS'99.

- A. D. Pimentel, S. Polstra, F. Terpstra, A. W. van Halderen, J. E. Coffland, and L.O. Hertzberger. Towards efficient design space exploration of heterogeneous embedded media systems. In *Proc. of the 1st Int. Workshop on Systems, Architectures, MOdeling, and Simulation (SAMOS)*, pages 57–73, July 2001.

- A.D. Pimentel, P. Lieverse, P. van der Wolf, L.O. Hertzberger, and E.F. Deprettere. Exploring embedded-systems architectures with Artemis. *IEEE Computer*, 34(11):57–63, Nov. 2001.

- 20. S. Sriram and S. S. Bhattacharyya. *Embedded Multiprocessors: Scheduling and Synchronization*. Marcel Dekker, Inc., 2000.

- T. Stefanov, B. Kienhuis, and E.F. Deprettere. Algorithmic transformation techniques for efficient exploration of alternative application instances. In *Proc. of the 10th Int. Symposium* on *Hardware/Software Codesign (CODES'02)*, pages 7–12, May 2002.

- 22. F. Terpstra. Design considerations and description of YML. Technical report, Univerity of Amsterdam, Jan. 2002.

- V. Živković, P. van der Wolf, E.F. Deprettere, and E.A. de Kock. Design space exploration of streaming multiprocessor architectures. To appear in the *Proc. of the IEEE Workshop on Signal Processing Systems (SIPS'02)*, Oct. 2002.

# Energy Estimation for Piecewise Regular Processor Arrays<sup>\*</sup>

Frank Hannig and Jürgen Teich

University of Paderborn, D-33098 Paderborn, Germany, {hannig, teich}@date.upb.de, URL: http://www-date.upb.de

**Abstract.** In this paper, we present a first approach for array-level energy estimation during high-level synthesis when mapping piecewise regular algorithms onto massively parallel full size processor arrays. Innately, piecewise regular algorithms have some power consumption friendly properties, e.g., they may be mapped onto processor arrays with only local interconnect and memory. In addition to these properties, we show that the chosen mapping has a significant influence on the power consumption. Our energy estimation approach identifies regions with decreased switching activity of functional units' input operands. For these regions with reduced activity, a lower power consumption can be directly obtained from a generated table based model. Experimental results fortify the accuracy and efficiency of our methodology.

### 1 Introduction

Nowadays, low power has become an important design criterion last but not least due to all the mobile phones and portable computers. These devices have to handle increasingly computational-intensive algorithms like video processing (MPEG4) or other digital signal processing tasks (3G), but on the other hand they are limited in their power budget. The next generation of ULSI chips will allow to implement arrays of hundreds 32-bit micro-processors and more on a single die. Hence, parallelization techniques and compilers will be of utmost importance in order to map computational-intensive algorithms efficiently to these processor arrays.

In this context, our paper deals with the specific problem of estimating the power consumption when mapping a certain class of loop-specified computations called *piecewise regular algorithms* [24] onto a dedicated processor array. This work can be classified to the area of loop parallelization in the polytope model [8,15].

The rest of the paper is structured as follows. In Section 2, a brief survey of previous work on low power is presented. Section 3 introduces the class of

<sup>\*</sup> Supported in part by the German Science Foundation (DFG) Project SFB 376 "Massively Parallel Computation".

algorithms we are dealing with. In Section 4, we examine the power consumption of functional units in dependence on their input activity. Afterwards, an energy estimation methodology when mapping regular algorithms to processor arrays is described. The methodology and some results are discussed in Section 5. Future extensions and concluding remarks are presented in Section 6.

### 2 Related Work

A lot of previous work in the area of low power design during high-level synthesis has dealt with the issue of power estimation. Various methodologies for generating accurate models for datapath power consumption were presented.

In general these power estimation techniques can be divided into simulative and non-simulative categories. The non-simulative method in [16] estimates the power consumption from an information theoretical point of view. In [14], the authors describe a strategy called Dual Bit Type (DBT) model where not only the random activity of the least significant bits, but also the correlated activity of the most significant bits is taken into account. The method in [10] proposes a modeling approach for functional units that are typically used in digital signal processing systems, such as adders, multipliers and delay elements. Thereby, a 4-dimensional table-based [9] macro model is used by the authors.

Also, some works [3] focused on transformations at the algorithmic and the architectural level to obtain low power designs. In [2], transformations for nested loop programs are discussed. In [4, 18, 19, 21], several scheduling and binding techniques for low power are studied. Some energy estimations for processor arrays with hierarchical memory structures are made in [6].

However, to the best of our knowledge, our work presented here is the first which considers the relationship between space-time mappings of computation intensive algorithms and energy consumption. Here, we specify a powerconsumption model used in the methodology described afterwards for energy estimation of piecewise regular processor arrays.

### 3 Notation and Background

#### 3.1 Algorithms

The class of algorithms we are dealing with in this paper is a class of recurrence equations defined as follows:

**Definition 1.** (Piecewise Regular Algorithm). A piecewise regular algorithm contains N quantified equations

$$S_1[I],\ldots,S_i[I],\ldots,S_N[I]$$

Each equation  $S_i[I]$  is of the form

$$x_i[I] = f_i(\ldots, x_j[I - d_{ji}], \ldots)$$

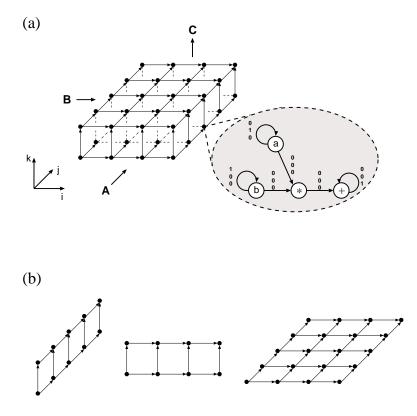

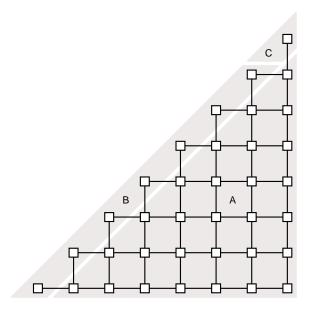

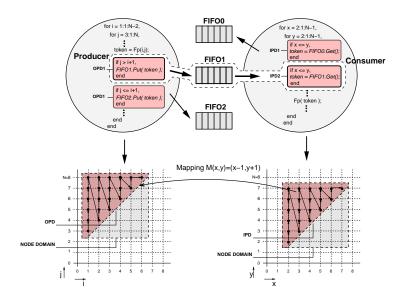

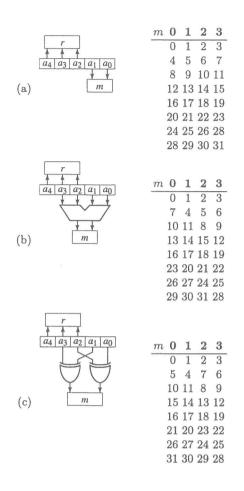

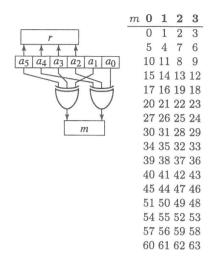

**Fig. 1.** In (a), an index space and the reduced dependence graph is shown. Some possible mappings are depicted in (b).

where  $I \in \mathcal{I}_i \subseteq \mathbb{Z}^n$ ,  $x_i[I]$  are indexed variables,  $f_i$  are arbitrary functions,  $d_{ji} \in \mathbb{Z}^n$  are constant data dependence vectors, and ... denote similar arguments.

The domains  $\mathcal{I}_i$  are called index spaces, and in our case defined as follows:

**Definition 2.** (Linearly Bounded Lattice). A linearly bounded lattice denotes an index space of the form

$$\mathcal{I} = \{ I \in \mathbb{Z}^n \mid I = M\kappa + c \land A\kappa \ge b \}$$

where  $\kappa \in \mathbb{Z}^l$ ,  $M \in \mathbb{Z}^{n \times l}$ ,  $c \in \mathbb{Z}^n$ ,  $A \in \mathbb{Z}^{m \times l}$  and  $b \in \mathbb{Z}^m$ . { $\kappa \in \mathbb{Z}^l \mid A\kappa \ge b$ } defines an integral convex polyhedron or in case of boundedness a polytope in  $\mathbb{Z}^l$ . This set is affinely mapped onto iteration vectors I using an affine transformation  $(I = M\kappa + c)$ .

Throughout the paper, we assume that the matrix M is square and invertible. Then, each vector  $\kappa$  is uniquely mapped to an index point I. Furthermore, we require that the index space is bounded.

For illustration purposes throughout the paper, the following example is used.

*Example 1.* The well known matrix multiplication algorithm computes the product  $C = A \cdot B$  of two matrices  $A \in \mathbb{R}^{N_1 \times N_3}$  and  $B \in \mathbb{R}^{N_3 \times N_2}$  and is defined as follows

$$c_{ij} = \sum_{k=1}^{N_3} a_{ik} b_{kj} \quad \forall \ 1 \le i \le N_1 \ \land \ 1 \le j \le N_2$$

A corresponding piecewise regular algorithm is given by

$\begin{array}{ll} \mbox{input operations} \\ a[i,0,k] \leftarrow a_{ik} & 1 \leq i \leq N_1 \ \land \ 1 \leq k \leq N_3 \\ b[0,j,k] \leftarrow b_{kj} & 1 \leq j \leq N_2 \ \land \ 1 \leq k \leq N_3 \\ c[i,j,0] \leftarrow 0 & 1 \leq i \leq N_1 \ \land \ 1 \leq j \leq N_2 \\ \mbox{computations} & 1 \leq i \leq N_1 \ \land \ 1 \leq j \leq N_2 \\ \mbox{computations} & 1 \leq i \leq N_1 \ \land \ 1 \leq j \leq N_2 \\ \mbox{computations} & 1 \leq i \leq N_1 \ \land \ 1 \leq j \leq N_2 \\ \mbox{computations} & 1 \leq i \leq N_1 \ \land \ 1 \leq j \leq N_2 \\ \mbox{computations} & 1 \leq i \leq N_1 \ \land \ 1 \leq j \leq N_2 \\ \mbox{computations} & 1 \leq i \leq N_1 \ \land \ 1 \leq j \leq N_2 \\ \mbox{c}[i,j,k] \leftarrow b[i-1,j,k] & \forall (i \ j \ k)^T = I \in \mathcal{I} \\ \mbox{c}[i,j,k] \leftarrow c[i,j,k-1] + z[i,j,k] & \forall (i \ j \ k)^T = I \in \mathcal{I} \\ \mbox{output operations} & 1 \leq i \leq N_1 \ \land \ 1 \leq j \leq N_2 \\ \end{array}$

The data dependence vectors are  $d_{aa} = (0\ 1\ 0)^{\mathrm{T}}, d_{bb} = (1\ 0\ 0)^{\mathrm{T}}, d_{cc} = (0\ 0\ 1)^{\mathrm{T}}, d_{az} = (0\ 0\ 0)^{\mathrm{T}}, d_{bz} = (0\ 0\ 0)^{\mathrm{T}}$ , and  $d_{zc} = (0\ 0\ 0)^{\mathrm{T}}$ . The index space is given by

$\mathcal{I} = \{ I = (i \ j \ k)^{\mathrm{T}} \in \mathbb{Z}^3 \mid 1 \le i \le N_1 \ \land \ 1 \le j \le N_2 \ \land \ 1 \le k \le N_3 \}.$

Computations of piecewise regular algorithms may be represented by a *dependence graph* (DG). The dependence graph of the algorithm of Example 1 is shown in Fig. 1 (a). The dependence graph expresses the partial order between the operations. Each variable of the algorithm is represented at every index point  $I \in \mathcal{I}$  by one node. The edges correspond to the data dependencies of the algorithm. They are *regular* throughout the algorithm, i.e., a[i, j, k] is directly dependent on a[i, j - 1, k]. The dependence graph specifies implicitly all legal execution orderings of operations: if there is a directed path in the dependence graph from one node a[J] to a node z[K] where  $J, K \in \mathcal{I}$ , then the computation of a[J] must precede the computation of z[K].

Henceforth, and without loss of generality<sup>1</sup>, we assume that all indexed variables are embedded in a common index space  $\mathcal{I}$ . Then, the corresponding dependence graphs can be represented in a reduced form.

**Definition 3.** (Reduced Dependence Graph). A reduced dependence graph (RDG) G = (V, E, D) of dimension n is a network where V is a set of nodes and  $E \subseteq V \times V$  is a set of edges. To each edge  $e = (v_i, v_j)$  there is associated a dependence vector  $d_{ij} \in D \subset \mathbb{Z}^n$ .

The RDG of the matrix multiplication algorithm is shown in Fig. 1 (a). Each node v in the graph corresponds to one equation in the section computations of the algorithm.

<sup>&</sup>lt;sup>1</sup> All described methods can also be applied for each quantification individually.

#### 3.2 Space-Time Mapping

Linear transformations as in Eq. (1), are used as space-time mappings [12, 17] in order to assign a processor index  $p \in \mathbb{Z}^{n-1}$  (space) and a sequencing index  $t \in \mathbb{Z}$ (time) to index vectors  $I \in \mathcal{I}$ .

$$\begin{pmatrix} p \\ t \end{pmatrix} = TI = \begin{pmatrix} Q \\ \lambda \end{pmatrix} I \tag{1}$$

In Eq. (1),  $Q \in \mathbb{Z}^{(n-1) \times n}$  and  $\lambda \in \mathbb{Z}^{1 \times n}$ . The main reasons for using linear allocation and scheduling functions is that the data flow between PEs is local and regular which is essential for low power VLSI implementations. The interpretation of such a linear transformation is as follows: The set of operations defined at index points  $\lambda \cdot I = \text{const.}$  are scheduled at the same time step. The index space of allocated processing elements (*processor space*) is denoted by Q and is given by the set  $Q = \{p \mid p = Q \cdot I \land I \in \mathcal{I}\}$ . This set can also be obtained by choosing a projection of the dependence graph along a vector  $u \in \mathbb{Z}^n$ , i.e., any coprime<sup>2</sup> vector u satisfying  $Q \cdot u = 0$  [12] describes the allocation equivalently.

Allocation and scheduling must satisfy that no data dependencies in the DG are violated. This is ensured by the following *causality constraint*

$$\lambda \cdot d_{ij} \ge 0 \quad \forall (v_i, v_j) \in E.$$

<sup>(2)</sup>

A sufficient condition for guaranteeing that no two or more index points are assigned to a processing element at the same time step is given by

$$\operatorname{rank}\begin{pmatrix}Q\\\lambda\end{pmatrix} = n.$$

(3)

Using the projection vector u satisfying  $Q \cdot u = 0$ , this condition is equivalent to  $\lambda \cdot u \neq 0$  [24].

**Definition 4.** (Iteration Interval) [26]. The iteration interval  $\pi$  of an allocated and scheduled piecewise regular algorithm is the number of time instances between the evaluation of two successive instances of a variable within one processing element.

**Definition 5.** (Block Pipelining Period) [13]. The block pipelining period of an allocated and scheduled piecewise regular algorithm is the time interval between the initiations of two successive problem instances and is denoted by  $\beta$ .

Lets consider the matrix multiplication algorithm introduced in Example 1 as a problem instance. The whole matrices A and B have to read into the processor array before the next pair can be read, the time between these input operations is the block pipelining period  $\beta$ . Let  $\lambda$  be the schedule vector. Then, the block pipelining period  $\beta$  may be computed as follows,

$$\beta = \max_{I_1 \in \mathcal{I}} \left\{ \lambda \cdot I_1 \right\} \ - \ \min_{I_2 \in \mathcal{I}} \left\{ \lambda \cdot I_2 \right\} \ = \max_{I_1, I_2 \in \mathcal{I}} \left\{ \lambda (I_1 - I_2) \right\}.$$

<sup>&</sup>lt;sup>2</sup> A vector x is said to be *coprime* if the absolute value of the greatest value of the greatest common divisor of its elements is one.

## 4 Power Modeling and Energy Estimation

In digital CMOS circuits, the dominant source of power consumption is switching power [22]. The average power consumed by a CMOS gate can be computed using the following equation,

$$P_{sw} = \frac{1}{2} C_L V_{dd}^2 N f,$$

where  $C_L$  is the gate output load capacitance,  $V_{dd}$  is the supply voltage, f is the clock frequency, and N is the average or expected number of output transitions per clock cycle.

Due to the influence of the switching activity on the power consumption, our main idea is to exploit the fact that power consumption is drastically reduced when some inputs of a functional unit remain unchanged for n > 1 clock cycles.

Here, we want to discuss the impact of the space-time mapping on the power and energy consumption respectively of the resulting processor array. Our approach identifies regions with decreased switching activity of functional units' input operands and take these power savings into account. An estimation methodology is presented in the following. This methodology estimates for a given piecewise regular algorithm and a space-time mapping T the average power consumption of the entire array.

Briefly described this methodology can be subdivided into two hierarchical estimation steps,

- PE-level power estimation,

- array-level power estimation.

#### 4.1 PE-level Power Estimation

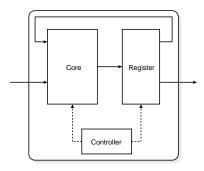

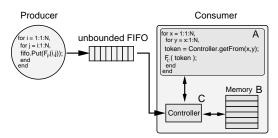

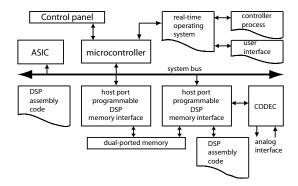

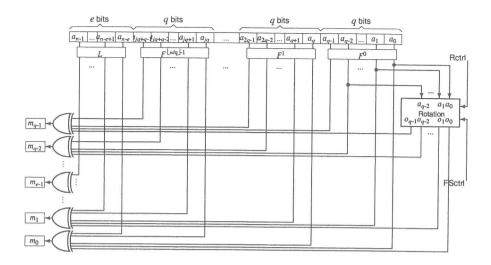

A sketch of a typical processor element's internal structure is shown in Fig. 2. It consists of a core part where all the functional units are located, a controller, and some delay registers. In the final paper version, we quantify the percentages

Fig. 2. Schematically internal structure of one processor element.

of power consumption for the functional units  $P_{\rm FU}$ , the control structures  $P_{\rm Ctrl}$ , and the registers  $P_{\rm Rg}$  and these parts' proportion of the overall power consumption of one processing element. Then the power consumption of one PE can be approximated as follows,  $P_{\rm FU}(\lambda, u) = P_{\rm FU}(u) + P_{\rm Ctrl}(\lambda) + P_{\rm Rg}(\lambda)$ .

For characterization of the functional units (adders, multipliers, etc.), standard register-transfer level power estimation tools from Synopsys [23] are used.

| n          | $P_{avg,i}$   | A P           | avg, B        | $P_{avg}$ | $_{g,C}$ | $P_{avg}$ | $_{I},D$ |

|------------|---------------|---------------|---------------|-----------|----------|-----------|----------|

| 1          | 26.97 $\mu$   | ıW 204        | $1.2 \ \mu W$ | 212.0     | $\mu W$  | 319.6     | $\mu W$  |

| 2          | 22.33 $\mu$   | ιW 155        | $6.4 \ \mu W$ | 164.0     | $\mu W$  | 225.0     | $\mu W$  |

| 3          | $18.82 \mu$   | ιW 138        | $8.6 \ \mu W$ | 145.6     | $\mu W$  | 190.1     | $\mu W$  |

| 4          | $16.99 \ \mu$ | ιW 129        | $0.6 \ \mu W$ | 137.3     | $\mu W$  | 175.1     | $\mu W$  |

| 5          | $16.31 \ \mu$ | $\iota W 125$ | $6.4 \ \mu W$ | 133.8     | $\mu W$  | 164.3     | $\mu W$  |

| 6          | $15.68 \ \mu$ | ιW 120        | $0.5 \ \mu W$ | 128.4     | $\mu W$  | 159.4     | $\mu W$  |

| 7          | 15.48 $\mu$   | $\iota W 119$ | $0.5 \ \mu W$ | 125.2     | $\mu W$  | 153.3     | $\mu W$  |

| 8          | 15.29 $\mu$   | ιW 116        | $6.8 \ \mu W$ | 124.4     | $\mu W$  | 151.6     | $\mu W$  |

| 9          | 15.09 $\mu$   | $\iota W 116$ | $6.3 \ \mu W$ | 123.7     | $\mu W$  | 147.8     | $\mu W$  |

| 10         | 14.89 $\mu$   | $\iota W 115$ | $5.5 \ \mu W$ | 122.7     | $\mu W$  | 145.8     | $\mu W$  |

| $\infty_0$ | $8.49 \mu$    | $\iota W$     | -             | -         |          | _         |          |

|            |               |               |               |           |          |           |          |

Table 1. Average power consumption of different functional units.

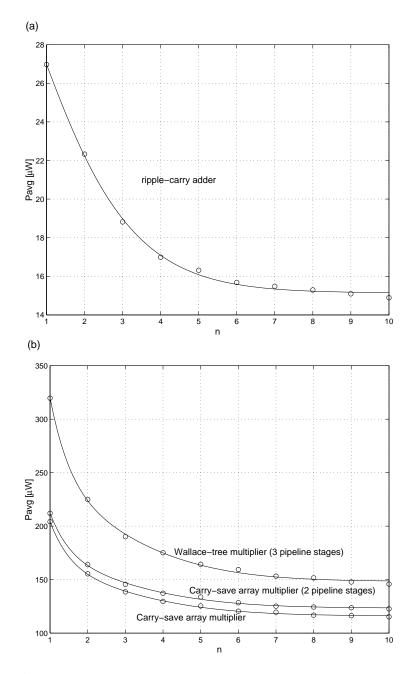

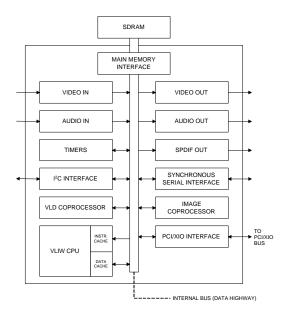

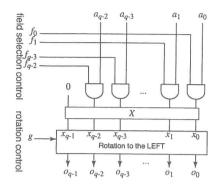

In Table 1, the average power consumption of some 16-bit functional units are listed (A = ripple-carry adder, B = carry-save array multiplier, C = carrysave array multiplier with two pipeline stages, D = Wallace-tree multiplier with three pipeline stages). Each functional unit has two input operands. The value of one operand is assumed to be constant for n clock cycles; the other can change randomly in every clock cycle. These values are visualized in Fig. 3 (a) for the 16-bit ripple-carry adder and Fig. 3 (b) for the multipliers respectively. The curves are derived by regression, where the function is of type  $P = a_0 + a_1 e^{-n} + a_2 n e^{-n} + a_3 n^2 e^{-n}$ . The regression is good enough to have errors less than 2%. Since we are only interested in integer multiples of the clock cycle for n, the derived models may be stored in a table without too much effort.

#### 4.2 Array-level Power Estimation

Based on the class of piecewise regular algorithms, we want to estimate the power consumption for a given space-time mapping  $T = (Q \lambda)^{\mathrm{T}}$ . It is obvious that the cost (number of processor elements) and the latency is influenced by the space-time mapping. In earlier work [11], we described how to determine the cost and the latency as a measure for performance. Here, we just briefly outline the main ideas. If we assume that processor arrays are resource-dominant, we are able to approximate the cost as being proportional to the processor count. *Ehrhart polynomials* [5, 7] may be evaluated to count the number of points (processor elements, #PE) in the projected index space.

Fig. 3. Average power consumption of some 16-bit functional units when one operand is constant for n clock cycles and the other can change randomly in every clock cycle.

The latency is determined by solving a minimization problem which may be formulated as a mixed integer linear program (MILP) [25, 26]. Also, modified low power scheduling and binding techniques like in [19, 21] can be applied to compute a suited schedule.

Here, we want to discuss the impact of the space-time mapping on the power and energy consumption respectively of the resulting processor array. Our approach identifies regions with decreased switching activity of functional units' input operands and take these power savings into account. An estimation algorithm is presented on the following pages. The algorithm estimates for a given RDG G, an index space  $\mathcal{I}$ , a space-time mapping T, the number of processor elements #PE, and the block pipelining period  $\beta$  the average power consumption  $P_{array}$  of the entire array. The processor count #PE and the block pipelining period  $\beta$  of the array may be computed as described earlier in this paper.

Once, the average power consumption  $P_{\text{array}}$  of the entire processor array is estimated, the energy consumption per problem instance is computed as follows,

$$E = \beta \cdot P_{\text{array}}.$$

Without loss of generality, we assume in the following that the iteration period  $\pi$  is one and that each RDG node is mapped onto a dedicated resource. Our estimation algorithm can be subdivided into two phases. In the first phase, the worst case power consumption is computed, i.e., when the switching activity of all functional units' input operands is highest. Therefore, the power consumption  $P_{\rm PE}$  of one processor element is determined by summation of the power consumption  $P_{v_i}(1)$  of all of its FUs

$$P_{\rm PE} = \sum_{\forall v_i \in V} P_{v_i}(1).$$

The one in the term  $P_{v_i}(1)$  denotes that operands can change in every clock cycle.

# POWER ESTIMATION

RDG  $G, \mathcal{I}, T = \begin{pmatrix} Q \\ \lambda \end{pmatrix}, \#PE, \text{ and } \beta$ IN: 1 2 OUT:  $P_{\mathrm{arrav}}$ 3 BEGIN 4  $P_{\rm PE} \leftarrow 0$ FOR all nodes  $v \in G$  DO 5  $P_{v,1} \leftarrow \mathsf{lookUpPower}(v,1)$ 6  $P_{\text{PE}} \leftarrow P_{\text{PE}} + P_{v,1}$ 7 8 **ENDFOR**  $P_{\text{array}} \leftarrow \# PE \cdot P_{\text{PE}}$ 9 FOR all edges  $e \in G$  DO 10 11 d is dependence vector of edge e12 node  $v \leftarrow \mathsf{source}(e)$ 13 node  $w \leftarrow \mathsf{target}(e)$

```

IF (v = w) THEN

14

IF (S_v \text{ is propagation equation}) THEN

15

IF (Q \cdot d = \mathbf{0}) THEN

16

FOR all adjacent edges e' of v

17

d' is dependence vector of edge e'

18

IF (d' = 0) THEN

19

w \leftarrow \mathsf{target}(e')

20

P_{w,1} \leftarrow \mathsf{lookUpPower}(w,1)

21

P_{w,\beta}^{w,n} \leftarrow \mathsf{lookUpPower}(w,\beta)

P_{\mathrm{array}} \leftarrow P_{\mathrm{array}} - \#PE \cdot (P_{w,1} - P_{w,\beta})

22

23

24

FNDIF

ENDFOR

25

ENDIF

26

ELSE

27

28

(k, m) \leftarrow \mathsf{getOperandFixedCycles}(T, v)

P_{w,1} \leftarrow \mathsf{lookUpPower}(w,1)

29

\begin{array}{l} P_{w,k} \leftarrow \mathsf{lookUpPower}(w,k) \\ P_{\mathrm{array}} \leftarrow P_{\mathrm{array}} - m \cdot (P_{w,1} - P_{w,k}) \end{array}

30

31

32

ENDIF

ENDIF

33

ENDFOR

34

END

35

```

Subsequently, the power consumption of the entire array is obtained by extrapolation of this value. In the second algorithm phase array regions with lower switching activity are detected. Therefore, the whole reduced dependence graph is traversed to examine self-loops<sup>3</sup>. These self-loops correspond to inputs of a processor element. If these inputs remain unchanged for more than one period, the switching activity is decreased and consequently also the power. It remains to determine for how long inputs are constant and how many processor elements are affected. Two cases can be differentiated:

- 1. Propagation equations mapped onto itself. Propagation equations are only used to distribute data from one processor to another. Due to the regularity and locality of the considered processor arrays, they occur very commonly. If such a propagation equation is mapped onto itself  $(Q \cdot d = 0)$  no data transport is needed, i.e., the data remains in one processor element unchanged for  $\beta$  cycles until the next problem instance is fed into the array. Thus, the switching activity of all adjacent nodes  $v_i$  (functional units) in the same processor element is reduced. Therefore, the estimation of the average power consumption is decreased by  $P_{v_i}(1) - P_{v_i}(\beta)$ . As a propagation equation has global influence the activity is reduced in every processor element (#PE).

- 2. Other self-loops. These are the remaining inputs which may be constant for k clock cycles. The number of processor elements with these constant

10

$<sup>^{3}</sup>$  A self-loop is an edge where source and target node are the same.

inputs is denoted by m. Let  $\mathcal{I}_{in_1}$  be the input index space of variable  $in_i$ . Transforming this index space by Q and counting the number of points in the transformed space, gives m.

$$m = \left| \left\{ I \in \mathbb{Z}^{n-1} | I = Q \cdot I_{in_1} \land I_{in_1} \in \mathcal{I}_{in_1} \right\} \right|$$

This counting problem is similar to the earlier described one and can also solved by using Ehrhart polynomials. Once k and m are determined, the overall estimated power consumption can be reduced by  $m \cdot (P_{in_1}(1) - P_{in_1}(k))$ .

In the next section the overall algorithm is explained by means of discussing some results.

#### 5 Results

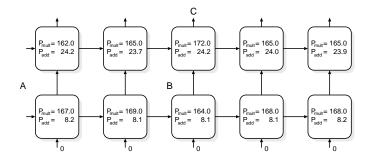

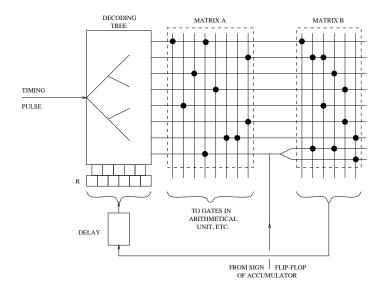

Reconsider the introductory Example 1. As an allocation we choose for the addition a 16-bit ripple-carry adder and for the multiplication a three-stage pipelined Wallace-tree multiplier. The input operations a and b are mapped each to one resource of type *input*. The execution times of these operations are zero. This is equivalent to a multi-cast without delay to a set of processors. Furthermore, let  $u = (1 \ 0 \ 0)^{T}$  be the chosen projection vector. Then, after scheduling and cost calculus, we obtain the schedule vector  $\lambda = (1 \ 0 \ 1)$  and as cost  $\#PE = N_2 \cdot N_3$ . Now, with this information we are able to estimate the power consumption by applying the proposed algorithm. First, the worst case power consumption is determined, i.e., the switching activity of functional units' when input operands change each both each cycle. Second, in the main part of the algorithm, two types of equations with lower input activity are detected and the overall power consumption is adapted.

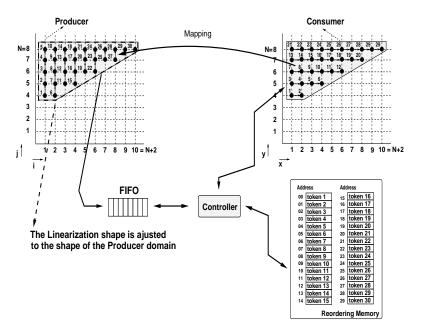

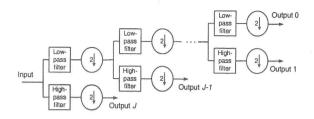

**Fig. 4.** Processor array for  $u = (1 \ 0 \ 0)^{\mathrm{T}}$ ,  $N_1 = 4$ ,  $N_2 = 5$ , and  $N_3 = 2$ .

The processor array for a projection in direction  $u = (1 \ 0 \ 0)^{\mathrm{T}}$  is shown in Fig. 4. Due to this projection, the variable b is mapped onto itself. From this it

follows that one operand of the multiplication remains unchanged for some time. At the beginning of a computation, the whole matrix B is input simultaneously to the array, whereas the matrix A is fed sequentially row by row from the left side into the array. Since the matrix A has  $N_1$  rows, one operand of the multiplier is fixed for  $\beta = N_1$  clock cycles which significantly reduces the power consumption in the multipliers by 45% (see Table 1). On account of the design regularity the power savings can multiplied by #PE (line 23 of the algorithm). The second point where less power is consumed is the constant input variable c. One input of the adders in the lower row of the processor array is permanently zero. This partial areas with reduced power consumption in the array are determined by the function getOperandFixedCycles. In addition to the time ( $k = \infty$ ) where one input remains unchanged, the number  $m = N_2$  of processors with reduced switching activity is returned.

Table 2. Average power and energy consumption of different mappings.

| u                                                                                                                 | $P_{\rm sim}$ | $P_{\rm ext}$ | $\mathrm{Err}_{\mathrm{ext}}$                 | $P_{\rm est}$ | $\mathrm{Err}_{\mathrm{est}}$ | $E_{\rm sim}$ | $E_{\rm est}$ |

|-------------------------------------------------------------------------------------------------------------------|---------------|---------------|-----------------------------------------------|---------------|-------------------------------|---------------|---------------|

|                                                                                                                   | $[\mu W]$     | $[\mu W]$     | $\operatorname{Err}_{\operatorname{ext}}$ [%] | $[\mu W]$     | [%]                           | [pJ]          | [pJ]          |

| $ \begin{array}{c} (1 \ 0 \ 0)^{\mathrm{T}} \\ (0 \ 1 \ 0)^{\mathrm{T}} \\ (0 \ 0 \ 1)^{\mathrm{T}} \end{array} $ | 2020          | 3466          | 71.6                                          | 1928          | -4.6                          | 80.8          | 77.1          |

| $(0\ 1\ 0)^{\mathrm{T}}$                                                                                          | 1530          | 2773          | 81.2                                          | 1456          | -4.8                          | 76.5          | 72.8          |

| $(0 \ 0 \ 1)^{\mathrm{T}}$                                                                                        | 7260          | 6931          | -4.5                                          | 6931          | -4.5                          | 145.2         | 138.6         |

In Table 2, the power consumption for different projection vectors is shown, where for illustration purposes, the upper boundaries of the index space are set to  $N_1 = 4$ ,  $N_2 = 5$ , and  $N_3 = 2$ . In the table,  $P_{\rm sim}$  is the exact value obtained by simulation of the entire array. The worst case extrapolation (line 4–9 in the algorithm) is denoted by  $P_{\rm ext}$ . The power consumption of our estimation algorithm is labeled with  $P_{\rm est}$ . Whereas the simple extrapolation method has errors up to 81%, our approach is very accurate with errors less than 5%.

Furthermore, the energy values per matrix multiplication in the table show the significant influence of the chosen space-timing mapping. Different mappings can lead to energy consumptions which differ up to a factor of two.

# 6 Conclusions and Future Work

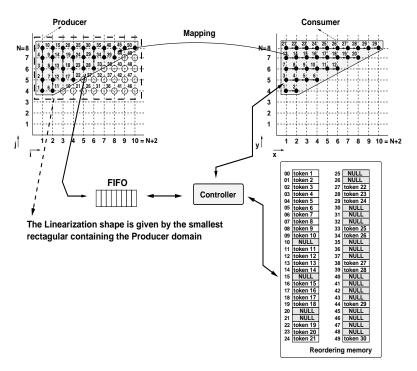

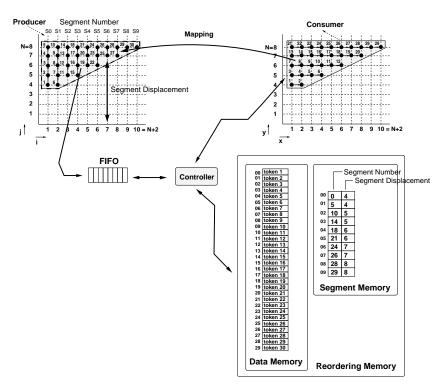

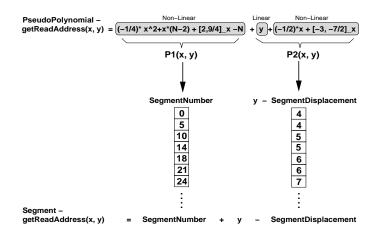

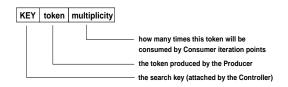

A first study of a matrix multiplication algorithm has shown the great impact of a chosen mapping to the average energy consumption of the resulting array and the accuracy (errors < 5%) of our estimation approach when comparing it with RTL power estimation tools from Synopsys [23].