# NBTI-Aware Nanoscaled Circuit Delay Assessment and Mitigation

Seyab Khan Said Hamdioui

Delft University of Technology, Computer Engineering Laboratory Mekelweg 4, 2628 CD, Delft, The Netherlands {M.S.K.Seyab, S.Hamdioui}@tudelft.nl

Abstract. As semiconductor manufacturing entered into nanoscale era, performance degradation due to Negative Bias Temperature Instability (NBTI) became one of the major threats to circuits reliability. In this paper, we present a model and analysis of NBTI impact on circuit delays. First, we model NBTI impact on gate intrinsic delay and output transition delay. The insights of our models reveal that NBTI causes additional 6.7% intrinsic and 3% output transition delays to a gate. Second, we analyze delays in the gates at the inputs and outputs of a circuit. Simulation results from several benchmark circuits show that under a given condition identical gates at the circuit outputs suffer from 3.33% additional delays as compared to gates at the circuit inputs. Third, we analyze different techniques at transistor and circuit levels to mitigate NBTI. From the analysis of mobility increment, gate oversizing, temperature reduction, and supply voltage increment techniques, we conclude that temperature reduction is the most effective to mitigate NBTI.

**Keywords**: Negative Bias Temperature Instability, Intrinsic delay, Frontend delay, NBTI mitigation.

#### 1 Introduction

With the relentless pursuit for smaller CMOS process technologies, failures due to aging mechanisms have become a limiting factor for transistor/circuit reliability [1]. Industrial data reveal that as oxide thickness reached 4nm, Negative Bias Temperature Instability (NBTI) has become one of the most significant aging mechanisms [2, 3]. NBTI degrades performance of a PMOS transistor under a negative gate stress. The effects of NBTI on a PMOS transistor include: (a) threshold voltage increment, (b) drain current degradation, and (c) delay increment [4, 5]. These effects show off themselves at circuit level by increasing circuit delays, or in extreme cases causing circuit timing/functional failures.

The delay due to NBTI is a growing problem for nanoscaled gates and circuits. The amount of delay depends on variables such as temperature, voltage and switching activities of transistors. Therefore, an accurate estimation of the delay is a tremendous challenge. In the work done so far, the delay due to NBTI is modeled in two distinct ways:

- Gate delay modeling [6–8]: in which NBTI impact on delays of individual gates are calculated. The delay models are generally derived analytically or constructed from circuit simulations.

- Circuit delay modeling [7, 10]: in which gate delays of *individual isolated gate* are lumped to get circuit delay models.

There are few research works on NBTI induced delay modeling at gate level [6–8]. Paul et al. in [6] initiated NBTI delay modeling and analysis. However,

the analysis is pessimistic as they consider only the worst case, i.e. static stress conditions. In [7] NBTI impact on gate delay have been analyzed under dynamic stress conditions. However, the analysis focuses on the NBTI induced delay of the isolated gate and does not consider its impact on the gate output transition that affects input transition to the next gates in the circuit. In [9] it has been argued that variations in input transition can cause up to 31% additional delay to a gate. Therefore, NBTI impact on the output transition must be incorporated in the gate delay models.

Apart from the above mentioned initial works at gate level delay modeling, circuit level delay modeling due to NBTI is still at its infancy stage and demands more attention from the research community. The circuit delay models proposed so far [7,10] suffer from inaccuracy as they only consider NBTI impact on intrinsic delays of the gates. These models ignore the impact on the gate input transition. NBTI affects the input transition of a gate due to degradation of the previous gates in a circuit. Therefore, an accurate gate level NBTI model suitable for circuit delay assessment is needed.

In this paper, we present a novel NBTI aware circuit delay model, which embodies transistor level NBTI induced degradation, gate level delay and circuit level delay. Thereafter, we analyze different techniques to mitigate NBTI at transistor and circuit levels. The contributions of this paper are the following.

- It models gate the intrinsic delay increment due to NBTI induced threshold voltage shift. Magnitude of the delay is a function of supply voltage, temperature and switching activity of the gate.

- It models NBTI impact on the output transition of a gate. Furthermore, it models the impact of the input transition on the gate delay.

- It presents NBTI induced circuit delay modeling and analysis; magnitude of the delay depends on the switching activities, types of the gates and nature of the correlation among the gates.

- It analyzes different techniques to mitigate NBTI at transistor and circuit levels. The analysis reveals that at circuit level, temperature reduction is the most suitable technique to mitigate NBTI.

The rest of the paper is organized as follows. Section 2 describes NBTI mechanism under dynamic stress. Section 3 proposes an NBTI induced gate delay model; the model considers NBTI impact on intrinsic delay and output transition of a gate. Section 4 extends the gate delay model to model circuit delay due to NBTI. Section 5 discusses simulation results of several benchmark circuits. Section 6 analyzes different techniques to mitigate NBTI. Finally, Section 7 concludes the paper.

# 2 NBTI Mechanism

The Reaction-Diffusion (R-D) model [11] has been widely used to explain NBTI mechanism of PMOS transistors. The model can be divided in two phases i.e. stress and recovery phases.

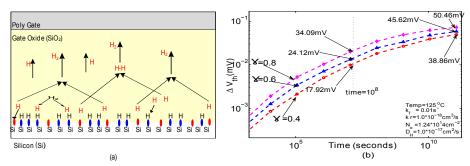

Stress Phase: According to the model, during stress phase ( $V_{gs}$ =- $V_{dd}$ ), NBTI degradation originates from Silicon Hydrogen bonds ( $\equiv$ Si-H) breaking at Silicon-Silicon dioxide (Si-SiO<sub>2</sub>) interface of a PMOS transistor as shown in Fig.1(a). The broken Silicon bonds ( $\equiv$ Si-) act as interface traps that cause NBTI degradation. The number of interface traps ( $N_{IT}$ ) depends on  $\equiv$ Si-H bond breaking

**Fig. 1.** (a) Schematic view of NBTI mechanism (b)  $V_{th}$  with time for various  $\gamma$  values rate  $(k_f)$  and  $\equiv$ Si- bond recovery rate  $(k_r)$ . The  $N_{IT}$  generation rate is given by [4]:

$$\frac{dN_{IT}}{dt} = k_f(N_o - N_{IT}) - k_r N_{IT} N_H^0 \tag{1}$$

where  $N_o$  and  $N_{\rm H}^0$  denote initial bond density and atomic Hydrogen density at the Si-SiO<sub>2</sub> interface respectively. The H atoms released from  $\equiv$ Si-H bond breaking contribute to three sub-processes including: (a) diffusion towards the gate, (b) combination with other H atoms to produce H<sub>2</sub>, or (c) recovery of the broken bonds. Similar to H atoms, H<sub>2</sub> molecules participate two sub-processes: (a) diffusion towards gate, and (b) dissociation to produce H atoms. All these sub-processes are schematically shown in Fig.1(a). The N<sub>IT</sub> generation rate is limited by the sub-processes related to H and H<sub>2</sub> and is given by [4]:

$$\frac{dN_H}{dt} = D_H \frac{d^2 N_H}{dx^2} - k_H N_H^2 + k_{H_2} N_{H_2} \tag{2}$$

$$\frac{dN_{H2}}{dt} = D_{H2}\frac{d^2N_{H2}}{dx^2} + \frac{1}{2}k_H N_H^2 - k_{H2}N_{H2} \tag{3}$$

where  $N_H$  and  $N_{H_2}$  are densities,  $D_H$  and  $D_{H_2}$  are diffusion rates of H and H<sub>2</sub>, while  $k_H$  and  $k_{H_2}$  are interconversion rates of H and H<sub>2</sub> respectively.

Initially, the bond breaking and bond recovery sub-processes dominate at the  $Si-SiO_2$  interface; the diffusing entities in  $SiO_2$  layer are mainly atomic H. However, if the stress is maintained for longer time, most of the H atoms are converted to  $H_2$ , which in turn dominate the diffusion inside  $SiO_2$  layer. Under such conditions  $N_{IT}$  at time t is obtained by solving Eq.1 and Eq.3 [4]:

$$N_{IT}(t) = \left(\frac{k_f N_o}{k_r}\right)^{2/3} \left(\frac{k_H}{k_{H_2}}\right)^{1/3} (6D_{H_2}t)^{1/6} \tag{4}$$

**Recovery Phase:** Once the gate stress is removed (i.e.  $V_{gs}=V_{dd}$ ), the Si-H bond breaking at Si-SiO<sub>2</sub> interface no longer exists. Now the H and H<sub>2</sub> entities diffuse back and recover the interface traps. The recovered interface traps  $(N_{IT}^*)$  can be written as [4]:

$$N_{IT}* = N_{IT} \left( 1 - \sqrt{\frac{\xi \cdot t}{t + t_o}} \right) \tag{5}$$

where  $\xi$  is the diffusion dependent recovery constant,  $t_o$  is the cycle duration, and t is the recovery duration. The equation shows that  $N_{IT}*$  increases with t; and that at  $t=t_o$ , the recovered interface traps reach  $N_{IT}*=0.3\times N_{IT}$  for  $\xi=1$ .

Eq. 4 and Eq. 5 give the generated  $N_{\rm IT}$  and the recovered  $N_{\rm IT}*$  during stress

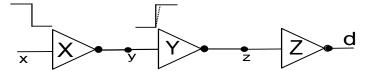

Fig. 2. An example circuit to illustrate NBTI impact on delays

and recovery phases respectively.  $N_{\rm IT}$  causes threshold voltage shift ( $\Delta V_{\rm th}$ ) of PMOS transistor, which can be written as:

$$\Delta V_{\rm th} = (1+m)\frac{q.N_{IT}}{C_{cr}} \tag{6}$$

where m, q, and  $C_{ox}$  represent hole mobility degradation, electron charge and oxide capacitance of the transistor respectively. During recovery phase,  $N_{IT}*$  presence means a reduction in  $N_{IT}$ . As a consequence,  $V_{th}$  shift will be reduced during the recovery phase.

The  $N_{IT}$  generated and the consequent  $\Delta V_{th}$  strongly depend on stress and recovery durations ratio  $(\gamma)$  of transistor in a gate. Fig.1(b) shows the  $\Delta V_{th}$  increment with time for different  $\gamma$  values. The figure shows that for a given  $\gamma$ , the  $\Delta V_{th}$  increases with the stress time and intends to saturate at longer stress time. In addition, the analysis of data in the figure reveal that  $\Delta V_{th}$  is linearly proportional to  $\gamma$  i.e.

$$\Delta V_{th} \propto \gamma$$

(7)

The relation is evident from the figure. For instance, at t=10<sup>8</sup>sec,  $\Delta V_{th}$  =17.92mV for  $\gamma$ =0.4,  $\Delta V_{th}$ =24.12mV for  $\gamma$ =0.6, and  $\Delta V_{th}$ =34.08mV for  $\gamma$ =0.8.

## 3 Proposed Gate Delay Model

Traditionally, the circuit delay due to NBTI is modeled in two phases: (a) the delay is modeled for an isolated gate, and (b) the isolated gate delays are added to get the circuit delay model [6, 10]. Clearly, the isolated gate delay model used is not accurate for circuit delay modeling since NBTI impact on gate delay in a circuit is not isolated. Instead, a gate delay model should account for the correlation between gates. The correlation exists because the output of one gate can be the input of the next gate in a circuit. NBTI increases the output transition of a gate to increases the input transition of the next gate and consequently its delay.

Fig.2 will be used to illustrate how  $\Delta V_{\rm th}$  of transistors in inverter Y and delay of inverter X influence the delay of inverter Y. Without considering aging, the delay of inverter Y is:

$$D = D_{th} + D_{st} + D_{cl} \tag{8}$$

where  $D_{th}$ ,  $D_{st}$  and  $D_{cl}$  are delays due to transistor's  $V_{th}$ , input Signal Transition and Capacitive Load of the gate respectively. For simplicity, we assume that third term is not affected by aging. The first and second terms degrade with aging. Suppose a falling transition is applied to the input of inverter X. By considering aging,  $\Delta V_{th}$  of transistors in X will increase output signal transition of the inverter X. As a consequence, this will cause an additional delay to the input signal transition of inverter Y. Obviously, aging will also cause an additional

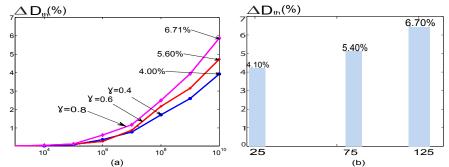

Fig. 3. (a)  $\Delta D_{th}$  with time under different  $\gamma$ , (b)  $\Delta D_{th}$  at different temperatures

delay due to  $\Delta V_{th}$  of transistors in Y. Hence, the total additional delay of inverter Y due to aging is:

$$\Delta D = \Delta D_{th} + \Delta D_{st} \tag{9}$$

where  $\Delta D_{th}$  and  $\Delta D_{st}$  are the delays due to  $\Delta V_{th}$  of transistors in Y and input delay respectively. Henceforth, we will refer to  $\Delta D_{th}$  as *intrinsic delay* and  $\Delta D_{st}$  as *Front-end delay*. It is important to note that for gates at the circuit inputs  $\Delta D_{st} = 0$  and  $\Delta D$  is only due to  $\Delta D_{th}$ .

In the rest of the section, we develop a gate delay model due to NBTI; The model takes both intrinsic delay model and the front-end delay into consideration.

Intrinsic Delay Model: The *n*th power law model [12] offers a simple yet accurate empirical formulation of the gate intrinsic delay  $(\Delta D_{th})$ . The  $\Delta D_{th}$  dependence on  $V_{th}$  is given by:

$$D_{th} = \frac{A}{(V_g - V_{th})^n}$$

where  $V_g$  is the gate voltage, n is a constant, and A is a technology dependent constant. The delay due to NBTI induced  $\Delta V_{\rm th}$  can be obtained by taking the differential of the above equation w.r.t.  $V_{\rm th}$ . Thereafter, applying Taylor series expansion and neglecting the higher order terms, the  $\Delta D_{\rm th}$  obtained is [6]:

$$\Delta D_{th} = \frac{n.\Delta V_{th}}{(V_{qs} - V_{th})} \tag{10}$$

In the above formulation, we introduce the variable  $\gamma$  of Eq.7. With this variable, we express the distribution of stress and recovery durations of the PMOS transistor in the gate. The stress/recovery distribution aware  $\Delta D_{\rm th}$  of the gate is given by:

$$\Delta D_{th} = \gamma \cdot \frac{n \cdot \Delta V_{th}}{(V_{as} - V_{th})} \tag{11}$$

The equation shows that the  $\Delta D_{th}$  is  $\gamma$  dependent. Additionally, it is important to point out here, that the  $\Delta D_{th}$  varies with temperature due to  $\Delta V_{th}$  dependence on temperature. The 45nm PMOS transistor model's [15] parameters are used to simulate  $\Delta D_{th}$  of a gate. Fig.3 shows the gate  $\Delta D_{th}$  for various  $\gamma$  and temperature values. The key insights from the figure are:

– NBTI induced  $\Delta D_{\rm th}$  increases with  $\gamma$  and follows the same trend as  $\Delta V_{\rm th}$  with  $\gamma$ . Figure 3(a) shows that the delay increment for  $\gamma$ =0.4 is 4.00%, while for  $\gamma$ =0.80 the increment approaches 6.71%.

– Temperature affects NBTI induced  $\Delta V_{th}$  and hence the gate  $\Delta D_{th}$ . Figure 3(b) shows the correlation between temperature and  $\Delta D_{th}$ . The simulation is done for  $\gamma$ =0.8; the results show that  $\Delta D_{th}$  is 4.10% at 25°C, and 6.70% at 125°C.

Front-end Delay Model: In order to complete our gate delay model suitable for circuit delay modeling, we model NBTI impact on output transition  $(\tau_o)$  of a gate. It has been argued that at constant load capacitance  $(C_L)$  and supply voltage  $(V_{dd})$ ,  $\tau_o$  of a gate depends on the saturation drain current  $(I_{dsat})$  of the active transistor (i.e.  $\tau_o = C_L V_{dd} / I_{dsat})$  [13]; the  $I_{dsat}$  is given by:

$$I_{dsat} = \mu.B.(V_{qs} - V_{th})^n \tag{12}$$

where  $\mu$  is the hole mobility and B is a technology dependent constant. NBTI increases  $V_{th}$ , reduces  $\mu$  that results in lower  $I_{dsat}$  and hence increase  $\tau_o$  of a gate. For an intermediate gate in a circuit, we assume that  $\tau_o$  of the gate is equivalent to the input transition  $(\tau_i)$  of the next gate (i.e.  $\tau_0 = \tau_i$ ). For a given value of velocity saturation index  $(\alpha)$  and voltage gain of the active transistors  $(\nu_t)$  in a gate, we model the gate delay as a function of  $\tau_i$  in accordance with [12]. Henceforth, we will call it front-end delay  $(D_{st})$ . After simplification, we conclude that the  $\Delta D_{st}$  increases with  $\tau_i$ , and can be written as:

$$D_{st} = \left(\frac{\alpha + \nu_t}{1 + \alpha}\right) \tau_i . \kappa \tag{13}$$

where  $\kappa$  is an indicator variable for delay propagation. If the input transition  $\tau_i$  will cause a transition at the gate output its value is 1, otherwise it is zero. The increase in  $\tau_i$  due to NBTI induced degradations of the previous gates and their impact on gate  $\Delta D_{\rm st}$  is achieved by solving Eq. 12 and Eq. 13. After simplification, the front-end delay is:

$$\Delta D_{st} = \left(\frac{\alpha + \nu_t}{1 + \alpha}\right) \Delta \tau_i \cdot \kappa \tag{14}$$

To illustrate the front-end delay model we consider the circuit in Fig.2. We assume that inverter X suffers from NBTI, and Y does not have intrinsic delay and its delay is only affected by input transition. The 45nm PMOS transistor model's [15] parameters are used to simulate NBTI impact, (a) on  $\tau_o$  of a inverter X, (b) on  $\tau_i$  of inverter Y, and (c) on  $\Delta D_{\rm st}$  of inverter Y. Fig.4(a) shows NBTI impact on the  $\tau_o$  of inverter X. The figure shows that  $\tau_o$  of inverter X increases with time due to NBTI.  $\tau_o$  increment of inverter X increases  $\tau_i$  inverter

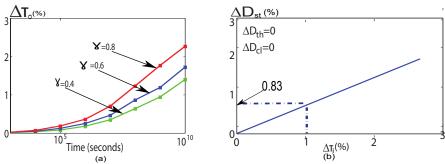

**Fig. 4.** (a)  $\Delta \tau_o$  under NBTI degradation at  $\gamma$ =0.4, 0.6 and 0.8(b)  $\Delta D_{st}$  variation with  $\Delta \tau_i$

Fig. 5. (a) Comparison of models with HSPICE simulation, (b)  $\Delta D$  of inverters and  $\Delta D_{\rm st}$  caused by the previous inverters

Y. Fig.4 (b) shows the percent  $\Delta D_{st}$  of Y against the percent  $\Delta \tau_i$ . The figure shows that  $\Delta D_{st}$  increases monotonically with  $\Delta \tau_i$ . However, the sensitivity to  $\tau_i$  is less then unity. For example, 1% variation in the  $\Delta \tau_i$  causes 0.83% additional  $\Delta D_{st}$ . The magnitude of this difference depends on the  $C_L$  and other transistors parameters. However, they are beyond the scope of this paper.

Gate Delay Model: Equations 11 and 14 give the impact of NBTI on  $\Delta D_{th}$  and  $\Delta D_{st}$  delays. Substituting these terms in Eq. 9, we obtain the gate delay  $\Delta D$  as:

$$\Delta D = \alpha \cdot \frac{\Delta V_{th}}{(V_{qs} - V_{th})} + \left(\frac{\alpha + \nu_t}{1 + \alpha}\right) \cdot \kappa \cdot \Delta \tau_i \tag{15}$$

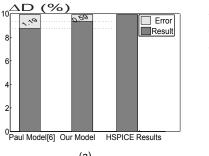

The model presented in the equation is suitable for the circuit delay modeling. Fig.5(a) shows a comparison of Paul's model [6] and our model with the HSPICE simulation. The figure shows that our proposed model have error less than 0.59%, while in case of [6] model the error approaches 1.19%.

#### 4 Circuit Delay Model

In conventional NBTI induced circuit delay models, NBTI impact on circuit delay is considered to be just a sum of delay increments of isolated gates [6, 7]. The correlation among gates and its impact on circuit delay is ignored.

Let us consider a circuit with n gates in a circuit. The circuit delay ( $\Delta D_{circ}$ ) consists of: (a) summation of the delays caused by intrinsic degradations of the gates, (b) summation of delays caused by correlation among gates (front-end delays). That is:

$$\Delta D_{circ} = \sum_{i=1}^{n} \Delta D_{th(i)} + \sum_{i=1}^{n-1} \Delta D_{st(i)}$$

(16)

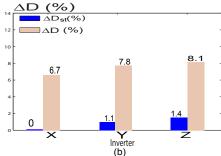

where  $\sum_{i=1}^{n} \Delta D_{th(i)}$  and  $\sum_{i=1}^{n-1} \Delta D_{st(i)}$  are the summation to representing intrinsic delays and front-end delays respectively. To demonstrate the situation we consider the example circuit shown in Fig.2; run HSPICE simulation using 45nm PMOS transistor model and 1.0V supply voltage. Fig.5(b) shows the simulation results for the three inverters of Fig.2 at  $\gamma$ =0.8 for 10 years of operation. The figure reveals that:

– Inverter X have a constant  $\tau_i$  that results in zero  $\Delta D_{st(X)}$ . However, it suffers from additional  $\Delta D = \Delta D_{th} = 6.7\%$ .

Table 1. Delays at input gates, output gates and paths in benchmark circuits

|                 |              |              |                | Percent Gate and Circuit Delay increments |              |                   |                     |              |                   |                     |              |                   |

|-----------------|--------------|--------------|----------------|-------------------------------------------|--------------|-------------------|---------------------|--------------|-------------------|---------------------|--------------|-------------------|

| Circuit(a,b,c)* |              | no of Trans. | Delay at $t=0$ |                                           |              |                   | $10^7 \mathrm{sec}$ |              |                   | $10^8 \mathrm{sec}$ |              |                   |

|                 |              |              | , [            | $\Delta D_1$                              | $\Delta D_n$ | $\Delta D_{circ}$ | $\Delta D_1$        | $\Delta D_n$ | $\Delta D_{circ}$ | $\Delta D_1$        | $\Delta D_n$ | $\Delta D_{circ}$ |

| C4              | 32(36,7,11)  | 996          | 11.68ns        | 1.37                                      | 3.09         | 2.25              | 2.98                | 5.5          | 5.04              | 4.41                | 11.99        | 7.43              |

| C4              | 99(41,32,7)  | 1316         | 14.68ns        | 1.61                                      | 1.71         | 2.91              | 4.06                | 4.37         | 6.17              | 6.13                | 6.48         | 9.01              |

| C8              | 880(60,26,5) | 2118         | 16.75ns        | 1.98                                      | 2.78         | 4.43              | 3.79                | 6.08         | 10.32             | 3.78                | 9.18         | 10.53             |

| C135            | 55(41,32,16) | 2484         | 9.58ns         | 1.20                                      | 2.96         | 1.21              | 2.71                | 6.44         | 2.48              | 4.01                | 7.34         | 5.90              |

a\*=# of inputs, b=# of outputs, c=# of gates in the path

$\Delta D_1$ =Delay of the gate at a primary input,  $\Delta D_n$  =Delay of the gate at a primary output,  $\Delta D_{circ}$ =Delay of a path in benchmarks.

– Inverter Y suffers from 7.8% delay due to NBTI. The additional 1.1% is due to  $\Delta D_{\rm st}$  degradation that constitute 14% of . Similarly, the delay increment of inverter Z approaches 8.1% with a share of 17% from  $\tau_i$  degradation.

The measurements showed that  $\Delta D_{th}$  in X causes an additional 3.0% delay to output transition  $\tau_{o(X)}$ . This increases  $\tau_{i(Y)}$  of Y that casues more  $\Delta D$  (i.e. 7.8%) to Y than X. The higher delay of Z than Y have also the same reason.

# 5 Benchmark Simulations and Analysis

In this section, we present simulation results and their analysis for several benchmark circuits. We have modeled the impact of NBTI using a time dependent external voltage source. Behavior of the source is defined using Verilog-A module. Voltage across the module represent NBTI induced  $\Delta V_{\rm th}$  that causes  $\Delta D$  and consequently  $\Delta D_{circ}$ . We simulated several ISCAS benchmark circuits to analyze NBTI impact on their delays. We have particularly focused on the following analysis: (a) delay of gates at primary input, (b) delay of gates at primary output, and (c) delay of complete paths in a circuit. Since  $\gamma$  of all the gates depend on the circuit topology so it extremely time consuming to determine  $\gamma$  of all the gates. We keep  $\gamma$  of all the primary input gates 0.8 and assume that it will remain same for all the gates.

Table 1 shows the simulation results for the delay of several benchmark circuits. From the table, we have the following observations:

- Delay of paths in the benchmarks circuits increase with increase in stress time. For instance, delay increment of the critical path in C432 for  $\gamma$ =0.8 is 2.25% after 10<sup>5</sup>sec stress time, while it is 5.04% after 10<sup>7</sup>sec and approaches 7.43% after 10<sup>8</sup>sec stress. Other benchmarks also follow the same trend in their delay increment.

- In a given benchmark circuit and under identical  $\gamma$  values the path delay depend on topology of the circuits. For example, C499 and C1355 have same number of inputs and outputs. However, C499 suffers from 7.43% delay while C1355 suffers from 5.90% delay.

- Generally it is claimed that identical gates have similar delay increment under a given  $\gamma$  values. However, we observed that the claim is not true. For example, the primary input gate in C1355 have a delay increment of 4.01% after  $10^8$ sec of stress, while an identical gate at the primary output have a delay increment of 7.34% after the same stress time. The additional 3.33% delay of the output gate is due to the effect of degradation of the previous gates that propagates to the final output gate in the benchmark.

## 6 NBTI Mitigation Techniques

So far we have investigated the root causes of NBTI mechanism at device level, its impact on gate delay and finally, on circuit delay. From the analysis, we conclude that the delays due to NBTI depend on: (a) Holes mobility degradation in the PMOS transistor inversion layer, (b)  $\gamma$  of the gates, (c) operational temperature, (d) supply voltage, and (d) locations of the gates in a circuit. Now we will describe some techniques at transistor level, gate level, and circuit level to mitigate the delays.

**Holes Mobility Increment:** NBTI can be mitigated at the transistor level by, (a) increasing robustness of the holes mobility against the  $N_{\rm IT}$  at Si-SiO<sub>2</sub> interface, and (b) improving the interface structure between Si and SiO<sub>2</sub>. In [17] Islam suggested that the mobility robustness can be achieved by using strained silicon (SiGe source/drain and contact etch stop layer) transistor. Although the scheme is expensive and dictates changes in fabrication process, it ensures minimum circuit delay under NBTI effect.

Temperature Reduction: The electrochemical reactions at Si-SiO<sub>2</sub> interface that cause NBTI degradation are thermally activated. Therefore, by tuning temperature to a lower value, we can reduce NBTI degradation at transistor level that will reduce delay increment at circuit level. Table 6 shows the impact of temperature reduction on the delay. The table shows that the delay of C880 for  $\gamma$ =0.8 is 10.53% at 125°C. However, by reducing temperature to 75°C the delay is only 6.63% (37% less than at 125°C).

Supply Voltage Tunning: The exact impact of supply voltage tunning on NBTI is not clear and there are contradictory arguments. In [18], suggested lower  $V_{dd}$  to mitigate the delay increment, while in [7] negated the argument and favored higher  $V_{dd}$ . Our observation from the simulation affirmed the latter argument. Table 6 shows the simulation results for the voltage reduction. The table shows that supply voltage increment in C432 results in 6.95% (0.62% reduction) delay. We observed that supply voltage have a smaller impact than temperature. It is due to the fact only bond breaking sub-process ( $k_f$  in section II-A) is voltage/field dependent. All the other sub-processes are voltage independent [4]. Additionally, voltage increment shold be in limit as it will cause higher leakage currents.

Table 2. NBTI mitigation by temperature and voltage supply

|      |                     |                        |              | Supply voltage |      |              |  |  |

|------|---------------------|------------------------|--------------|----------------|------|--------------|--|--|

|      | $125^{o}\mathrm{C}$ | $75^{\circ}\mathrm{C}$ | $\Delta D_t$ | 1.1V           | 1.2V | $\Delta D_v$ |  |  |

|      | 7.43                |                        |              | 7.43           | l    |              |  |  |

| C880 | 10.53               | 6.63                   | 37           | 10.53          | 9.76 | 0.67         |  |  |

$\Delta D_t = \%$  delay improvement by temperature reduction,  $\Delta D_v = \%$  delay improvement by voltage tuning.

**Transistor Oversizing:** Transistor oversizing is an effective way to reduce NBTI affects. In [6], the authors suggested 8.7% oversizing of the whole circuit to mitigate NBTI at circuit level. However, we observed that gates at the

primary output have more delay increment than gates at the primary input. Therefore, we choose to increase size of the gates at primary output.

#### 7 Conclusion

In this paper we proposed a new NBTI induced gate delay model. Unlike traditional models that only considers NBTI impact on intrinsic delay of an isolated gates, we also consider the impact on output transition to show the delay correlation among gates. From the model demonstration, we found that depending on the activity ratio of a gate NBTI can cause up to 6.7% intrinsic delay and 3.0% output transition delay. The transition delay increase delay of the next gates as a result gates at outputs of a circuit suffer from more delays than gates at the inputs. Finally, we analyzed different techniques to mitigate NBTI. The analysis concluded that temperature reduction can mitigate 37% of NBTI induced delay. In future, we plane to use the delay model for developing NBTI induced delay testing schemes at circuit level.

## References

- 1. S. Borkar, et al "Micro architecture and Design Challenges for Giga scale Integration", *Pro. of Intl. Sympos. Micro architecture*, pp:3-3, 2004.

- N. Kizmuka "The Impact of BTI for Direct Tunneling Ultra Thin Gate Oxide of MOSFET Scaling", VLSI Technology, Digest of Technical Papers, pp:73-74, 1999.

- 3. W. Abadeer, et al., "Behaviour of NBTI Under AC Dynamic Circuit Conditions", Pro. of International Physics Reliability Symposium(IPRS), pp:17-22, 2003.

- 4. M.A. Alam, et al., "A Comprehensive Model of PMOS NBTI Degradation", *Microelectronics Reliability*, Vol:45, Issue:1, pp:71-81, 2005.

- 5. A.T. Krishnan, et al., "NBTI impact on transistor and circuit: Models, mechanisms and scaling effects", *Pro. of International Electronics Device Meeting(IEDM)*, pp:14.5.1-14.5.4, 2003.

- B.C. Paul, et al "Impact of NBTI on the Temporal Performance Degradation of Digital Circuits", IEEE Electron Device Letter, Vol. 26, No.8, Aug. 2005.

- W. Wang, et al "The Impact of NBTI on the Performance of Combinational and Sequential Circuits", Pro. of DAC, 2007.

- 8. H. Luo, et al "A Novel Gate-Level NBTI Delay Degradation Model with Stacking Effects", *PATMOS*, pp. 160-170, 2007.

- 9. A.I. Kayssi, et al "The Impact of Signal Transition Time on Path Delay Computation", *IEEE Trans. on Circuits and Systems*, Vol.40, No.5, May 1993.

- M. Noda, et al "On the Estimation of NBTI Induced Delay Degradation", Pro. of ETS, 2010.

- 11. K.O. Jeppson, et al "Negative bias of MOS devices at high electric fields and degradation of MNOS devices", *Journal of Applied Physics*, 48, 1977.

- 12. T. Sakuri, et al "Alpha Power Law MOSFET Model and its Application to CMOS Inverter Delay and Other Formulas ", *IEEE Journal of Solid-State Circuits*, Vol. 25, April 1990.

- 13. M.J. Bellido, et al "Logic Timing Simulation and the Degradation Delay Model ", Imperial College Press, 2006.

14. S. Khan, et al "NBTI Modeling in the Framework of Temperature Variation ",

- 14. S. Khan, et al "NBTI Modeling in the Framework of Temperature Variation", *Proc. of DATE*, pp:978-981, Mar. 2010.

- 15. "Predictive Technology Model", http://ptm.asu.edu/.

- 16. R. Tayade, et al "Critical Path Selection for Delay Testing by Considering Noise Coupling", Journal of Electron Test, pp. 213-223, 2009.

- A.E. Islam, et al "On the Possibility of Degradation Free Field Effect Transistor", Applied Physics Letter, 2008.

- 18. G. Karakonstantis, et al "A Self-Consistence Model to Estimate NBTI Degradation and a Comprehensive On-Line System Lifetime Enhancement Technique", *IOLTS*, pp:978-981, July. 2010.