## Compiler Strategies for Transport Triggered Architectures

Johan Janssen

## Compiler Strategies for Transport Triggered Architectures

Proefschrift

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus prof.ir. K.F. Wakker, voorzitter van het College voor Promoties, in het openbaar te verdedigen

op maandag 17 september 2001 om 16:00 uur

door

Johannes Antonius Andreas Jozef JANSSEN

elektrotechnisch ingenieur geboren te Wamel Dit proefschrift is goedgekeurd door de promotoren: Prof.dr.ir. A.J. van de Goor Prof.dr. H. Corporaal

Samenstelling promotiecommissie:

| Rector Magnificus,            | voorzitter                              |

|-------------------------------|-----------------------------------------|

| Prof.dr.ir. A.J. van de Goor, | Technische Universiteit Delft, promotor |

| Prof.dr. H. Corporaal,        | T.U. Eindhoven / IMEC, promotor         |

| Prof.dr.ir. E.F. Deprettere,  | Universiteit Leiden                     |

| Prof.dr.ir. Th. Krol,         | Universiteit Twente                     |

| Prof.dr.ir. R.H.J.M. Otten,   | Technische Universiteit Eindhoven       |

| Prof.dr.ir. H.J. Sips,        | Technische Universiteit Delft           |

| Dr. C. Eisenbeis,             | INRIA, Rocquencourt                     |

|                               |                                         |

Published and distributed by: DUP Science

DUP Science is an imprint of Delft University Press P.O. Box 98 2600 MG Delft The Netherlands Telephone: +31 15 27 85 678 Telefax: +31 15 27 85 706 E-mail: DUP@Library.TUDelft.NL

ISBN 90-407-2209-9

Keywords: Compilers, Instruction Scheduling, Register Assignment

This work was carried out in the ASCI graduate school. ASCI dissertation series number 69.

Copyright © 2001 by Johan Janssen

All rights reserved. No part of the material protected by this copyright notice may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying, recording or by any information storage and retrieval system, without written permission from the publisher: Delft University Press.

Printed in The Netherlands

This dissertation is dedicated to the loving memory of my mother

# Acknowledgements

This Ph.D. thesis is the result of my research at the Computer Engineering group of the Electrical Engineering department of the Delft University of Technology.

First, I would like to express my gratitude to Henk Corporaal, my supervisor, for his everlasting support, valuable comments and for the numerous discussions we had. In addition, I want to thank prof. Ad van de Goor for being my promotor and for giving me the opportunity to perform my research in his group.

Secondly, I thank the reviewers of this thesis, Andrea Cilio, Henjo Schot and my sister Willemien Korfage for their valuable comments on (parts of) the first drafts of this thesis. I thank Walter Groeneveld for his contribution on the formulation of the "stellingen". Furthermore, I would like to thank my fellow Ph.D. students within the MOVE project: Marnix Arnold, Jeroen Hordijk, Steven Roos and especially Jan Hoogerbrugge for their work on the TTA compiler. I would like to thank the system administrators Jean-Paul van der Jagt, Tobias Nijweide and Bert Meijs for providing an excellent working computer environment. In addition, I would also like to thank all my former colleagues and students of the Computer Engineering group for the enjoyable working environment.

Finally, I would like to thank my family, friends and TNO colleagues for their support and encouragement.

Johan Janssen Delft, July 2001

# Contents

| Ac | knov | vledgei  | ments                                          | vii |

|----|------|----------|------------------------------------------------|-----|

| 1  | Intr | oductio  | n                                              | 1   |

|    | 1.1  | Instru   | ction-Level Parallelism                        | 2   |

|    |      | 1.1.1    | ILP Architecture Arena                         | 3   |

|    |      | 1.1.2    | Architectural Trade-off                        | 6   |

|    | 1.2  | Resear   | rch Goals                                      | 9   |

|    | 1.3  |          | Outline                                        | 11  |

| 2  | TTA  | s: An (  | Overview                                       | 13  |

|    | 2.1  | From     | VLIW to TTA                                    | 13  |

|    | 2.2  |          | oort Triggered Architectures                   | 15  |

|    |      | 2.2.1    | TTA Instruction Format                         | 16  |

|    |      | 2.2.2    | Function Units                                 | 17  |

|    |      | 2.2.3    | Register Files                                 | 18  |

|    |      | 2.2.4    | Immediates                                     | 18  |

|    |      | 2.2.5    | Move Buses                                     | 18  |

|    |      | 2.2.6    | Sockets                                        | 19  |

|    |      | 2.2.7    | Control Flow and Conditional Execution         | 19  |

|    |      | 2.2.8    | Software Bypassing                             | 20  |

|    |      | 2.2.9    | Operand Sharing                                | 21  |

| 3  | Con  | npiler ( | Dverview                                       | 23  |

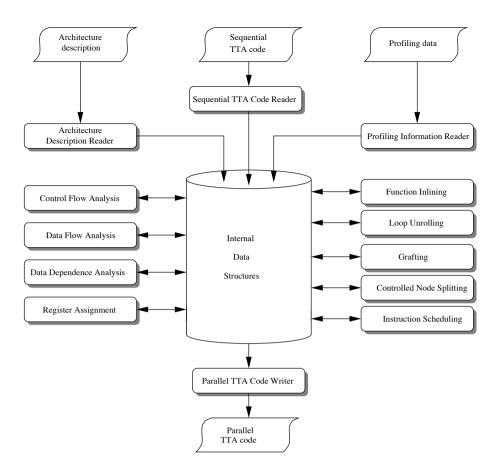

|    | 3.1  | Front-   | end                                            | 24  |

|    | 3.2  | Back-e   | end Infrastructure                             | 26  |

|    |      | 3.2.1    | Reading and Writing                            | 26  |

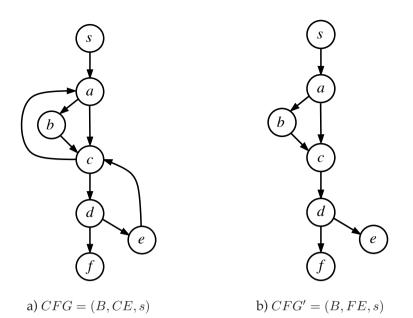

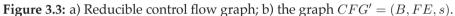

|    |      | 3.2.2    | Control Flow Analysis                          | 27  |

|    |      | 3.2.3    | Data Flow Analysis                             | 30  |

|    |      | 3.2.4    | Data Dependence Analysis                       | 32  |

|    |      | 3.2.5    | Loop Unrolling, Function Inlining and Grafting | 35  |

|    | 3.3  | Regist   | er Assignment                                  | 35  |

|    |      | 3.3.1    | Graph Coloring                                 | 36  |

|    |      | 3.3.2    | Spilling                                       | 40  |

|   | 3.4        | 3.3.4TTA vs. OTAInstruction Scheduling3.4.1List Scheduling3.4.2Resource Assignment3.4.3Local Scheduling3.4.4Global Scheduling | 41<br>43<br>43<br>44<br>45<br>46<br>50 |

|---|------------|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

|   |            | 1 0                                                                                                                           | 54                                     |

| 4 |            |                                                                                                                               | <b>59</b><br>59                        |

|   | 4.1<br>4.2 |                                                                                                                               | 59<br>60                               |

|   | т.2        |                                                                                                                               | 60                                     |

|   |            | 1 0                                                                                                                           | 63                                     |

|   | 4.3        |                                                                                                                               | 65                                     |

|   | 4.4        | 0 1                                                                                                                           | 67                                     |

| 5 | The        | Phase Ordering Problem                                                                                                        | 69                                     |

| 0 | 5.1        |                                                                                                                               | 70                                     |

|   |            |                                                                                                                               | 70                                     |

|   |            |                                                                                                                               | 72                                     |

|   |            | 5.1.3 Dependence-Conscious Early Register Assignment for                                                                      |                                        |

|   |            |                                                                                                                               | 78                                     |

|   | <b>-</b> 0 | , 1                                                                                                                           | 81                                     |

|   | 5.2        | 0 0                                                                                                                           | 83<br>84                               |

|   |            |                                                                                                                               | 86                                     |

|   |            |                                                                                                                               | 88                                     |

|   |            | 0                                                                                                                             | 90                                     |

|   | 5.3        |                                                                                                                               | 91                                     |

|   |            |                                                                                                                               | 92                                     |

|   |            | 5.3.2 Integrated Instruction Scheduling and Register Assign-                                                                  |                                        |

|   |            |                                                                                                                               | 93                                     |

|   | 5.4        | Conclusion                                                                                                                    | 96                                     |

| 6 | Inte       | grated Assignment and Local Scheduling                                                                                        | 99                                     |

|   | 6.1        |                                                                                                                               | .00                                    |

|   | 6.2        |                                                                                                                               | .01                                    |

|   | 6.3        | The Interference Register Set                                                                                                 | .05                                    |

|   | 6.4        |                                                                                                                               | .09                                    |

|   |            | 0 1 0                                                                                                                         | 110                                    |

|   |            | 1 0 1                                                                                                                         | 110<br>112                             |

|   |            | 0                                                                                                                             | 112<br>117                             |

|   | 6.5        |                                                                                                                               | 118                                    |

|   |            | 0                                                                                                                             | -                                      |

|   |                                                                                              | 6.5.1 Generation of Callee-saved Code                                                                                                                                                                                                                                                                                                                                                      | 118                                                                                                                               |

|---|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

|   |                                                                                              | 6.5.2 Generation of Caller-Saved Code                                                                                                                                                                                                                                                                                                                                                      | 120                                                                                                                               |

|   | 6.6                                                                                          | Experiments and Evaluation                                                                                                                                                                                                                                                                                                                                                                 | 121                                                                                                                               |

|   |                                                                                              | 6.6.1 Register Selection                                                                                                                                                                                                                                                                                                                                                                   | 122                                                                                                                               |

|   |                                                                                              | 6.6.2 Operation Selection                                                                                                                                                                                                                                                                                                                                                                  | 123                                                                                                                               |

|   |                                                                                              | 6.6.3 Basic Block Selection                                                                                                                                                                                                                                                                                                                                                                | 124                                                                                                                               |

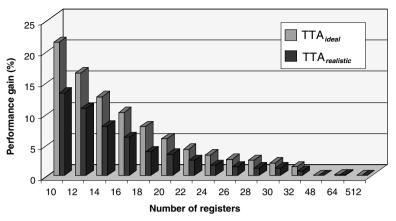

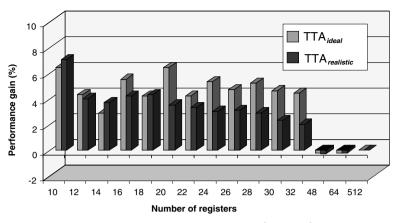

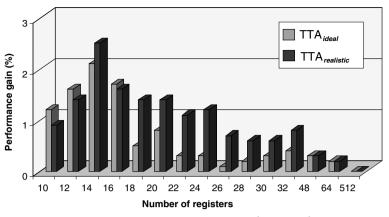

|   |                                                                                              | 6.6.4 Early vs. Integrated Assignment                                                                                                                                                                                                                                                                                                                                                      | 126                                                                                                                               |

|   | 6.7                                                                                          | Conclusions                                                                                                                                                                                                                                                                                                                                                                                | 130                                                                                                                               |

| 7 | Inte                                                                                         | egrated Assignment and Global Scheduling                                                                                                                                                                                                                                                                                                                                                   | 131                                                                                                                               |

|   | 7.1                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                            | 131                                                                                                                               |

|   |                                                                                              | 7.1.1 Importing a Use                                                                                                                                                                                                                                                                                                                                                                      | 132                                                                                                                               |

|   |                                                                                              | 7.1.2 Importing a Definition                                                                                                                                                                                                                                                                                                                                                               | 133                                                                                                                               |

|   | 7.2                                                                                          | Importing Operations                                                                                                                                                                                                                                                                                                                                                                       | 136                                                                                                                               |

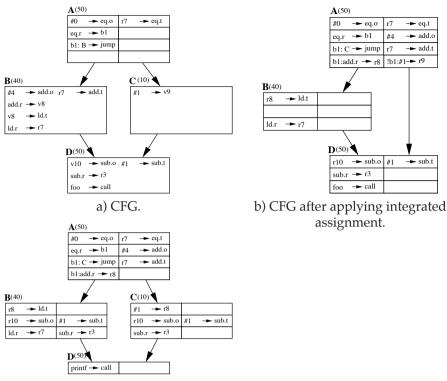

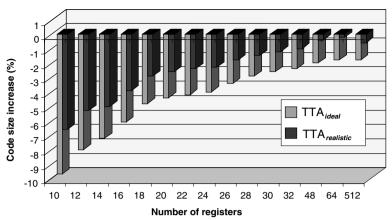

|   | 7.3                                                                                          | Example                                                                                                                                                                                                                                                                                                                                                                                    | 137                                                                                                                               |

|   | 7.4                                                                                          | Spilling                                                                                                                                                                                                                                                                                                                                                                                   | 140                                                                                                                               |

|   | 7.5                                                                                          | State Preserving Code                                                                                                                                                                                                                                                                                                                                                                      | 141                                                                                                                               |

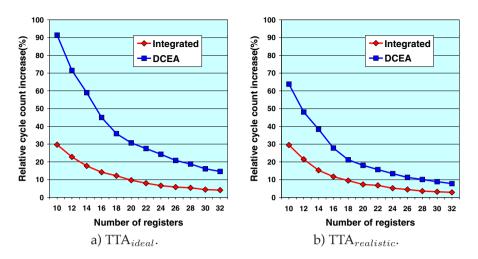

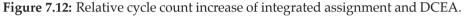

|   | 7.6                                                                                          | Experiments and Evaluation                                                                                                                                                                                                                                                                                                                                                                 | 143                                                                                                                               |

|   |                                                                                              | 7.6.1 Region Selection                                                                                                                                                                                                                                                                                                                                                                     | 143                                                                                                                               |

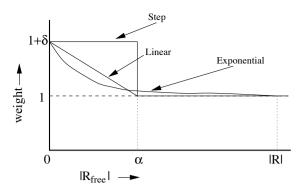

|   |                                                                                              | 7.6.2 Global Spill Cost Heuristic                                                                                                                                                                                                                                                                                                                                                          | 144                                                                                                                               |

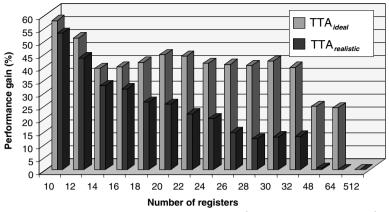

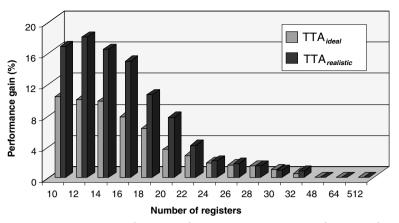

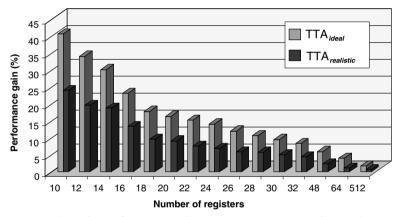

|   |                                                                                              | 7.6.3 Early vs. Integrated Assignment                                                                                                                                                                                                                                                                                                                                                      | 145                                                                                                                               |

|   | 7.7                                                                                          | Conclusions                                                                                                                                                                                                                                                                                                                                                                                | 150                                                                                                                               |

|   |                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                   |

| 8 | Inte                                                                                         | egrated Assignment and Software Pipelining                                                                                                                                                                                                                                                                                                                                                 | 151                                                                                                                               |

| 8 |                                                                                              | egrated Assignment and Software Pipelining<br>Register Pressure                                                                                                                                                                                                                                                                                                                            | <b>151</b><br>152                                                                                                                 |

| 8 | 8.1                                                                                          | Register Pressure                                                                                                                                                                                                                                                                                                                                                                          | 152                                                                                                                               |

| 8 | 8.1<br>8.2                                                                                   | Register Pressure                                                                                                                                                                                                                                                                                                                                                                          | 152<br>156                                                                                                                        |

| 8 | 8.1                                                                                          | Register Pressure                                                                                                                                                                                                                                                                                                                                                                          | 152<br>156<br>158                                                                                                                 |

| 8 | 8.1<br>8.2                                                                                   | Register PressureRegister Assignment and Software PipeliningIntegrated Assignment and Modulo Scheduling8.3.1The Interference Register Set                                                                                                                                                                                                                                                  | 152<br>156<br>158<br>159                                                                                                          |

| 8 | 8.1<br>8.2<br>8.3                                                                            | Register PressureRegister Assignment and Software PipeliningIntegrated Assignment and Modulo Scheduling8.3.1The Interference Register Set8.3.2Spilling                                                                                                                                                                                                                                     | 152<br>156<br>158<br>159<br>160                                                                                                   |

| 8 | 8.1<br>8.2                                                                                   | Register PressureRegister Assignment and Software PipeliningIntegrated Assignment and Modulo Scheduling8.3.1The Interference Register Set8.3.2SpillingExperiments and Evaluation                                                                                                                                                                                                           | 152<br>156<br>158<br>159<br>160<br>161                                                                                            |

| 8 | 8.1<br>8.2<br>8.3                                                                            | Register Pressure                                                                                                                                                                                                                                                                                                                                                                          | 152<br>156<br>158<br>159<br>160<br>161<br>161                                                                                     |

| 8 | 8.1<br>8.2<br>8.3                                                                            | Register PressureRegister Assignment and Software PipeliningIntegrated Assignment and Modulo Scheduling8.3.1The Interference Register Set8.3.2SpillingExperiments and Evaluation                                                                                                                                                                                                           | 152<br>156<br>158<br>159<br>160<br>161                                                                                            |

|   | <ul><li>8.1</li><li>8.2</li><li>8.3</li><li>8.4</li><li>8.5</li></ul>                        | Register Pressure          Register Assignment and Software Pipelining          Integrated Assignment and Modulo Scheduling          8.3.1       The Interference Register Set          8.3.2       Spilling          Experiments and Evaluation           8.4.1       Spilling or Increasing the <i>II</i> 8.4.2       Early vs. Integrated Assignment          Conclusions               | 152<br>156<br>158<br>159<br>160<br>161<br>161<br>162<br>164                                                                       |

| 8 | <ul> <li>8.1</li> <li>8.2</li> <li>8.3</li> <li>8.4</li> <li>8.5</li> <li>The</li> </ul>     | Register Pressure          Register Assignment and Software Pipelining          Integrated Assignment and Modulo Scheduling          8.3.1       The Interference Register Set          8.3.2       Spilling          Experiments and Evaluation           8.4.1       Spilling or Increasing the <i>II</i> 8.4.2       Early vs. Integrated Assignment          Partitioned Register File | 152<br>156<br>158<br>159<br>160<br>161<br>161<br>162<br>164<br><b>167</b>                                                         |

|   | <ul><li>8.1</li><li>8.2</li><li>8.3</li><li>8.4</li><li>8.5</li></ul>                        | Register Pressure                                                                                                                                                                                                                                                                                                                                                                          | 152<br>156<br>158<br>159<br>160<br>161<br>161<br>162<br>164<br><b>167</b><br>168                                                  |

|   | <ul> <li>8.1</li> <li>8.2</li> <li>8.3</li> <li>8.4</li> <li>8.5</li> <li>The</li> </ul>     | Register Pressure                                                                                                                                                                                                                                                                                                                                                                          | 152<br>156<br>158<br>159<br>160<br>161<br>161<br>162<br>164<br><b>167</b><br>168<br>169                                           |

|   | <ul> <li>8.1</li> <li>8.2</li> <li>8.3</li> <li>8.4</li> <li>8.5</li> <li>The</li> </ul>     | Register Pressure          Register Assignment and Software Pipelining          Integrated Assignment and Modulo Scheduling          8.3.1       The Interference Register Set          8.3.2       Spilling          Experiments and Evaluation           8.4.1       Spilling or Increasing the <i>II</i> 8.4.2       Early vs. Integrated Assignment          Conclusions               | 152<br>156<br>158<br>159<br>160<br>161<br>161<br>162<br>164<br><b>167</b><br>168<br>169<br>170                                    |

|   | <ul> <li>8.1</li> <li>8.2</li> <li>8.3</li> <li>8.4</li> <li>8.5</li> <li>The</li> </ul>     | Register Pressure                                                                                                                                                                                                                                                                                                                                                                          | 152<br>156<br>158<br>159<br>160<br>161<br>161<br>162<br>164<br><b>167</b><br>168<br>169<br>170<br>171                             |

|   | <ul> <li>8.1</li> <li>8.2</li> <li>8.3</li> <li>8.4</li> <li>8.5</li> <li>The 9.1</li> </ul> | Register Pressure                                                                                                                                                                                                                                                                                                                                                                          | 152<br>156<br>158<br>159<br>160<br>161<br>161<br>162<br>164<br><b>167</b><br>168<br>169<br>170<br>171<br>171                      |

|   | <ul> <li>8.1</li> <li>8.2</li> <li>8.3</li> <li>8.4</li> <li>8.5</li> <li>The</li> </ul>     | Register Pressure                                                                                                                                                                                                                                                                                                                                                                          | 152<br>156<br>158<br>159<br>160<br>161<br>161<br>162<br>164<br><b>167</b><br>168<br>169<br>170<br>171<br>171<br>174               |

|   | <ul> <li>8.1</li> <li>8.2</li> <li>8.3</li> <li>8.4</li> <li>8.5</li> <li>The 9.1</li> </ul> | Register Pressure                                                                                                                                                                                                                                                                                                                                                                          | 152<br>156<br>158<br>159<br>160<br>161<br>161<br>162<br>164<br><b>167</b><br>168<br>169<br>170<br>171<br>171<br>174<br>175        |

|   | <ul> <li>8.1</li> <li>8.2</li> <li>8.3</li> <li>8.4</li> <li>8.5</li> <li>The 9.1</li> </ul> | Register Pressure                                                                                                                                                                                                                                                                                                                                                                          | 152<br>156<br>158<br>159<br>160<br>161<br>161<br>162<br>164<br><b>167</b><br>168<br>169<br>170<br>171<br>171<br>174<br>175<br>177 |

|   | <ul> <li>8.1</li> <li>8.2</li> <li>8.3</li> <li>8.4</li> <li>8.5</li> <li>The 9.1</li> </ul> | Register Pressure                                                                                                                                                                                                                                                                                                                                                                          | 152<br>156<br>158<br>159<br>160<br>161<br>161<br>162<br>164<br><b>167</b><br>168<br>169<br>170<br>171<br>171<br>174<br>175        |

|           | 9.4                          | Integrated Assignment and Partitioned Register Files        | 183               |

|-----------|------------------------------|-------------------------------------------------------------|-------------------|

|           |                              | 9.4.1 Local Heuristics                                      | 184               |

|           |                              | 9.4.2 A Global Heuristic                                    | 186               |

|           | 9.5                          | Conclusions                                                 |                   |

| 10        | Sum                          | mary and Future Research                                    | 191               |

|           | 10.1                         | Summary                                                     | 191               |

|           | 10.2                         | Contributions                                               | 195               |

|           |                              | Proposed Research Directions                                |                   |

| A         | Integ                        | grated Assignment Benchmark Results                         | 203               |

|           |                              |                                                             |                   |

| В         | Parti                        | itioned Register File Benchmark Results                     | 211               |

| В         |                              | itioned Register File Benchmark Results<br>Early Assignment |                   |

| В         | B.1                          | itioned Register File Benchmark Results<br>Early Assignment | 211               |

|           | B.1                          | Early Assignment                                            | 211               |

| Gl        | B.1<br>B.2<br>ossar          | Early Assignment                                            | 211<br>213        |

| Gl<br>Bil | B.1<br>B.2<br>ossar<br>bliog | Early Assignment                                            | 211<br>213<br>217 |

# 1

## Introduction

T oday, microprocessors can be found in virtually every electronic device. Not only workstations and PCs contain microprocessors; they can also be found in equipment for daily use such as television sets, mobile phones, PDAs (Personal Digital Assistant), microwaves and cars, or in specialized devices such as the automatic pilot in an aircraft, robots and medical instrumentation. More than 100 million microprocessors for general-purpose computers (PCs, workstations, mainframes, etc.) are sold annually. This is however, only the tip of the iceberg. Over two billion microprocessors are estimated to be sold annually for embedded applications [Leh00]. The embedded microprocessor market is growing, according to Dataquest, from \$7.5 billion in 1998 to\$ 26 billion by 2002 [FBF+00]. Furthermore, the amount of produced embedded software exceeds the produced general-purpose software by a factor of five [EZ97].

The performance of microprocessors is increasing rapidly. This increase is driven by the demand to execute over and over again, more complex and larger applications. Various architectures are used to deliver the requested performance, like *CISC* (*Complex Instruction Set Computer*) and *RISC* (*Reduced Instruction Set Computer*) processor architectures. At this moment, we are in the middle of the *instruction-level parallelism* (*ILP*) era. The power of ILP processing lies in the ability to execute multiple operations in parallel. It should be obvious that this potentially results in large performance improvements. Various ILP architectures like *superscalar architectures*, *VLIWs* (*Very Long Instruction Word architectures*) and *TTAs* (*Transport Triggered Architectures*) are proposed and implemented. Unfortunately, the ability in hardware to execute multiple operations in parallel, by adding extra resources, does not always lead to a performance increase. Numerous constraints prevent the efficient usage of the resources of ILP processors. To efficiently utilize the available resources the order of operations in the program code should be rearranged. This process is called *instruction scheduling*. *Register assignment* manages the available high-speed on-chip memory elements called *registers*. These registers are used for holding temporary values produced by the operations. The order, in which register assignment and instruction scheduling are applied, plays an important role in the exploitation of ILP. An efficient register assignment may hinder an efficient reordering of the operations. In addition, efficient instruction scheduling may result in an inefficient use of the registers. In this dissertation, this *phase ordering problem* is discussed, solutions are proposed and results are given.

The research is performed within the MOVE project at the Delft University of Technology. The MOVE project aims at bringing instruction-level parallelism within the reach of *application specific processors* (*ASPs*) in a flexible, scalable and cost effective way. These processors are designed for a specialized task and can be found in all kinds of equipment like TVs, cars, copiers, cameras, etc. To achieve these goals, a new processor architecture is proposed and described. This new architecture is called the Transport Triggered Architecture, or in short TTA [Cor98]. Several processors using this new architecture have been designed and implemented [CvdA93, AHC96, TNO99, VLW00]. The performance of TTA processors highly depends on the quality of the compiler. Therefore, to fully exploit the available ILP provided by TTA processors, research is performed to develop new compiler techniques and strategies to enhance instruction-level parallelism.

In this chapter, the concept of instruction-level parallelism is introduced in Section 1.1. The research goals of this thesis are formulated in Section 1.2. An overview of the remaining chapters of this thesis is given in Section 1.3.

## 1.1 Instruction-Level Parallelism

Instruction-Level Parallelism (ILP) is the family of processor architectures and compiler techniques that enhances performance by executing multiple operations in parallel. The processors provide the resources to execute operations in parallel. The architecture of an ILP processor allows simultaneously access to the duplicated resources, which improves performance. The question of how much ILP is available in programs is addressed in a number of articles [JW89, Wal91, LW92, TGH92, LW97]. Studies to measure the maximum available ILP have critical shortcomings, however. First, many of these studies assume the presence of infinite processor resources and assume perfect program behavior predictors. In this case, the upper limit is too optimistic. Secondly, these studies do not consider modern or future techniques to enhance ILP. This results in a too pessimistic upper limit. Therefore, these studies are of

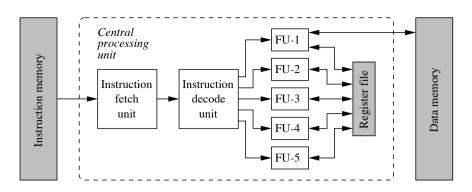

Figure 1.1: General organization of ILP architectures.

limited value. The maximum available ILP estimates range between 2 [JW89] and 1000 [LW97]. One should keep in mind that the exploitable ILP highly depends on the application. Scientific programs have inherently more ILP than control-intensive programs. To discover and to increase the ILP in programs, compiler technology is used. Discovering and exploiting ILP in programs, will be key to future increases in microprocessor performance [SCD<sup>+</sup>97].

Various architectures used to exploit ILP are described in Section 1.1.1. The architectural trade-off is discussed in Section 1.1.2.

#### 1.1.1 ILP Architecture Arena

The general organization of ILP architectures is shown in Figure 1.1. The *instruction fetch unit* reads the instructions from the *instruction memory*. These instructions are decoded and sent to the *function units* (*FUs*). The *central processing unit* (*CPU*) shown in the figure contains five FUs. The FUs perform the actual computation such as additions, multiplications, etc. One of the FUs in the figure is able to perform load and store operations on the *data memory*. Temporary data is stored in registers. These registers are grouped into the *register file* (*RF*). The FUs exchange data via this *shared* RF.

The main reason for the enormous research interest in ILP architectures nowadays, is the ability to have more silicon space available than a RISC processor requires. This allows the duplication of FUs and data paths. Having duplicated FUs means that multiple operations can be executed simultaneously. The data path transports data between the various resources in a processor. More FUs results in the need for a larger data path. The registers in an RF can be accessed by a limited number of ports. Increasing the number of ports, and thus increasing the data path to and from the RF, enables the exploitation of more ILP.

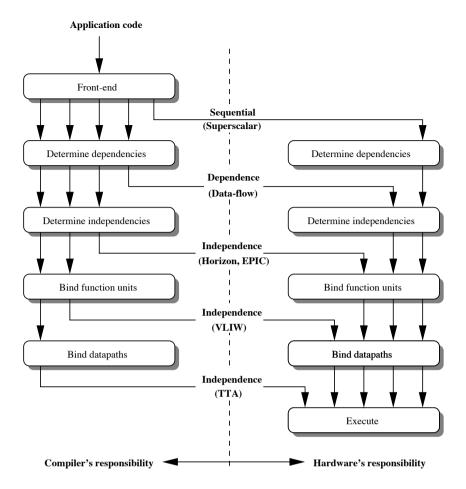

In [RF93] an excellent overview of the dynamic history of ILP architectures is given. Although the importance of ILP was already recognized in the early fifties [Wil51], and ILP processors were build in the eighties [BYA93, RYYT89, SS93], it took until the nineties, to become a key technology for microprocessor performance. Rau and Fisher [RF93] classify ILP architectures into three categories: sequential architectures, dependence architectures, and independence architectures.

#### Sequential architectures

*Sequential architectures* execute programs that contain no explicit information regarding dependences between operations. The programs for these architectures consist of a sequential operation stream. It is the responsibility of the hardware to detect dependences between operations, and to rearrange the operation order to achieve fast computation; this is called *dynamic scheduling*. An operation starts to execute if it does not depend on an operation currently being executed and if the resources needed for the operation are free.

Implementations of sequential ILP architectures are known as *super-scalars* [Joh91]. Superscalars exploit the ILP of a program in hardware; this requires extra logic to detect ILP and to dispatch operations to the FUs. Super-scalars differ in their *issue width* (i.e., the maximum number of operations that can be simultaneously executed), and in the complexity of their instruction scheduler. Simple superscalars, like the Alpha 21064, issue operations in the same order as they appear in the program while others, like the PowerPC 601 and the Pentium 4 [Int00], allow instructions to be issued *out-of-order* [SW94]. A disadvantage of superscalars is their limited scalability, for example increasing the issue width often results in a completely new and much more complex design [PJS96].

Superscalars do not require a compiler to exploit ILP, since there is no way to explicitly communicate information regarding ILP from the compiler to the hardware. However, many ILP compiler techniques may be beneficial to enhance superscalar performance [SCD<sup>+</sup>97, STK98, Wol99].

#### **Dependence** architectures

Dependence architectures execute programs consisting of operations and information about the data dependences between operations. The programmer or compiler adds this information to the program, which releases the hardware from detecting these dependences. The responsibility of the hardware is to detect operations that are ready for execution and to find free resources.

*Data-flow* processors [GS95] are representatives of this class. The operations of these processors contain a list of all data dependent successor operations. When an operation finishes execution, a copy of its result is created for each of its successor operations. As soon as all the input operands of an operation and the required resources are available the operation is executed. Since

the operands of an operation are implicitly specified by its predecessors, the operands do not have to be specified.

#### **Independence** architectures

Programs for *independence architectures* contain, besides the operations, information about independences between the operations. The compiler is responsible for identifying parallelism in a program. It communicates this information to the hardware by specifying which operations are independent of each other.

An example of an independence architecture is the Horizon architecture [TS88]. The compiler encodes an integer H into each operation. This integer tells the hardware that the next H operations in the operation stream are data independent of the current operation. This releases the hardware from detecting data independence, however, the hardware still is responsible for assigning resources to the operations.

Also the *Explicitly Parallel Instruction Computing* (*EPIC*) architecture [ACM<sup>+</sup>98] is classified as an independence architecture. The instructions of an EPIC architecture contain multiple operations. Each instruction includes a template, which indicates whether the operations in the instruction are independent. The template also indicates whether the instruction can be executed in parallel with neighbor instructions. An example of the EPIC architecture is the IA-64 instruction set architecture [IA99] as developed by Intel and Hewlett Packard in a joint effort. An actual implementation is Intel's Itanium processor [Abe00].

Another independence architecture is the Very Long Instruction Word (VLIW) architecture [BYA93, DT93, L<sup>+</sup>93, SS93, GNAB92, HA99, Kla00]. A VLIW compiler not only releases the hardware from detecting independences, but it also assigns the FUs to the operations. A VLIW program specifies on which FU each operation should be executed, and when each operation should be issued. In the context of VLIW architectures, it is important to distinguish between operations and instructions. An operation is a unit of computation, such as an addition, memory load or branch. An instruction consists of multiple operations. The operations in an instruction are issued simultaneously.

The compiler plays an important role to enhance the performance of VLIW processors. In fact, the compiler decides in which order operations are executed, with respect to the data dependence and resource constraints. To accomplish this the compiler uses a detailed description of the processor. It must exactly know how many operations can be executed in parallel. This is in contrast with the previous discussed approaches, where the hardware does the assignment of FUs to operations. Research in the area of exploiting ILP with the use of compilers is still ongoing as a result of the growing interest in VLIW processors. Examples of VLIW implementations are Cydrome's Cydra

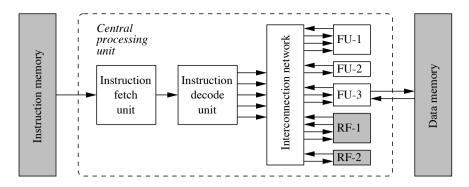

Figure 1.2: General organization of a TTA.

5 [RYYT89], Multiflow's TRACE 14/300 [SS93], Philip's TriMedia [SRD96] processor, the TMS320C6201 DSP processor of Texas Instruments [TI99], BOPS's ManArray [PV00] and Transmeta's Crusoe processor [Kla00].

The Transport Triggered Architecture (TTA) is also classified as an independence architecture. TTAs resemble VLIWs; however, where VLIWs specify operations in an instruction, TTAs also specify the transports between FUs and RFs. This gives the compiler an even larger responsibility, since now not only the FUs and registers need to be assigned but also the transport resources. The general organization of a TTA is given in Figure 1.2. It differs from other ILP architectures (see Figure 1.1) in the sense that not all FUs require a direct connection to the RF. The FUs exchange data via the *interconnection network* instead of using a shared RF. This reduces the complexity of the data path considerably as will be shown in Section 2.1.

The difference, between the three classes of ILP architectures, is the division of the responsibility of the ILP exploitation between the hardware and the compiler. Figure 1.3 summarizes the responsibilities for each type of ILP architecture.

#### 1.1.2 Architectural Trade-off

The most visible ILP processors are general-purpose processors, which can be found in workstations and PCs. For these processors, the superscalar architecture is the current technology of choice. Superscalars have advantages compared to VLIWs and TTAs because they provide binary compatibility, which allows existing applications to run on new machines with a different level of ILP without recompiling. Binary compatibility is an important issue for users who want to upgrade their hardware, without buying new application software. The dynamic scheduling ability of superscalars can adapt the order of execution in situations that were unknown at compile time. It can handle operations with variable latencies, such as load operations with potential cache

Figure 1.3: ILP architecture classification.

misses. Furthermore, it can reorder memory references whose independence could not be determined at compile time. It does this by comparing their effective addresses. On the other hand, superscalars have a limited view of the operations it can reorder, typically 4 to 64 operations can be considered. The hardware needed to perform the data independence tests and the assignment of the resources largely limits the scalability of superscalars. The number of transistors required to implement this level of intelligence is substantial and the time it takes to execute this work also adds a significant overhead to the pipeline. The enormous design effort required to increase the issue width of a superscalar increases the time-to-market. Furthermore, the increasingly complex design needed to make these processors puts a question mark over how many companies can afford designing them. Dataflow and Horizon processor architectures are academic research projects and did not found widespread application in the microprocessor market. Processors with an EPIC architecture are just starting to emerge. Initially they will replace superscalars in high-end PCs and workstations. Their hardware complexity is between superscalars and VLIWs. Compiler techniques developed for VLIWs and TTAs are also useful for EPIC based processors.

For Application Specific Processors (ASPs) time-to-market is an important issue. For many companies, it is of vital importance to introduce high quality ASPs at a low cost and within a short time frame. This is the promise of VLIWs and TTAs: by removing complexity from the hardware, simple processors are created that increase performance far more easily than superscalars. Simple hardware increases clock speeds more aggressively than is possible with today's complex superscalars, and more FUs can be easily added to exploit the parallelism existing in applications. TTAs are even more scalable than VLIWs since they do not require that each FU has its own private connection to the RF. VLIWs and TTAs can exploit large amounts of ILP with relatively simple control logic. This not only results in less silicon, but also reduces the power consumption. The compiler for these architectures can reorder the operations within a larger scope, normally tens or hundreds of operations. This gives a major performance benefit compared to superscalars. Unfortunately, VLIWs and TTAs do not provide binary compatibility. Changing the issue width reguires recompiling the application. Several methods are proposed to solve this limitation [Rau93, CS95], however no widely accepted solution has been found yet<sup>1</sup>. For companies that develop ASPs, binary compatibility is not an issue, because they usually own the application code and can recompile it for another processor. VLIWs and TTAs are not able to adapt their instruction scheduling strategy to run-time unpredictable situations. When, for instance, a cache miss is encountered and the following instruction needs the data, the processor is locked until the data is available. Furthermore, the instruction scheduler is often hindered by ambiguous memory references. Compile-time analysis can help to alleviate this problem. The instructions of a VLIW or a TTA specify which *n* operations must be executed in parallel. However, it is very unlikely that n operations can be found. The empty places in the instructions are then filled with no-ops. This lowers the code density compared with superscalars. Efficient encoding and compression techniques [CBLM96, L<sup>+</sup>93, RYYT89] can be used to solve this problem. Although the market for processors in embedded systems is less visible than the market for superscalars, the embedded market is much larger. Due to these reasons, new compiler techniques for VLIW and TTAs have a lot of interest in academic and industrial research.

<sup>&</sup>lt;sup>1</sup>The Java [GJS96] platform solves this problem by using a virtual machine. This extra software layer decreases performance and does not yet support the exploitation of ILP. Research has to prove whether ILP can efficiently be exploited by the Java platform [EA97, GV97]. Code morphing [Kla00], as introduced in Transmeta's Crusoe processor translates during execution x86 instruction in VLIW instructions. This software layer implements a virtual machine on a VLIW processor.

### 1.2 Research Goals

The research described in this dissertation is performed within the MOVE project. This project aims at the automatic generation of application specific processors and their compilers. In this project, a new architecture is developed: the Transport Triggered Architecture (TTA). TTAs are very well suited for ASPs since they provide scalability and flexibility. Since TTAs fall into the category of independence architectures, the compiler is responsible for detecting and exploiting ILP. Two of the most important code generation phases for ILP processors in general, and TTAs in specific, are register assignment and instruction scheduling [HP90]. Applying these two phases separately may have major performance drawbacks. This is especially true for applications for which registers are a critical resource, and for processors with a small register set.

In this dissertation, problems related to the interaction between register assignment and instruction scheduling are analyzed and new methods are researched. This includes the following topics:

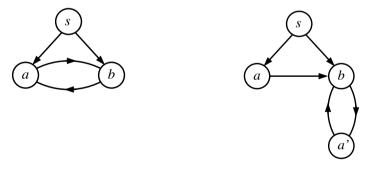

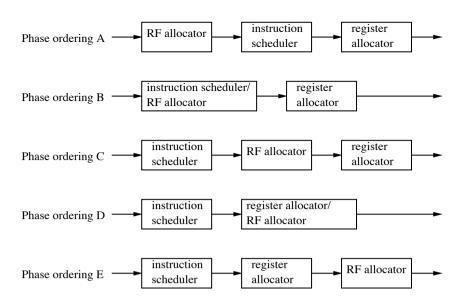

#### Evaluation of the phase ordering problem

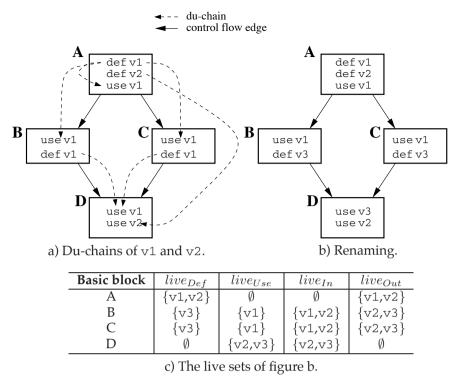

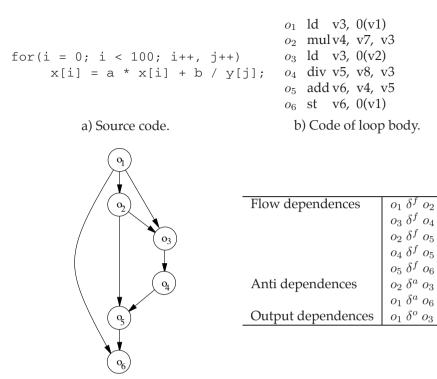

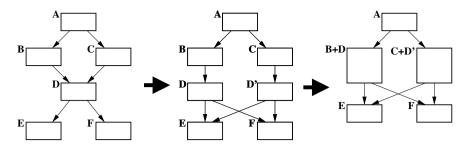

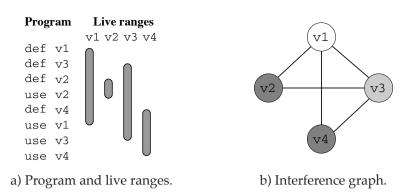

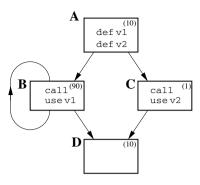

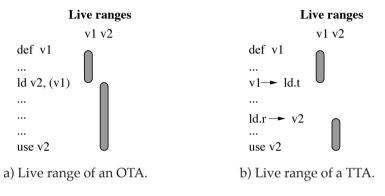

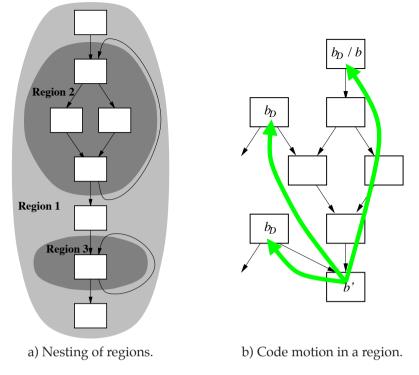

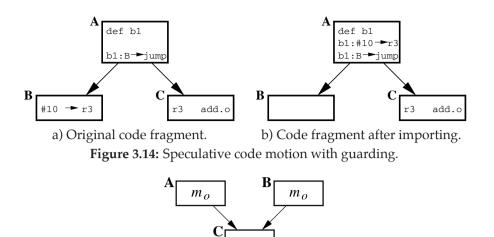

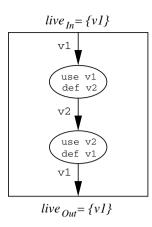

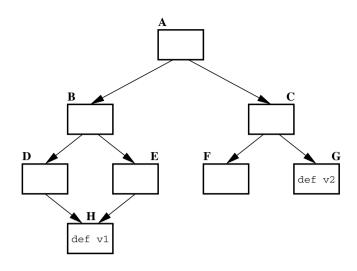

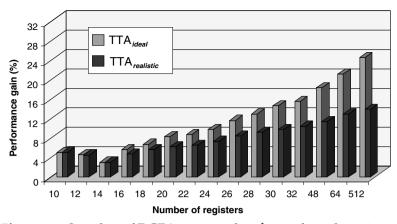

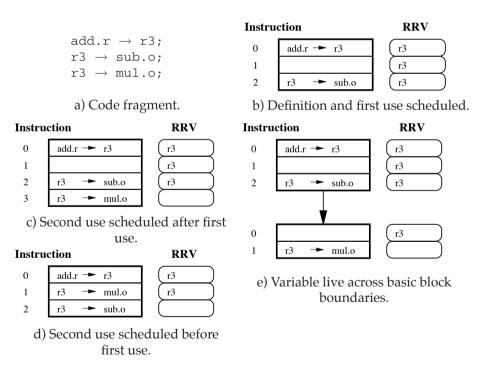

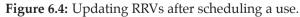

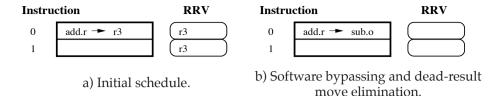

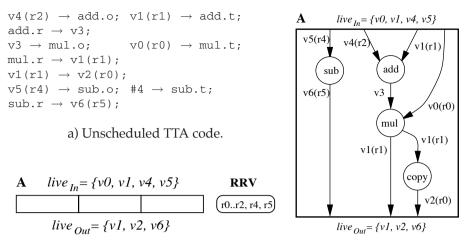

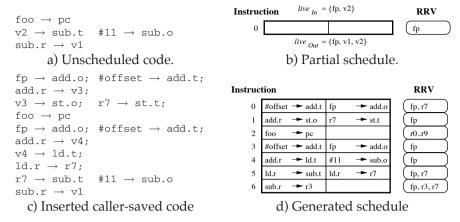

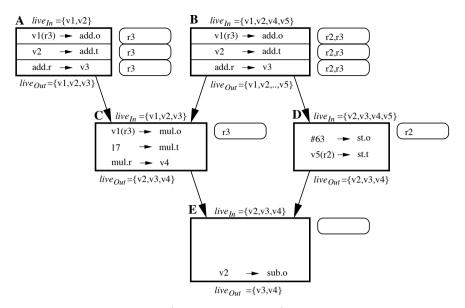

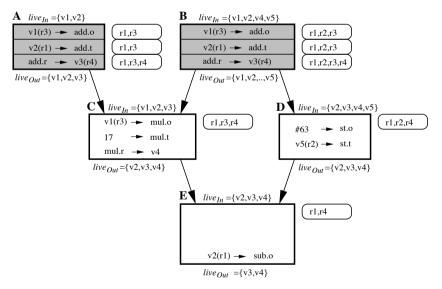

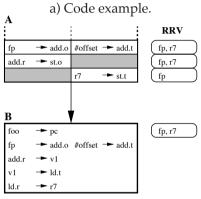

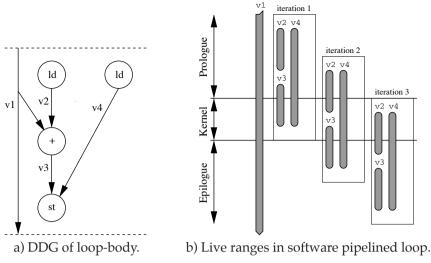

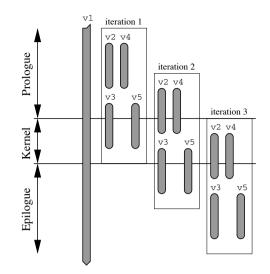

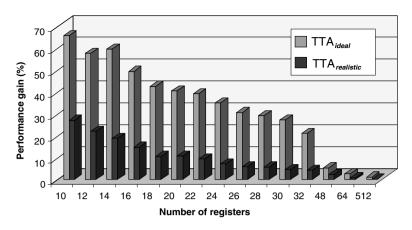

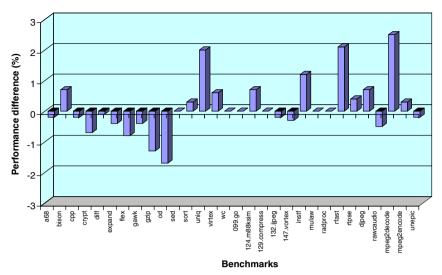

An evaluation of the phase ordering problem of instruction scheduling and register assignment is given. The instruction scheduler is responsible for creating a legal reordering of operations such that the execution time of a program is reduced and the semantics of the program are preserved. The task of the register allocator is to assign the program's variables to the registers of the processor. Instruction scheduling can be done either before or after register assignment. Consider the example in Figure 1.4, which shows three possible scenarios for scheduling the code fragment of Figure 1.4b, assuming a 2-issue processor with three registers. When register assignment is carried out before instruction scheduling (Figure 1.4c), the selection of registers may limit the possibilities to reorder the operations. This has a negative impact on the application's performance. On the other hand, when scheduling precedes register assignment, more variables become live simultaneously. For the scheduled code in Figure 1.4d no legal assignment can be found with three registers. This means that register assignment has to introduce extra operations, so-called spill code, to read and write values from memory. This lengthens the program and increases the execution time. The code example of Figure 1.4e shows the generated code when register constraints and instruction scheduling freedom are considered simultaneously. This approach results in the fastest executing code. In general, the more simultaneously issued operations, the more registers are potentially required. Therefore, it seems advantageous to address register assignment and instruction scheduling simultaneously in order to maximize ILP and to manage the registers efficiently. In this thesis, phase orderings are evaluated and TTA related issues are researched. addition, solutions proposed in the literature are discussed.

```

for(i = 0; i < 100; i++)

{

a[i] = a[i]/3 + 10 + a[i]*b[i];

b[i] = b[i]*3 + 2;

}</pre>

```

| ld  | v1  |     |     |

|-----|-----|-----|-----|

| div | v2, | v1, | #3  |

| add | v3, | v2, | #10 |

| ld  | v4  |     |     |

| mul | v5, | v1, | v4  |

| add | vб, | v5, | v3  |

| st  | vб  |     |     |

| mul | v7, | v4, | #3  |

| add | v8, | v7, | #2  |

| st  | v8  |     |     |

#### b) Code without loop control.

Instruction Scheduling

| ld  | v1  |     |     | ld  | v4  |     |    | ٦ |

|-----|-----|-----|-----|-----|-----|-----|----|---|

| div | v2, | v1, | #3  | mul | v7, | v4, | #3 |   |

| add | v3, | v2, | #10 | mul | v5, | v1, | v4 |   |

| add | v6, | v5, | v3  | add | v8, | v7, | #2 |   |

| st  | vб  |     |     | st  | v8  |     |    |   |

| ld  | r1              |     |     | ld  | r3 <sub>a</sub>   |                   |                 |

|-----|-----------------|-----|-----|-----|-------------------|-------------------|-----------------|

|     |                 |     |     | st  | r3 <sub>a</sub>   |                   |                 |

| div | r2,             | r1, | #3  | mul | r3 <sub>b</sub> , | r3 <sub>a</sub>   | , #3            |

| st  | r3 <sub>b</sub> |     |     | ld  | r3 <sub>a</sub>   |                   |                 |

| add | r2,             | r2, | #10 | mul | r1,               | r1,               | r3 <sub>a</sub> |

|     |                 |     |     | ld  | r3 <sub>b</sub>   |                   |                 |

| add | r1,             | r1, | r2  | add | r2,               | r3 <sub>b</sub> , | #2              |

| st  | r1              |     |     | st  | r2                |                   |                 |

|     |                 |     |     |     |                   |                   |                 |

## d) Register assignment after instruction scheduling<sup>2</sup>

| ld r1  |           | ld  | r2  |     |    |

|--------|-----------|-----|-----|-----|----|

| div r1 | , r1, #3  | mul | r3, | r1, | r2 |

| add r1 | , r1, #10 | mul | r2, | r2, | #3 |

| add r1 | , r3, r1  | add | r2, | r2, | #2 |

| st r1  |           | st  | r2  |     |    |

e) Integrated register assignment and instruction scheduling.

Figure 1.4: Motivating example: phase ordering problem.

10

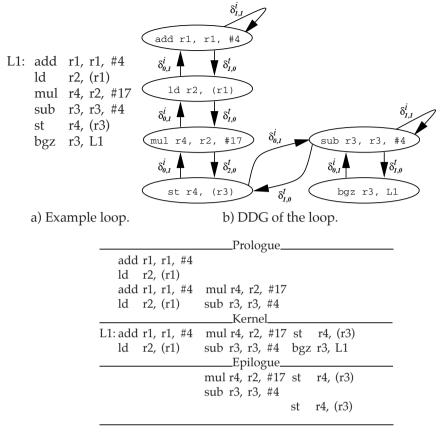

#### a) Example loop.

#### Register Assignment

|     | ,   | ,   |     |

|-----|-----|-----|-----|

| ld  | r1  |     |     |

| div | r2, | r1, | #3  |

| add | r2, | r2, | #10 |

| ld  | r3  |     |     |

| mul | r1, | r1, | r3  |

| add | r1, | r1, | r2  |

| st  | r1  |     |     |

| mul | r1, | r3, | #3  |

| add | r1, | r1, | #2  |

| st  | r1  |     |     |

|     | ,   | 7   |     |

#### Instruction Scheduling

Ļ

| ld  | r1  |     |     | ld  | r3  |     |    |

|-----|-----|-----|-----|-----|-----|-----|----|

| div | r2, | r1, | #3  | mul | r1, | r1, | r3 |

| add | r2, | r2, | #10 |     |     |     |    |

| add | r1, | r1, | r2  |     |     |     |    |

| st  | r1  |     |     | mul | r1, | r3, | #3 |

| add | r1, | r1, | #2  |     |     |     |    |

| st  | r1  |     |     |     |     |     |    |

## c) Register assignment before instruction scheduling.

<sup>&</sup>lt;sup>2</sup>The live ranges of the variables v4 and v7 are replaced by two short live ranges. Both live ranges with the index *a* originate from the live range of variable v4, while the live ranges with index *b* originate from the live range of v7.

#### Integrated register assignment and local scheduling

A new algorithm, which integrates register assignment and local scheduling, is developed. Local scheduling is one of the simplest instruction scheduling techniques. It exploits the ILP within basic blocks. A basic block is a sequence of consecutive statements in which the flow of control enters at the beginning and always leaves at the end. It will be shown that the introduced algorithm can gracefully handle situations in which insufficient registers are available. It also inserts store and reload code around procedure calls to preserve the state of the program. The state of the program consists of the contents of the registers. The results of the new introduced method are evaluated and compared with the results of early assignment methods, within the same compiler.

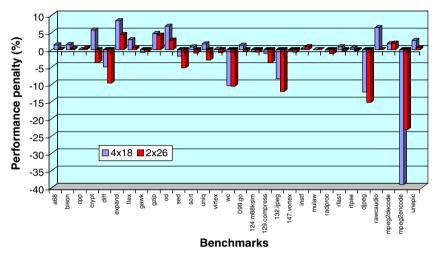

#### Integrated register assignment and global scheduling

Normally, a basic block consists of a small number of operations. This gives few opportunities to exploit ILP. Therefore, it is beneficial to exploit the ILP across several basic blocks. This increases the register requirements. We research the effectiveness of integrated assignment using a global scheduler, which exploits ILP without being restricted to basic block boundaries.

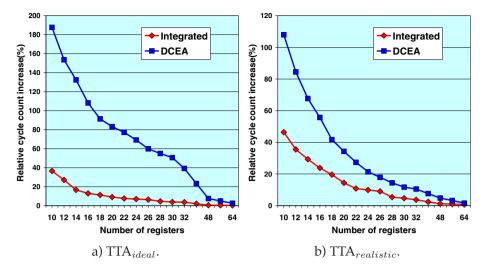

#### Integrated register assignment and software pipelining

A powerful and efficient scheduling technique for exploiting ILP in loops is software pipelining. It results in high performance, but increases the register requirements. When this scheduling technique runs out of registers, the compiler is faced with a severe problem. We present a solution based on our developed integrated register assignment and instruction scheduling technique.

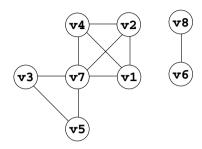

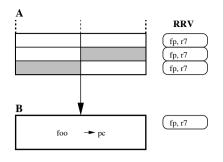

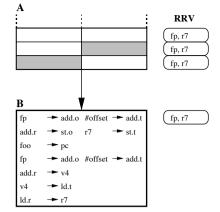

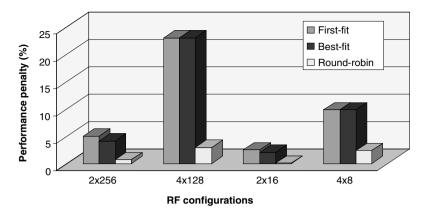

#### Efficient code generation in the context of partitioned RFs

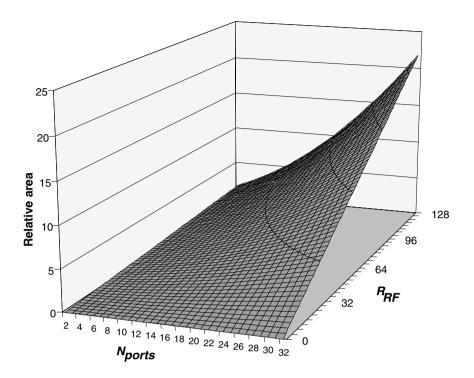

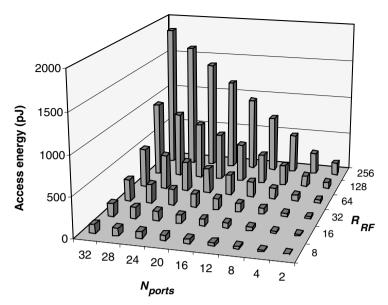

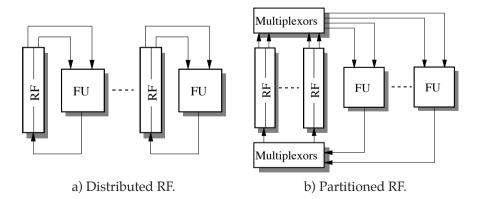

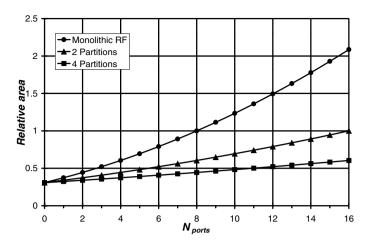

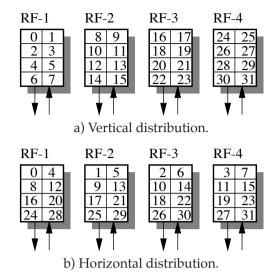

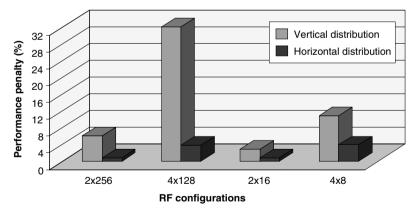

A practical implementation of high performance ILP architectures is constrained by the difficulty to build a large multi-ported RF. A solution is proposed to partition the RF into smaller RFs while keeping the total number of registers and ports equal. The advantages and disadvantages of partitioning RFs are discussed. In this dissertation, compiler techniques are proposed to generate code for TTAs containing partitioned RFs. Solutions for separated register assignment and instruction scheduling, as well as for an integrated approach are presented and the results of experiments are given.

## 1.3 Thesis Outline

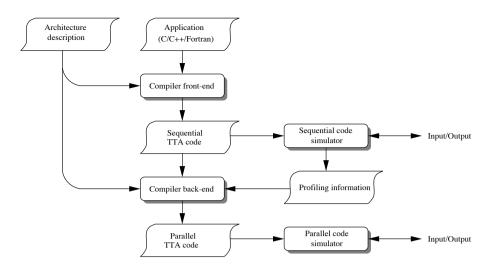

This dissertation is organized as follows. Chapter 2 describes the concept of TTAs. Starting from the VLIW concept this new class of processors is derived. In Chapter 3, the compiler framework is discussed. This includes a description of instruction scheduling and register assignment. A thorough knowledge of compiler techniques is necessary in order to comprehend the new methods. Chapter 4 discusses the environment for the experiments, including the used TTA configurations and benchmarks. The relationship between

instruction scheduling and register assignment is described in Chapter 5. It evaluates techniques from literature that tackle the phase ordering problem. The new developed method, which fully integrates register assignment and instruction scheduling in a single phase, is described in the following three chapters. Chapter 6 describes the simplest case. Register assignment is integrated with a local scheduler. A local scheduler can exploit only a modest amount of ILP; therefore, in Chapter 7, a global scheduling method is used. In Chapter 8, the application of integrated register assignment in combination with software pipelining, an even more aggressive scheduling technique, is discussed. This scheduling technique can only be applied to loops. When the amount of exploitable ILP increases, the register pressure increases also. Consequently, more registers are read and written simultaneously, which requires a large multi-ported RF. However, RFs with a high number of ports are difficult to realize. In Chapter 9, solutions are proposed to solve this problem. Two solutions are implemented: one for a phase ordering in which register assignment precedes instruction scheduling, and one method in which both phases are fully integrated. The last chapter concludes this dissertation, the findings are summarized and suggestions for further research directions are proposed.

# $\mathbf{2}$

# TTAs: An Overview

I ncreasing computing power is the subject of many research programs. The need for more powerful processors not only originates from generalpurpose computing, but also from dedicated applications. To satisfy the need for more powerful processors, computer researchers develop new computer architectures and architectural features. The most well known ILP (Instruction-Level Parallel) computer architectures are superscalars and VLIW (Very Long Instruction Word) processors. Corporaal [Cor98] developed a new computer architecture, called Transport Triggered Architecture (TTA). The research presented in this dissertation is done in the context of this architecture. Knowledge of the TTA concept is necessary to fully understand all aspects of the research presented in the remainder of this dissertation.

The TTA concept evolved from the VLIW concept. The evolution from VLIW to TTA is described in Section 2.1. The TTA's characteristics are described in Section 2.2.

### 2.1 From VLIW to TTA

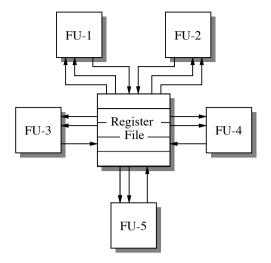

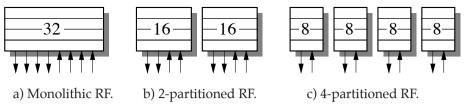

TTAs resemble VLIW architectures; both exploit ILP at compile-time. An example of the data path of a VLIW is given in Figure 2.1. This processor contains five *function units* (*FUs*) connected through a 15-ported register file (RF). An operation, performed by an FU, usually reads two values (operands), manipulates them and produces a single result. Consequently, the RF of a VLIW with *K* FUs must have 3K ports: 2K read ports and *K* write ports.

The data transport bandwidth in a VLIW is proportional with *K*. As was observed by [Cor98], VLIWs are designed for the worst case; however, it is very

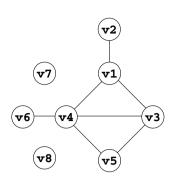

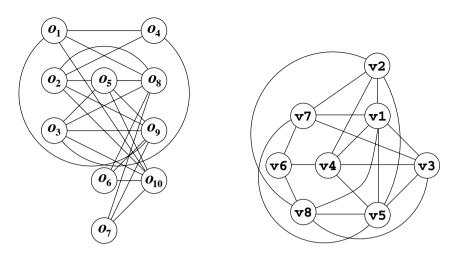

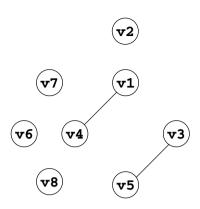

Figure 2.1: Register file connectivity within a VLIW.

unlikely that all FUs are busy simultaneously and that the data bandwidth is utilized for the full 100%. Some VLIWs have more FUs than the instruction size permits [SRD96]. For these VLIWs it is not even possible to keep all FUs busy, assuming single cycle pipelined FUs. Even when all FUs are busy, the data path is not likely to be fully used due to operations that require only one source operand or do not produce a result. The addition of a bypassing network to a VLIW may result in a better performance but decreases the utilization of the data path even further. The complexity of a fully connected bypassing network grows quadratically with the number of FUs [Cor98].

Due to the enormous effort towards the exploitation of more and more ILP, a processor architecture must be designed for scalability. However, the scalability of a VLIW is limited by the rapidly increasing complexity of the required data path; especially as its RF and bypass circuit become complex [Cor98]. This may increase the cycle time of the processor and hence degrades the performance. Furthermore, area and power consumption can become a bottleneck, which can make a processor too expensive and unsuited for specific applications.

Because the data path of a VLIW is rarely used for 100% it seems logical to share the transport capability with other FUs. This not only improves the utilization of the data path, but also decreases the number of ports on the RF. To accomplish this, an extra level of control is needed to ensure that no two transports use the same connection at the same time. This task is the responsibility of the compiler. The generated instructions have to specify transports instead of operations, hence the name of this new architecture: Transport Triggered Architecture.

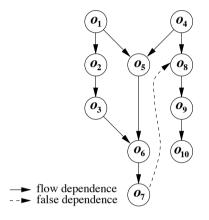

Figure 2.2: Block diagram of a TTA.

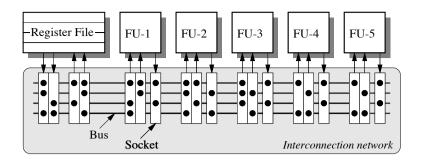

## 2.2 Transport Triggered Architectures

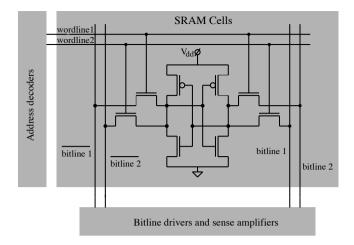

Unlike VLIWs, TTAs do not require that each FU has its own private connection to the RF. An example of the computing core of a TTA is given in Figure 2.2. An FU is connected to the RF by means of an interconnection network. It contains *buses* and *sockets*. A socket can be viewed as a gateway, which is able to pass one data item per cycle. The inputs and outputs of the FUs and RFs are connected to respectively input and outputs sockets. It is not necessary that all buses are connected to a socket. In the figure, the dots indicate to which bus a socket is connected.

FUs can be designed separately, pipelined independently and can have an arbitrary number of inputs and outputs. Examples of standard FUs are:

- *Instruction Fetch Unit:* Reads the instructions from memory and controls the flow of the program (jumps and calls).

- Integer Unit: Performs integer operations (add, subtract, etc.).

- *Floating-point Unit:* Performs floating-point operations (add, subtract, etc.).

- Logic Unit: Performs logical operations (and, or, xor, etc.).

- Load/Store Unit: Reads data from and writes data to external memory.

For some applications it is profitable to have FUs dedicated to a specific task, for instance a Multiply-Add or an RS232 - interface [AHC96]. These *Special Function Units* (*SFUs*) can also easily be integrated within the processor and exploited by the compiler.

The design space of TTAs is enormous. The number and type of FUs and RFs, and the capacity of the interconnection network can be changed easily. Performance gains can be achieved by: adding FUs, pipelining FUs, increasing the number of buses, or changing the RFs. Due to these qualities TTAs are extremely useful for Application Specific Processors (ASPs). For more details

Figure 2.3: General instruction format of a TTA.

on TTAs and prototype realizations, the reader is referred to [CM91, Cor93, CvdA93, AHC96, Cor98, TNO99].

TTAs are composed of various highly regular building blocks. These building blocks can be customized to the needs of an application. In the remainder of this section, a general description of these building blocks is given. In addition, the instruction format and TTA specific properties that allow the exploitation of ILP to a greater extent are discussed.

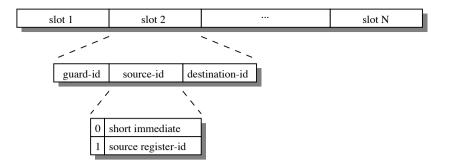

#### 2.2.1 TTA Instruction Format

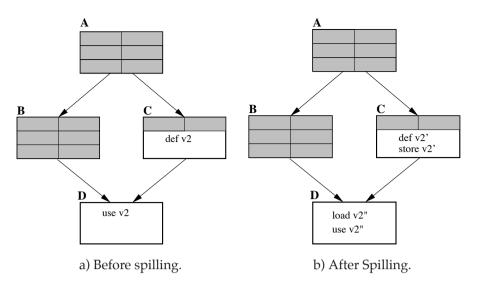

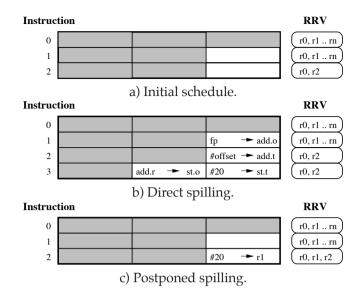

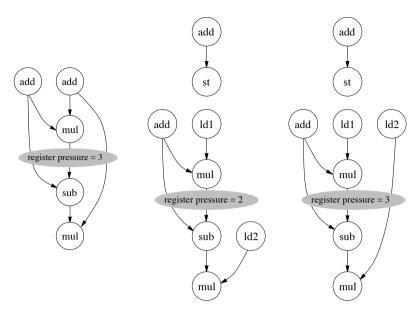

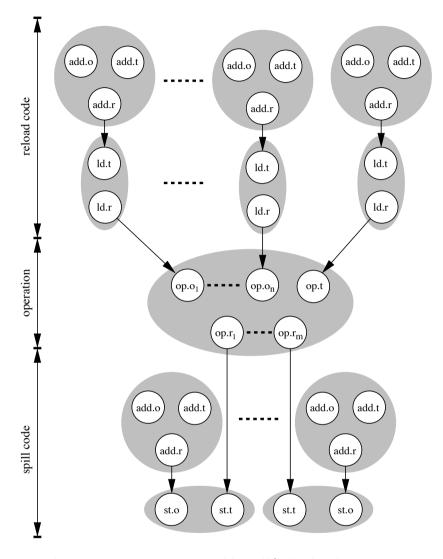

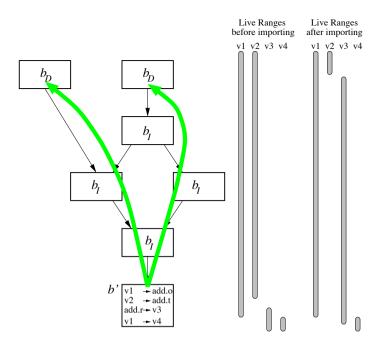

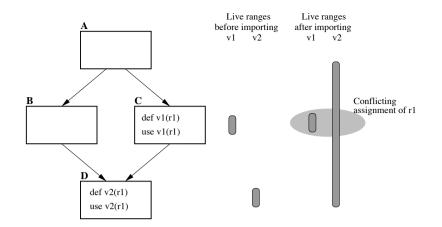

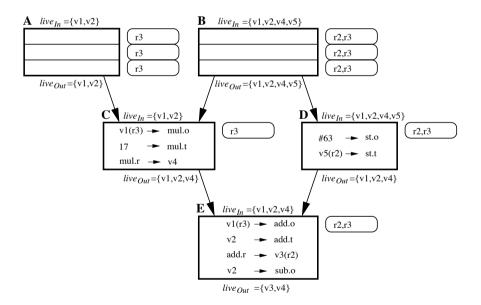

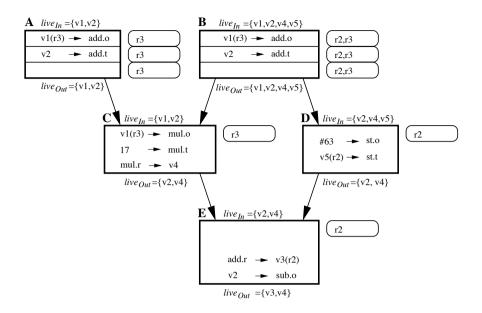

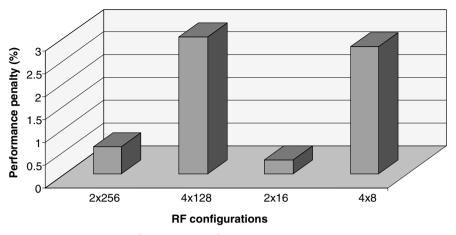

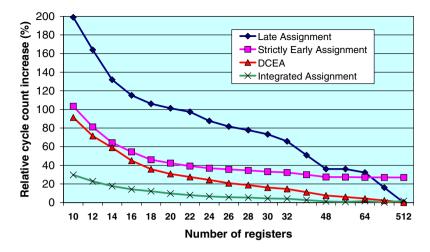

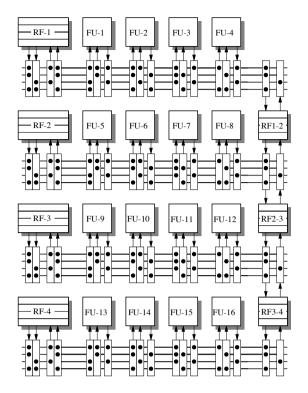

TTAs mirror the traditional programming model. Traditional architectures are programmed by specifying operations. The data transports between FUs and RFs are implicitly triggered by executing the operations. Therefore, traditional architectures are called *Operation Triggered Architectures (OTAs)*. TTAs are programmed by specifying the data transports; as a side effect, the operations are performed. Programming TTAs shows much resemblance with programming VLIWs. Instead of packing the operations in a single instruction, like VLIWs, TTAs pack multiple transports in a single instruction.