Computer Engineering Mekelweg 4, 2628 CD Delft The Netherlands http://ce.et.tudelft.nl/

## M.Sc. Thesis

## Hardware Components for Real-Time Stereo Matching: Acceleration of 3D HD TV with FPGAs

Hsiu-Chi Yeh

## Abstract

Stereo matching algorithm extracts the depth information by matching the corresponding positions on stereoscopic scenes and then computing the disparity maps. This thesis will focus on implementing a stereo matching computational flow on FPGA. In the proposed stereo matching computation flow, a dynamic programming algorithm is used to enforce the quality of the disparity map. In addition, a simple raw matching cost updating technique is used to strengthen the temporal consistency of disparity map sequences. In the stereo matching hardware design, a hardware-friendly dynamic programming processor unit is proposed, by taking advantage of the Potts model smoothness function, which penalizes disparity changes with a constant penalty. We also present a novel idea for disparity sequences compression by using run-length coding algorithm. The idea is further applied to the memory architecture design for the refinement stage of the stereo matching engine. Finally, the stereo matching engine design is integrated into IMEC 3D TV SoC for depth intensity adjustment. Several peripheral components, are developed in this project, include color space converters, video IO adaptors, and a dedicated memory hierarchy. They all support the stereo matching engine and the view synthesis engine. The proposed SoC is finally verified on EP3SL150 FPGA. The evaluation result shows that it can achieve 60 frames per second at a resolution of 1024 x 768 with an acceptable interpolated video quality.

Delft University of Technology Faculty of Electrical Engineering, Mathematics and Computer Science

## Hardware Components for Real-Time Stereo Matching: Acceleration of 3D HD TV with FPGAs Yeh Hsiu-Chi B.Sc.

### THESIS

submitted in partial fulfillment of the requirements for the degree of

### MASTER OF SCIENCE

$\mathrm{in}$

Embedded Systems

by

Hsiu-Chi Yeh born in Keelung, Taiwan

Computer Engineering Department of Electrical Engineering Faculty of Electrical Engineering, Mathematics and Computer Science Delft University of Technology

#### DELFT UNIVERSITY OF TECHNOLOGY DEPARTMENT OF MICROELECTRONICS & COMPUTER ENGINEERING

The undersigned hereby certify that they have read and recommend to the Faculty of Electrical Engineering, Mathematics and Computer Science for acceptance a thesis entitled "Hardware Components for Real-Time Stereo Matching: Acceleration of 3D HD TV with FPGAs" by Hsiu-Chi Yeh in partial fulfillment of the requirements for the degree of Master of Science.

| Laboratory<br>Codenumber |   | Computer Engineering<br>CE-MS-2012-29 |  |

|--------------------------|---|---------------------------------------|--|

| Committee Members        | : |                                       |  |

| Advisor:                 |   | Dr.ir. Gauthier Lafruit, IMEC-Leuven  |  |

| Advisor:                 |   | Dr.ir. Georgi Kuzmanov, CE, TU Delft  |  |

| Chairperson:             |   | Dr.ir. Koen Bertels, CE, TU Delft     |  |

| Member:                  |   | Dr.ir. Rene van Leuken, CAS, TU Delft |  |

ii

This master thesis research work was undertaken at the Department of NVision at IMEC-Leuven with the support from the Computer Engineering group of TU Delft. During the nine months of thesis research work, I received much support from many people. I would like to take this opportunity to express my gratitude to the people around me.

First, I must to thank my promoters, Dr. Gauthier Lafruit and Dr. Francesco Pessolano for providing me this opportunity to join the 3D TV project at IMEC. I must also thank my thesis supervisor, Dr. Georgi Kuzmanov, for his thesis work recommendation. During these nine months, the suggestions from Dr. Gauthier and Dr. Georgi Kuzmanov kept me on the right track of research decisions and provided me with all essential support.

During my nine months of research at IMEC, I was lucky to have a chance to work with a group of brilliant experts. I want to thank Ke Zhange for guiding me into the stereo matching world. Many ideas from Ke inspired me on algorithm implementation and optimization. I thank Geert Vanmeerbeeck and Eddy De Greef for all their support on building the developed environment and providing design suggestions. In this 3D TV project, we also collaborated with IMEC-Taiwans team members. I would like to thank Christine Lin and Josh Tu for all their technical support in building the SoC architecture and test works. I also appreciate the algorithm advice from CK Liao, PK Huang, and Eddy Wu. Further, the view of synthesis kernel design was supported by Professor Chang and NCTU. I would like to thank them all for their contributions. Last but not the least, I would like to especially thank Guanyu Yig. We worked day and night with each other to construct the complete system. He built the first version of the dynamic programming architecture, and my design was inspired and improved by his work. All in all, it has been my honor to work with these people.

Finally, I would like to express my gratitude to my family. Although I live abroad, they keep providing me full support. When I was struggling with the research work, they were always my best mental supporters. I would like to thank also all my friends who have shared all the joys and sorrows of my research life.

Thank You All

Hsiu-Chi Yeh

Delft, The Netherlands January 2, 2012

## Contents

| Α        | ckno                 | wledge           | ments                                                                                                                 | iii       |  |

|----------|----------------------|------------------|-----------------------------------------------------------------------------------------------------------------------|-----------|--|

| Li       | List of Figures viii |                  |                                                                                                                       |           |  |

| Li       | st of                | <b>Table</b>     | 3                                                                                                                     | ix        |  |

| 1        | Intr                 | oducti           | on                                                                                                                    | 1         |  |

|          | 1.1                  | Motiva           | ation                                                                                                                 | 1         |  |

|          | 1.2                  | Proble           | m Definition                                                                                                          | 3         |  |

|          | 1.3                  | Solutio          | on and Contribution                                                                                                   | 4         |  |

|          | 1.4                  | Overv            | iew of Chapters                                                                                                       | 6         |  |

| <b>2</b> | Bac                  |                  | nd on Stereo Matching and Related Works                                                                               | 7         |  |

|          | 2.1                  | -                | round of Epipolar Geometry and Image Rectification                                                                    | 8         |  |

|          | 2.2                  |                  | round of Disparity Map Extraction Flow: Local and Global Ap-                                                          |           |  |

|          |                      | 1                | les                                                                                                                   | 8         |  |

|          |                      | 2.2.1            | Matching Cost Computation                                                                                             | 9         |  |

|          |                      | $2.2.2 \\ 2.2.3$ | Matching Cost Aggregation                                                                                             | 9         |  |

|          |                      |                  | ming Algorithm                                                                                                        | 11        |  |

|          |                      | 2.2.4            | Disparity Map Refinement                                                                                              | 17        |  |

|          | 2.3                  | Tempo            | oral Consistency for Disparity Sequence                                                                               | 20        |  |

| 3        |                      |                  | atching Algorithm Implementation and Optimization on                                                                  |           |  |

|          |                      | dware            |                                                                                                                       | <b>21</b> |  |

|          | 3.1                  |                  | are Efficient Dynamic Programming Processor                                                                           | 22        |  |

|          |                      | $3.1.1 \\ 3.1.2$ | Dynamic Programming Algorithm and Architecture Co-design<br>Dynamic Programming - On-chip Memory Optimization - Back- | 22        |  |

|          |                      |                  | ward Path Data Compression                                                                                            | 23        |  |

|          |                      | 3.1.3            | Dynamic Programming - On-chip Memory Data Mapping                                                                     | 24        |  |

|          |                      | 3.1.4            | Dynamic Programming Processor - Hardware Architecture                                                                 | 25        |  |

|          | 3.2                  |                  | ength Coding Algorithm and Disparity Map Sequence                                                                     | 26        |  |

|          | 3.3                  | Tempo            | oral Consistency for Disparity Sequence                                                                               | 29        |  |

| 4        |                      |                  | of the proposed Stereo Matching Hardware                                                                              | 31        |  |

|          | 4.1                  |                  | Stereo Matching with Dynamic Programming - Disparity Map                                                              | <i></i>   |  |

|          |                      |                  | tion                                                                                                                  | 31        |  |

|          |                      | 4.1.1            | Parameter Exploration for Dynamic Programming Processor                                                               | 32        |  |

|          |                      | 4.1.2            | Comparison of Local and Global Stereo Matching Approaches                                                             | 34        |  |

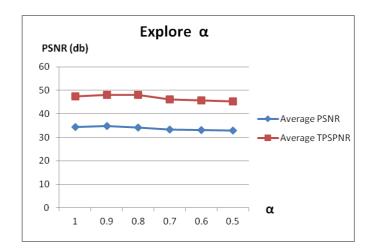

|               |        | 4.2.1 Parameter Exploration for Temporal Consistency                     | 34       |

|---------------|--------|--------------------------------------------------------------------------|----------|

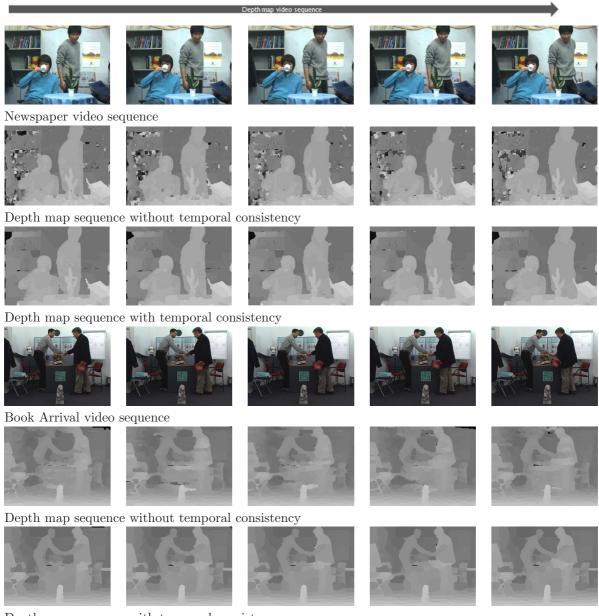

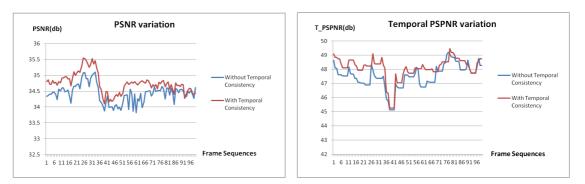

|               |        | 4.2.2 Evaluation of Temporal Consistency Function                        | 34       |

|               | 4.3    | Hardware Resource Estimation of Dynamic Programming Processor            | 35       |

|               |        | 4.3.1 Hardware Resource Estimation                                       | 35       |

|               | 4.4    | Evaluation of the Memory Architecture with Run-length Coding for Ver-    |          |

|               |        | tical Voting Processor                                                   | 37       |

|               |        | 4.4.1 Parameter Exploration for the Memory Architecture with Run-        |          |

|               |        | length Coding                                                            | 38       |

|               |        | 4.4.2 Hardware Resource Estimation and Comparison                        | 41       |

|               | 4.5    | Hardware Resource Estimation of Stereo Matching Engine on FPGA           | 41       |

|               | 4.6    | Performance Analysis of Stereo Matching Engine on FPGA                   | 42       |

| <b>5</b>      | IM     | EC 3D Depth Intensity Adjustable System with Stereo Matching             |          |

|               | on     | FPGA                                                                     | 45       |

|               | 5.1    |                                                                          | 45       |

|               |        | 5.1.1 Function Definition                                                | 45       |

|               |        | 5.1.2 Clock Domain Design                                                | 45       |

|               |        | 5.1.3 System On-chip Interconnection                                     | 47       |

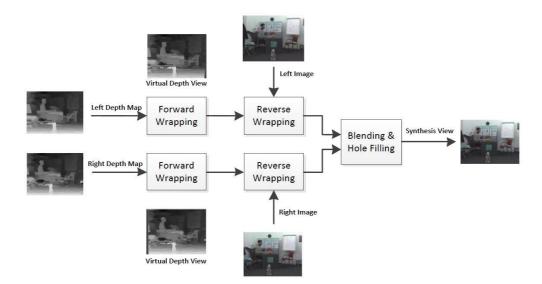

|               | 5.2    | Background of View Synthesis Engine                                      | 48       |

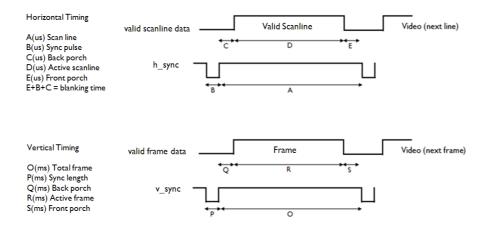

|               | 5.3    | Video Adaptor Design and Implementation                                  | 49       |

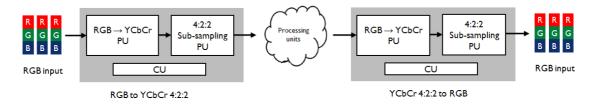

|               | 5.4    | Color Space Convertor Design and Implementation                          | 50       |

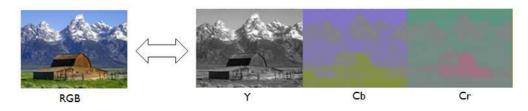

|               |        | 5.4.1 Background of Color Space Conversion                               | 50       |

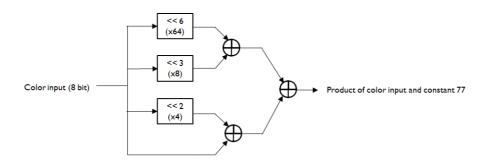

|               |        | 5.4.2 Background of Floating Point to Integer Mathematic Approaches .    | 52       |

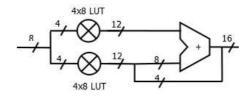

|               |        | 5.4.3 Hardware Architecture Design and Implementations                   | 53       |

|               | 5.5    | Memory Hierarchy Design and Implementation                               | 55       |

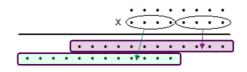

|               |        | 5.5.1 Memory Architecture Analysis for Stream Processing                 | 56       |

|               |        | 5.5.2 Memory Architecture Design for Stream Processing                   | 56       |

| 6             |        | EC 3D TV SoC Evaluation and Experimental Result                          | 67       |

|               | 6.1    | Color Space Converter Design Evaluation                                  | 67       |

|               |        | 6.1.1 Quality Evaluation                                                 | 67<br>67 |

|               | 6.9    | 6.1.2 Hardware Utilization Evalution                                     | 69<br>70 |

|               | 6.2    | Quality Evaluation                                                       | 70       |

|               | ~ .    | Hardware Utilization Estimation      Evaluation of Real-Time Performance | 71       |

|               | 6.4    | Evaluation of Real-Time Performance                                      | 73       |

| 7             |        | nclusion and Future Works                                                | 77       |

|               | 7.1    | Conclusion                                                               | 77       |

|               | 7.2    | Summary of Chapters and Contributions                                    | 78       |

|               | 7.3    | Future Work and Application Development                                  | 80       |

| $\mathbf{Bi}$ | ibliog | graphy                                                                   | 86       |

# List of Figures

| 1.1  | Focus position                                                                 | 2               |

|------|--------------------------------------------------------------------------------|-----------------|

| 1.2  | Depth perception according to visual comfort                                   | 2               |

| 1.3  | Depth adjustment processing flow                                               | 3               |

| 1.4  | Ghost effect and inaccurate disparity map                                      | 4               |

| 1.5  | disparity map sequence without temporal consistency                            | 4               |

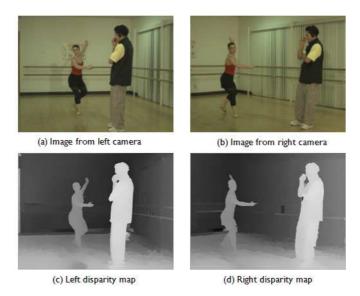

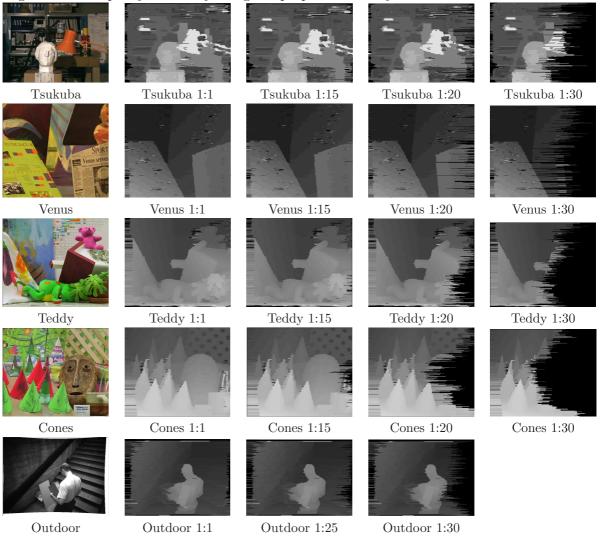

| 2.1  | Example of disparity maps                                                      | 7               |

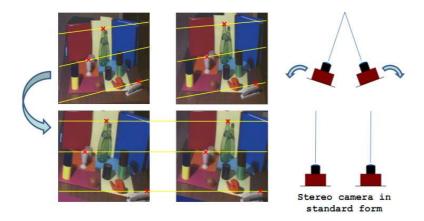

| 2.2  | Stereo image pair rectification                                                | 8               |

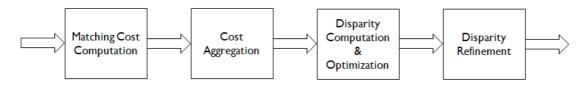

| 2.3  | Disparity map extraction flow                                                  | 8               |

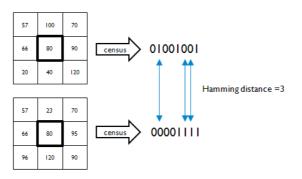

| 2.4  | Census transform and hamming distance to generate raw matching cost .          | 10              |

| 2.5  | Matching cost aggregation approaches                                           | 12              |

| 2.6  | Example of matching corresponding pixel                                        | 12              |

| 2.7  | Example of smoothness cost penlties by truncated linear model                  | 14              |

| 2.8  | Example of smoothness cost penities by linear model                            | 14              |

| 2.9  | Example of disparity map by linear model                                       | 15              |

| 2.10 | Example of disparity map by potts model                                        | 15              |

|      | Example of smoothness cost penlty by Potts model                               | 15              |

|      | Example of forward pass function                                               | 16              |

|      | Example of backward pass procedure                                             | 17              |

| 2.14 | Example of occlusion problem                                                   | 18              |

|      | Simple occlusion handling method                                               | 19              |

|      | 2D disparity voting                                                            | 19              |

|      | Two-pass 1D disparity voting                                                   | 19              |

| 3.1  | System architecture of stereo matching engine                                  | 21              |

| 3.2  | Forward pass with backward path encoding                                       | 24              |

| 3.3  | Example of backward pass with decoded path data                                | $\overline{25}$ |

| 3.4  | DP operation sequence                                                          | 25              |

| 3.5  | Example of 2-port RAM access patterns                                          | 26              |

| 3.6  | Proposed Forward Pass HW design                                                | 26              |

| 3.7  | Proposed Backward Pass HW design                                               | 26              |

| 3.8  | Disparity output from dynamic programming function                             | 27              |

| 3.9  | Circular memory architecture for Vertical Diaprity Voting processor            |                 |

|      | Proposed memory architecture with run-length coding                            | $\frac{20}{28}$ |

|      | Example of temporal consistency algorithm in dynamic programming               | <b>3</b> 0      |

| 4.1  | Parameter exploration for Dynamic Programming                                  | 33              |

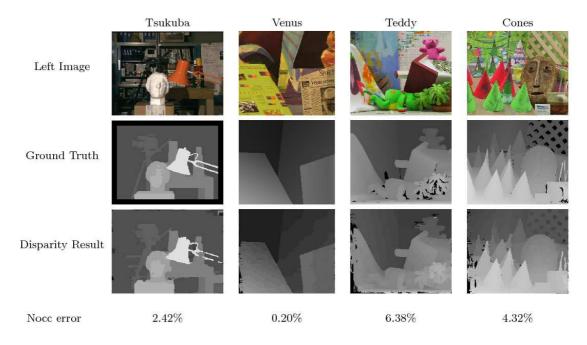

| 4.2  | Evaluation results from Middleburry's benchmark                                | 33              |

| 4.3  | Ground truth disparity maps and test disparity maps                            | 33              |

| 4.4  | Exploration of matching cost scaling parameter $\alpha$ with Book Arrival test | 55              |

|      | set                                                                            | 35              |

| 4.5  | Temporal consistency empirical evaluation                                      | 36              |

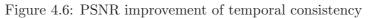

| 4.6  | PSNR improvement of temporal consistency                                | 37 |

|------|-------------------------------------------------------------------------|----|

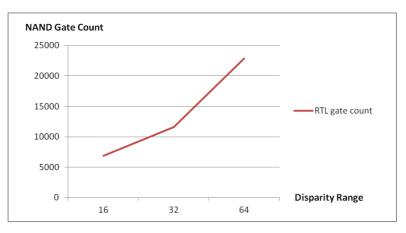

| 4.7  | RTL circuit gate count synthesis for Dynamic Programming Processor      | 37 |

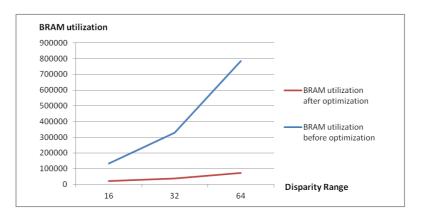

| 4.8  | On-chip memory utilization estimation for Dynamic Programming Processor | 37 |

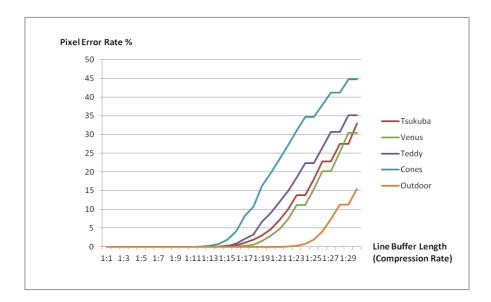

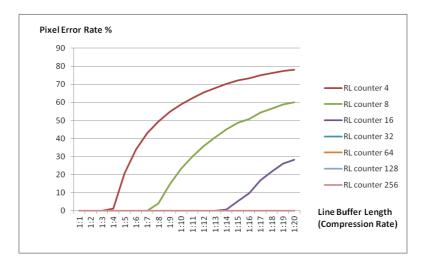

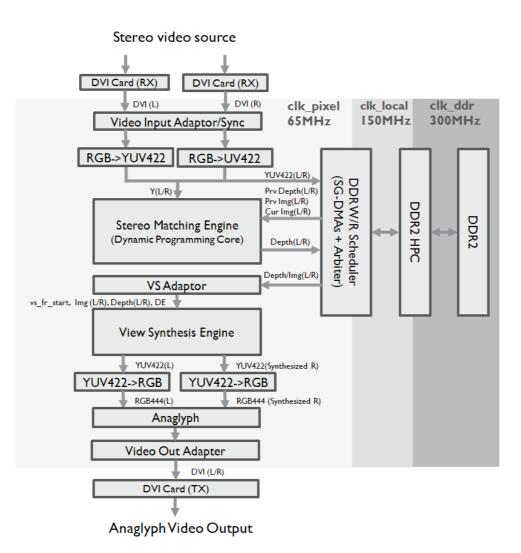

| 4.9  | Exploration of truncated line buffer length and pixel error rate        | 38 |

| 4.10 | Disparity results by using the proposed memory architecture with RLC .  | 39 |

| 4.11 | Explore the range of run length counter (Outdoor)                       | 40 |

| 4.12 | Explore the range of run length counter (Cones)                         | 40 |

|      |                                                                         |    |

| 5.1  | Dual DVI receivers scenario                                             | 46 |

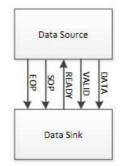

| 5.2  | Avalon Interface                                                        | 48 |

| 5.3  | High level architecture of View Synthesis Engine                        | 49 |

| 5.4  | Standard VGA signal format                                              | 49 |

| 5.5  | Example of RGB and YCbCr Format                                         | 50 |

| 5.6  | Color space conversion flow                                             | 53 |

| 5.7  | RGB to YCbCr Processor Unit                                             | 54 |

| 5.8  | Constant multiplier implementation (77) with Shift and Add/Sub archi-   |    |

|      | tecture                                                                 | 54 |

| 5.9  | Upper 4 bit nibble and lower 4 bit nibble multiplication                | 55 |

| 5.10 | Example of Look Up Table                                                | 55 |

| 5.11 | 8x8 Constant multiplier with 4x8 LUTs                                   | 55 |

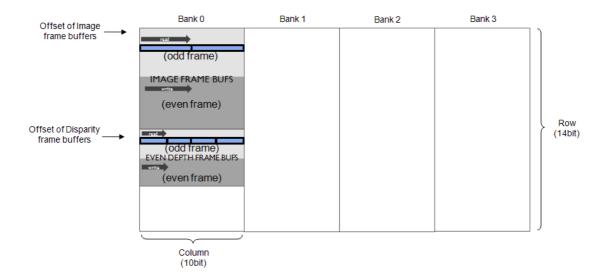

| 5.12 | Proposed Memory Hierarchy                                               | 57 |

| 5.13 | 5x5 slide window operation                                              | 58 |

| 5.14 | Example of data reuse                                                   | 58 |

| 5.15 | Proposed memory hierarchy for frame buffering                           | 59 |

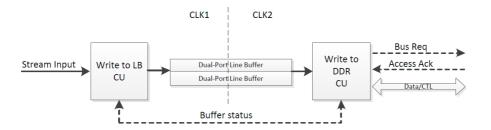

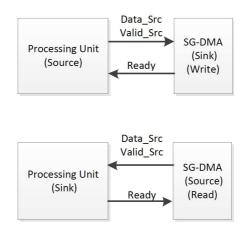

| 5.16 | SG-DMA architecture for write function                                  | 60 |

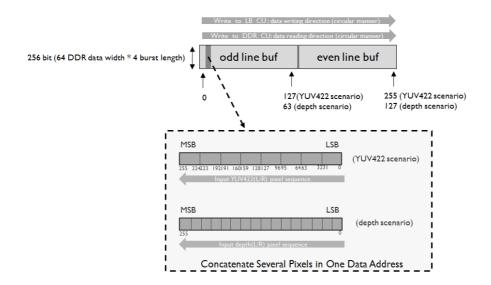

| 5.17 | Example of data concatenation                                           | 60 |

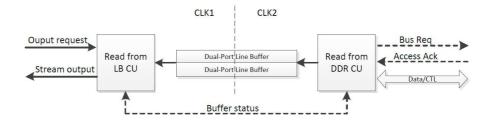

| 5.18 | SG-DMA architecture for read function                                   | 61 |

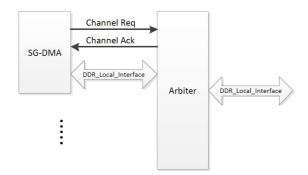

| 5.19 | The interface between SG-DMA and Arbiter                                | 62 |

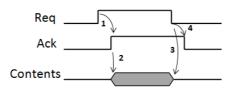

|      | Handshaking protocol between SG-DMA and Arbiter                         | 62 |

|      | Avalon stream interface between processing unit and SG-DMA              | 63 |

|      | Example of address generation pattern                                   | 65 |

|      |                                                                         |    |

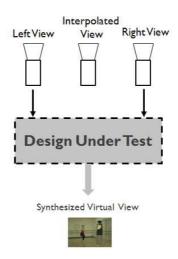

| 6.1  | Interpolated video evaluation structure for our system                  | 71 |

| 6.2  | Interpolated video evaluation structure for DERS+VSRS                   | 72 |

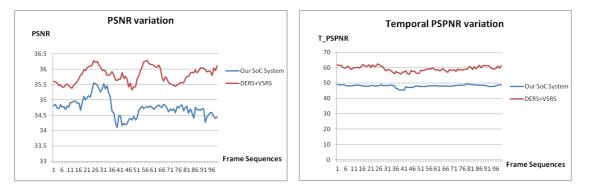

| 6.3  | Quality evaluation for Book Arrival                                     | 72 |

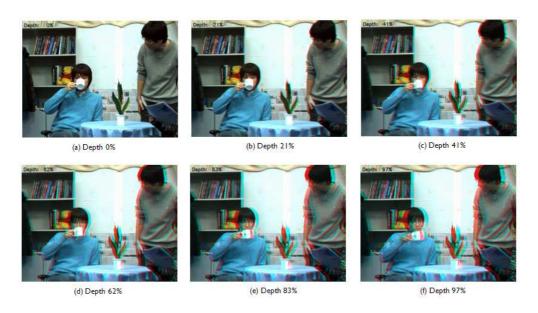

| 6.4  | Anaglyph outputs for different depth intensity                          | 73 |

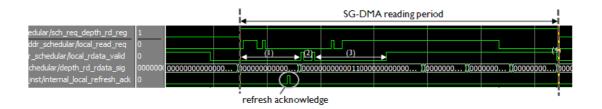

| 6.5  | Example of latencies during burst reading                               | 74 |

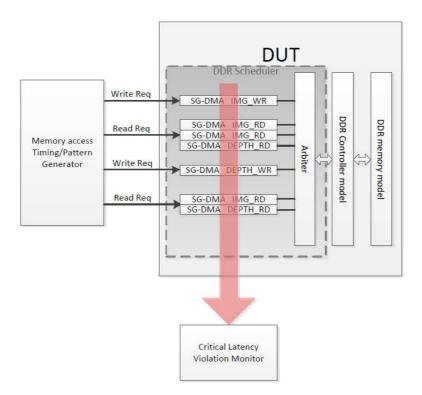

| 6.6  | Memory hierarchy evaluation environment                                 | 75 |

| $2.1 \\ 2.2 \\ 2.3$                                     | Definition of absolute difference and square difference                                                                              | 10<br>11<br>14       |

|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| $\begin{array}{c} 4.1 \\ 4.2 \\ 4.3 \\ 4.4 \end{array}$ | Hardware resource comparison of run length counter and compression rate<br>On-chip memory architecture resource utilization analysis | 41<br>41<br>42<br>43 |

| $5.1 \\ 5.2 \\ 5.3$                                     | Function definition in SoC                                                                                                           | 47<br>52<br>57       |

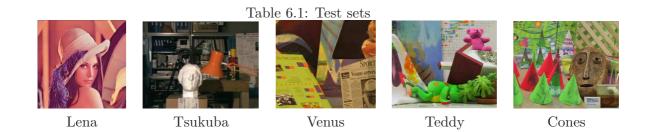

| $6.1 \\ 6.2 \\ 6.3$                                     | Test sets                                                                                                                            | 68<br>68             |

| $6.4 \\ 6.5$                                            | (1024)                                                                                                                               | 69<br>69<br>70       |

| $6.6 \\ 6.7 \\ 6.8 \\ 6.9$                              | Hardware utilization analysis of RGB to YCbCr converter                                                                              | 70<br>72<br>74<br>75 |

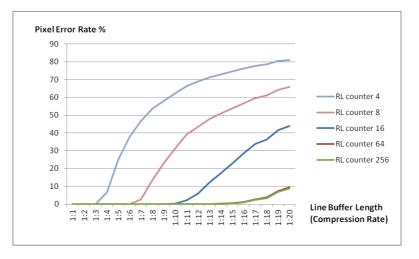

This thesis presents the researches about stereo matching algorithms and hardware implementation for a 3D TV System. The stereo matching algorithm refers to extracting depth information from two stereoscopic camera sources. The depth information, disparity value, is calculated from estimating the displacement of corresponding points on both images. The computed disparity maps can be used in the IMEC proposed depth adjustable 3D TV system for synthesizing intermediate points of views.

## 1.1 Motivation

Nowadays, 3D display technologies have become prevalent in many applications. For example, the number of movies with 3D content is growing dramatically. Besides, household entertainments such as 3D TV, 3D broadcast services and stereo cameras, etc. are gradually entering the consumer market. It is foreseeable that 3D display applications will become deeply embedded in our life in the future. Therefore, this thesis research especially interests in depth information extraction technology.

Binocular vision through our eyes is the basic way that our brain percepts object depth in real world. Because our eyes receive slightly different views, our brain can analyze the disparities and fuse the 2D information to a 3D perception. Based on the concept of binocular vision, stereoscopic video contents are generally used for 3D display.

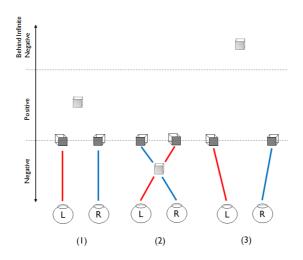

Unfortunately, 3D contents are usually incompatible with different display platforms. For example, the 3D contents for movie theaters are not always available for mobile phones. Besides, it is frequently reported that audiences easily suffer from nausea, eye strain or headache after watching 3D contents. One of the reasons of discomfort is the focus mismatch of 3D objects [48]. Figure 1.1 is an example that shows different scenarios that focus on the cube. In Scenario (1) Accommodation, the focus point of the cube concentrates on a positive region because eye-sight is nearly parallel. When the focus of object locates on a positive region, it provides best visual comfort to the viewer. In Scenario (2) Convergence, the focus point of the cube is in front of a screen, which is too close to the viewer's face. Discomfort is felt because the viewer's eye muscles are in tension. In Scenario (3) Divergence, the focus point of the cube locates far behind the screen because the focus objects are too far apart that causes eyes diverging.

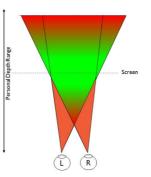

Figure 1.2 is an example that illustrates the personal depth comfort regions in a green zone. In general, the comfort zone depends on different viewers. For example, the eye distance of adult is around 6.25 cm. However, the 3D contents are usually not always applicable for children. Moreover, the comfort zone relates to screen size, view dis-

Figure 1.1: Focus position (1) Accommodation (2) Convergence (3) Divergence.

tance and display technology. It is definitely a great challenge for the 3D content vendors.

Figure 1.2: Depth perception according to visual comfort.

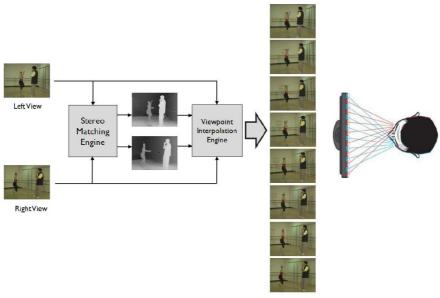

Addressing to the visual comfort, depth scaling [48] is a solution to the abovementioned problem. If the viewer observes from the in-between virtual view, heshe will perceive less depth intensity of 3D content. Therefore, IMEC provides a depth scaling solution based on this concept. The processing flow Figure 1.3 calculates the standard stereoscopic video sources captured from left and right cameras and extracts the disparity maps by Stereo Matching Engine. With the disparity maps and input stereo images, View Synthesis Engine is able to generate the in-between virtual view. Therefore, a viewer can choose an arbitrary 3D depth intensity through IMEC 3D TV system.

We are motivated to develop the IMEC 3D TV system on SoC. The proposed system contains Video Adaptors, Color Space Converters, Stereo Matching Engine, memory hierarchy, and a Viewpoint Synthesis Engine. This thesis research and design works mainly concentrate on constructing a stereoscopic processing architecture to support

Virtual Interpolated Views

Figure 1.3: Depth adjustment processing flow with stereo matching and viewpoint synthesis engine.

depth extraction for view synthesis in real-time performance. Currently, the SoC has been verified on FPGA and readied for ASIC mapping.

## 1.2 Problem Definition

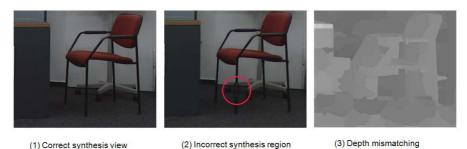

The stereo matching algorithms have been researched by the stereo matching community for many years. The most difficult handling regions are occlusion, texture less, and repetitive pattern. In the IMEC 3D TV system, generating quality disparity map is required because it affects the accuracy of the synthesized virtual view. Previous study has shown that humans are more sensitive to the edge area than the plain region. The incorrect disparity map easily generates the so called ghost effect in the synthesized view. Figure 1.4 demonstrates the synthesis error that is introduced from mismatching disparity map.

Generally, the disparity sequences suffer from a temporal inconsistency problem. Figure 1.5 demonstrates an example of inconsistent disparity map sequences. Because most stereo matching algorithms only take individual frames into the computation flow, there is a lack of links among the disparity map sequences. The disparity map sequences are easily influenced by things like camera noise, disparity map mismatching, occlusion region, luminance difference, etc. Unfortunately, a previous study [53] showed that humans are most sensitive to the inconsistent pattern (temporal noise) that flickers in 10 to 20 cycles per second. It also reports that temporal noise is even more obvious than spatial noise.

.

Figure 1.4: Ghost effect and inaccurate disparity map

Figure 1.5: disparity map sequence without temporal consistency

Hardware overhead is a problem when implementing a dyancmic programming algorithm on FPGA/ASIC. In this thesis, we chose dynamic programming algorithm to implement the global optimization function in stereo matching computation flow. Although the quality of the disparity map shows outstanding performance in Middlebury benchmark [43], tremendous hardware utilization is required for SoC implementation. If we apply scanlin-based dynamic programming algorithm in stereo matching computation flow, it will require  $O(W \cdot D_{max}^2)$  computational complexity and  $(W \cdot D_{max} \cdot D_{bit})$ memory space for the computation. The term W represents the image width, and  $D_{max}$ represents the maximum disparity range. It is preferable to keep the memory on-chip because off-chip memory introduces extra throughput and cost problems. Therefore, algorithm selection for resource optimization is one of the goals in this thesis work.

## **1.3** Solution and Contribution

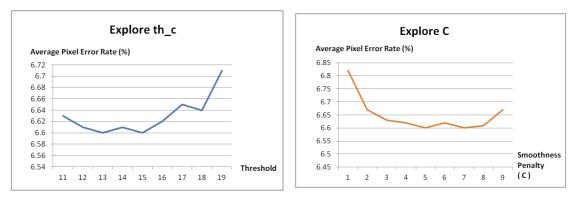

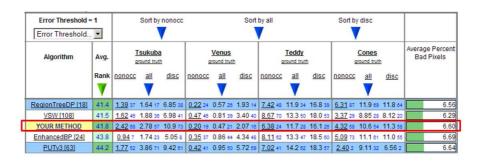

Two algorithms are applied on the design of the Stereo Matching Engine to improve the quality of the disparity map. In order to achieve a high quality in the disparity map, Dynamic programming algorithm [16] is introduced into stereo matching computation flow for global optimization. The smoothness assumption with the Potts model reserves the disparity discontinuity and also covers the texture-less region that can't be handled in a local algorithm. Then a left-and-right-check algorithm [16] and a cross-based algorithm [49] are used for disparity map refinement. The stereo matching flow shows that the above-average quality of the disparity map. According to Middlebury's benchmark [43], a 6.6% average pixel error rate is achieved based on the evaluation of four frequently used test sets. In this thesis, a couple of algorithm improvement proposals are further introduced into the stereo matching computation flow:

• A simple temporal consistency method is used to enhance the disparity map sequences by adjusting the matching raw cost based on the previous disparity map and image (luminance) information. After integrating with dynamic programming and refinement stage, the stability and quality of the disparity map sequence can be greatly improved.

Furthermore, a hardware efficient stereo matching architecture with dynamic programming algorithm is presented. In addition, a couple of memory optimization methods are further proposed to improve the hardware resource requirement:

- We choose Potts model as the smoothness function for the dynamic programming algorithm. By rewriting the energy minimize function, the computational complexity can be reduced from  $O(W \cdot D_{max}^2)$  to  $O(W \cdot D_{max})$ , and the memory consumption is reduced from  $(W \cdot D_{max} \cdot D_{bit})$  to  $(W \cdot (D_{max} + D_{bit}))$ . The term W represents the image width, and  $D_{max}$  represents the maximum disparity range. We also propose a hardware efficient memory architecture by using a single 2-Port BRAM with a sophisticated memory mapping mechanism instead of the conventional ping-pong BRAM architecture. All in all, the on-chip memory can be reduced 11 times without quality loss.

- Run-length coding algorithm is first proposed on disparity map data compression. In this thesis, it is applied on reducing the on-chip memory consumption of post processor. Our experiments shows that the compression rate can reach above 12 times with almost no loss of quality. In the proposed new memory architecture with run-length coding encoder/decoder, it achieves a 4.75 times of memory reduction rate. The high compression rate of run-length the disparity map by run-length coding shows a promising solution for disparity map compression.

To construct IMEC 3D TV SoC, we design and implement extra peripheral components to support Stereo Matching and View Synthesis Engines. Those components are encapsulated in IMEC 3D TV SoC. More specifically, they are:

- A dedicated memory hierarchy is proposed and implemented to support frame buffering for temporal consistency function. The memory hierarchy successfully cooperates with stream processors by using pre-fetch and data burst techniques.

- Color space converters are designed to perform RGB-YCbCr and YCbCr-RGB conversions for the SoC design. Two hardware efficient designs are compared and evaluated from quality, hardware consumption, and flexibility aspects.

- Video signal adaptors are designed for input sequences synchronization, memory data extraction, and output display signal generation based on VGA standards.

Finally, the system integration work is prototyped and evaluated on EP3SL150 FPGA. We integrate the designs including video adaptors, color space converters, stereo matching engine, and memory hierarchy with a view synthesis engine provided by the

research group from NCTU (National Chiao Tung University). So far, the 3D TV prototype is capable of processing up to XGA format (1024x768@60FPS 65MHz Pixel Rate) of video streams in real-time performance. Users can adjust the depth intensity of 3D contents through on-board buttons and can watch anaglyph or synthesized stereoscopic video from 2D or 3D TV through IMEC 3D TV solution.

## 1.4 Overview of Chapters

The following chapters discuss this thesis works from algorithm selection to hardware implementation. The design works cover from individual components to integrated system.

In Chapter 2, the related background of stereo matching is introduced.

In Chapter 3, a depth extraction flow is presented. Based on the depth extraction flow, we evaluate the performance and hardware complexity. Then, several techniques and proposals are introduced to optimize the disparity map sequences quality and hardware usage.

The proposals in Chapter 3 are evaluated in Chapter 4. The designs are estimated based on three aspects: image/video quality, hardware utilization, and real-time performance.

In Chapter 5, we apply the Stereo Matching Engine design on IMEC 3D TV SoC. The overview of the system architecture will first be introduced. Then we will mention about the supporting peripherals, including memory hierarchy, color space converters, and video signal adaptors.

In Chapter 6, we evaluate the proposed IMEC 3D TV SoC design for EP3SL150 FPGA platform.

In the final chapter, the thesis work is summarized. In addition, several suggestions for future work and relative applications will be mentioned.

## Background on Stereo Matching and Related Works

Stereo matching algorithm extracts the depth information from stereoscopic image pairs. The depth information refers to the displacement of corresponding points on the other image. In general, the displacement is quantified to the disparity value which is located in a so-called disparity range. Finally, the disparity map is constructed from the full-frame pixel number of disparity value. Figure 2.1 shows the disparity maps that are rendered from stereoscopic image pairs and displayed in gray scale. With the disparity map, it is possible to reconstruct a 3D scene by using triangulation method.

Figure 2.1: Example of disparity maps

There are two main classes of correspondence matching algorithms: feature-based and correlation-based. A feature-based approach refers to searching correspondence by matching sparse sets of image features. The image features are usually derived from feature-identified methods such as edge detection. The other approach, correlationbased, refers to searching for the best correlation pixel on the target image by matching the homologous pixel within disparity range. The matching image intensities are usually derived from a window of pixels. This thesis will only focus on a correlation-based approach because of its robustness and simplicity for real-time hardware implementation. In Section 2.1, the concept of Epipolar geometry is introduced as the background to a correlation-based approach. Section 2.2 sums up the correlation-based stereo matching algorithm for both local and global stereo matching approaches. In Section 2.3, we conclude with some related researches about the stereo matching for sequences.

## 2.1 Background of Epipolar Geometry and Image Rectification

Image rectification is an important step to simplify the stereo matching space from two dimensions to one dimension searching space. Because the stereo video is not always taken from the well horizontally-aligned cameras, as Figure 2.2 shows, the mapping work is based on the concept of Epipolar line geometry [15][2]. In the example, the upper two images are not taken from two perfectly aligned cameras. The yellow Epipolar lines of the left image are mapped to different positions on the right image. Therefore, the work of image rectification [42][32][6] uses the given intrinsic and extrinsic camera parameters which includes camera rotation, translation, and rotation information to align the Epipolar lines of two projected points on the new image planes.

Figure 2.2: Stereo image pair rectification [29]

## 2.2 Background of Disparity Map Extraction Flow: Local and Global Approaches

This section introduces the disparity map extracting work flow in general correlationbased approaches. Referring to Scharstein and Szeliski's taxonomy [13], a stereo algorithm generally includes four steps that are briefly summarized in Figure 2.3.

Figure 2.3: Disparity map extraction flow

PS. Local disparity computation algorithm generally performs all of steps but without global optimization in order to obtain accurate disparity map. Global disparity optimization algorithm sometimes ignore step 2 (cost aggregation) because the algorithm itself covers enough neighborhood pixel information.

The local stereo matching algorithm performs the matching computation only within a finite disparity range. In the matching cost computation step, the matching cost can be calculated from window-based matching algorithms such as sum-of-squared-difference (SSD), sum-of-absolute-difference (SAD), or census-transform (CT) [33], since the matching cost reflects the accuracy of the disparity map. Cost aggregation, which sums a region of matching cost, includes more information around its neighbor pixels. It is generally used in local algorithms. After the matching costs are derived, the disparities are computed by the winner-take-all (WTA) strategy [13]. The WTA strategy selects the displacement position which possesses minimal matching cost value. The winner displacement is regarded as the disparity value. Finally, disparity refinement techniques such as consistency check and disparity voting are implemented to increase the accuracy of disparity map. All in all, the local algorithm normally relies on enforcing the matching cost computation and cost aggregation stages.

The global algorithm optimizes the WTA strategy with an energy function which introduces a smoothness assumption. With the smoothness assumption, global optimization can handle the texture-less regions that local algorithms can't handle. However, it requires more hardware resource than the local algorithm. The state-of-art global algorithms which are based on energy minimization include graph cuts [5], belief propagation [35], and dynamic programming [16]. In this thesis, we choose scanline-based dynamic programming approach to implement the global optimization function.

## 2.2.1 Matching Cost Computation

The simplest matching cost computation is pixel-based matching cost. The pixel-based matching techniques refer to the two most common methods: absolute difference (AD) and squared difference (SD). Table 2.1 lists the definition of AD and SD [40]. However, the raw matching cost generation only involves a single pixel of information on stereo image pair. To enhance the pixel-based matching cost approach, area-based matching cost approaches [23] are proposed to improve the problems that pixel-based approaches have.

## 2.2.2 Matching Cost Aggregation

The cost aggregation step aggregates raw matching cost within a certain shape of the neighborhood region in order to increase the matching accuracy. In area-based matching cost approaches, the most commonly used techniques are Sum of Absolute Intensity Difference (SAD), Sum of Square Difference (SSD), Normalized Cross Correlation (NCC), Rank, and Census Transform. The functions are summarized in Table 2.2. In recent years, the Census Transform approach has become popular in the stereo matching community because of its robust performance. The previous research work from Chang [7], Heiko [14], Bleyer [27] show Census Transform performs outstandingly

| Matching<br>Cost Alg.                                                                                                           | Description                                                                                                                             | Definition                                           |

|---------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| AD                                                                                                                              | Absolute difference approach ag-<br>gregates the color(luminance) dif-<br>ference of reference pixels and tar-<br>get candidate pixels. | $f(u, v, d) =  I_{ref}(x, y) - I_{tar}(x + d, y) $   |

| SD Square difference approach squares<br>and aggregates the difference of<br>reference pixels and target candi-<br>date pixels. |                                                                                                                                         | $f(u, v, d) = (I_{ref}(x, y) - I_{tar}(x + d, y))^2$ |

Table 2.1: Definition of absolute difference and square difference

against other approaches in both local and global stereo matching algorithms. The advantage of census-transform is that it only includes the information about the luminance relationship of the central pixel and neighboring pixels. Since no luminance difference value is involved in cost generation, it is robust to the luminance and gamma variations of stereo sources.

In the case of Census Transform matching cost function, the raw matching cost is generated from the hamming distance of the reference pixel and the target pixel of stereo image pairs. 2.4 is an example that shows the distance (raw cost) of two census series. The hamming distance of 01001001 and 00001111 is 3 because 3 bits are unmatched. The higher the raw matching cost represents the lower similarity between reference pixel and candidate matching pixel.

Figure 2.4: Census transform and hamming distance to generate raw matching cost

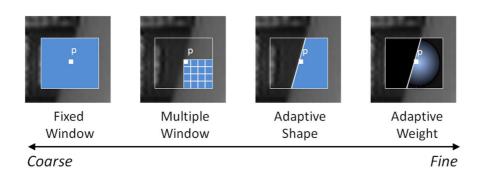

In advance, Figure 2.5 shows different cost aggregation region strategies, from coarse to fine [50]: fixed window, multiple window, adaptive shape, and adaptive weight. The fixed window approach is the simplest method. Although it possesses low computation complexity, it performs badly on boundary, slant surface, and repetitive pattern regions. The multiple windows approach [29] enhances the fixed window. A number of sub-windows are predefined to make the support region, which is not only constrained to rectangular shape. Another approach is the adaptive shape method. It partitions

### 2.2. BACKGROUND OF DISPARITY MAP EXTRACTION FLOW: LOCAL AND GLOBAL APPROACHES 11

| Matching<br>Cost Alg | Description                                                                                                                                                                                                                                                           | $Definition \ f(u,v,d)$                                                                                                                                                                                                       |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SAD                  | Sum of Absolute Difference<br>sums up the absolute differ-<br>ences in the corresponding re-<br>gion of pixels. (such as square<br>window)                                                                                                                            | $\sum_{(x,y)\in B(u,v)}  I_{ref}(x,y) - I_{tar}(x+d,y) $                                                                                                                                                                      |

| SSD                  | Sum of Square Difference<br>squares and aggregates the<br>differences in the correspond-<br>ing region of pixels. (such as<br>square window).                                                                                                                         | $\sum_{(x,y)\in B(u,v)} (I_{ref}(x,y) - I_{tar}(x+d,y))^2$                                                                                                                                                                    |

| NCC                  | Normalized Cross Correla-<br>tion. The cross correlation is<br>normalized by the mean value<br>in the block. Higher NCC<br>stands better match.                                                                                                                       | $\frac{\sum_{(x,y)\in B(u,v)}(I_{ref}(x,y)-\mu_{tar}(x+d,y))\cdot(I_{tar}(x+d,y)-\mu_{tar}(u+d,v)))}{\sqrt[2]{\sum_{x,y\in B(u,v)}(I_{ref}(x,y)-\mu_{tar}(x+d,y))^2}\cdot(I_tar(x+d,y)-\mu_tar(x+d,v))}$                      |

| Rank                 | Rank transform calculates the<br>number of neighbor pixels<br>which have the value lager<br>than the central pixel. The<br>matching cost is calculated<br>from the absolute difference of<br>the two ranks.                                                           | $\begin{split} \sum_{(x,y)\in B(u,v)}  Rank_{ref}(x,y) - Rank_{tar}(x+d,y)  \\ Rank(u,v) &= \sum_{(i,j)(u,v)} L(i,j) \\ L(i,j) &= \begin{cases} 0 \ , & I(i,j) > I(u,v) \\ 1 \ , & I(i,j) \ge I(u,v) \end{cases} \end{split}$ |

| Census               | Census Transform encodes<br>the comparison result of cen-<br>tral pixel and neighbor pix-<br>els (window) into a bit string.<br>The matching cost is calcu-<br>lated from the hamming dis-<br>tance of census bit string of<br>corresponding matching can-<br>didate. | $f(u, v, d) = \sum_{(x,y) \in B(u,v)} Hamming(Census_{ref}(x, y) - Census_{tar}(x + d, y))$ $Census(u, v) = Bitstring_{(i,j) \in R(u,v)}(I(i, j) \ge I(u, v))$                                                                |

Table 2.2: Definition of area-based matching cost functions

the image in regions with similar color intensity and aggregates costs within the similar segmentation. Cross-based approach [49] is one example of adaptive shape methods thas is proposed by Zhang. The last but the most accurate one is adaptive weight [22] [17]. It assumes that the nearest pixels with similar intensity to the central pixel share the same disparity value. Based on the assumption, the weight of the intensity difference to the central pixel is gradient based on distance. By using adaptive weight method, it helps achieve highest matching performance comparing to other methods. However, the computational complexity is obviously higher than others.

### 2.2.3 Disparity Computation and Optimization with Dynamic Programming Algorithm

There are two categories of disparity computation approaches: local stereo matching and global optimization method. Both approaches have pros and cons on computational 12 CHAPTER 2. BACKGROUND ON STEREO MATCHING AND RELATED WORKS

Figure 2.5: Categories matching cost aggregation approaches from coarse to fine.

resource and matching quality.

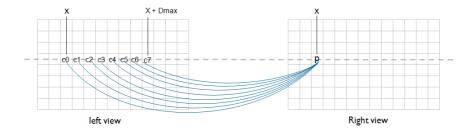

[Local Stereo Matching] The local stereo matching method computes the disparity value by selecting the disparity candidate which possesses the minimum raw cost value. This method is so-called local winner-take-all (WTA) strategy [13]. It selects the corresponding point (disparity) that has minimum raw cost. The raw costs are generated from the reference pixel and the matching target corresponding candidate pixels on the other image, using the matching cost generation/aggregation methods that were mentioned in the previous section. Then the disparity value is chosen from the disparity candidate that possesses the minimum raw cost. The distance between the reference pixel and the selected target pixel is regarded as a disparity value. Figure 2.6 is an example that illustrates matching one pixel from right image to the left image on an Epipolar line.

Figure 2.6: Example of matching corresponding pixel

## [Global Optimization]

## **Energy Function**

The global optimization algorithm computes the disparity with energy function which introduces the smoothness assumption for global optimization. An additional constraint is added to supports smoothness by penalizing changes of neighboring disparities. Therefore, the smoothness constraints can be treated as an energy minimization problem. The energy function is typically defined as 2.1.

$$E(d) = E_{data}(d) + E_{smooth}(d)$$

(2.1)

where  $d \in [0, D_{max} - 1]$

$$E_{data}(d) = \sum_{j \in N} C(j, d)$$

(2.2)

where C() is matching cost function

$$E_{smooth}(d) = \sum_{j \in N, d' \in [0, D_{max} - 1]} \lambda \cdot S(d, d')$$

(2.3)

where S( ) is smoothness function.  $\lambda$  is a scaling coefficient, which adapts to the luminance variation of adjacent pixels. It provides sharper depth discontinuity when encountering edge regions.

The first term represents the sum of matching costs for each disparity. The second term is a smoothness function, which generates a penalty value to smoothness assumption based on the disparity distance in adjacent pixels.  $\lambda$  is a scaling parameter which adapts to the luminance variation of adjacent pixels in order to provide sharper disparity discontinuouity. The smoothness function models will be further introduced in the next paragraph. The energy function is widely used in global optimization approaches such as Dynamic Programming [16], Graph Cut [5], and Belief Propagation [35]. In this thesis, we will focus on scanline dynamic programming algorithm because of its hardware-friendly trait.

The second term, smoothness cost function, produces a penalty value based on the distance of d and d' pixels' disparities. d and d' are adjacent pixels. The idea is to impose cost penalty on disparity variation in order to increase the smoothness of disparity map. The higher penalty value reduces the chance of the disparity candidate to be chosen in winner take all(WTA) step, and vice versa. Thus this increases the chance that the disparity value of d pixel remains the same as d' pixel. In the following, we will conclude the most common used smoothness function models.

In the linear model, the higher distance between the disparities of pixel d and d' generate a higher smoothness penalty. Figure 2.8 illustrates the gradient penalty costs are added on different disparity positions. This leads the disparity to be changed gradually only within small steps. The linear model performs outstanding in slanted surfaces. However, it performs badly in the disparity continuity regions (edge). Figure 2.9 is an example shows the blurd edge in the disparity discontinuity region. To solve the weakness of the linear model, a truncated constant penalty value k is introduced to improve the linear model. The penalties of high distance between the disparities of d and d' are limited to k in order to preserve discontinuous disparity regions (Figure 2.7).

Potts model preserves the discontinuous edges in disparity map by only imposing cost penalty on disparity change. Figure 2.11 illustrates the cost penalties are added

| 1able 2.3: Common used smoothness function models |                                                                                                                                                                                                                   |                             |  |

|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--|

| Model Name                                        | Smoothness Function                                                                                                                                                                                               | Computational<br>Complexity |  |

| Linear Model                                      | S(d,d') =  d - d'                                                                                                                                                                                                 | $O(D^2)$                    |  |

| Truncated Lin-<br>ear Model                       | S(d, d') = min( d - d' , k)<br>where k is user-defined truncation constant                                                                                                                                        | $O(D^2 + D)$                |  |

| Potts Model                                       | $S(d,d') = \begin{cases} 0 , & if \ d = d' \\ C , & if \ d \neq d' \\ \end{cases}$ where C is a constant introduces smoothness cost penalties                                                                     | O(D)                        |  |

| Modified Potts<br>Model                           | $S(d, d') = \begin{cases} 0, & if \ d = d' \\ C_1, & if \  d - d'  = 1 \\ C_2, & if \ otherwise \end{cases}$<br>where $C_1$ and $C_2$ introduce constant smoothness cost penalties, and $C_1$ is lower than $C_2$ | O(2D)                       |  |

| Second(Higher)<br>Order Model                     | $S(p,q,r) =  d_p - 2d_q + d_r $<br>where q and r are p's left and right neighborhood<br>pixels                                                                                                                    | $O(D^3)$                    |  |

| Truncated<br>Second Order<br>Model                | $S(p,q,r) = min( d_p - 2d_q + d_r , k)$ where k is user-defined truncation constant                                                                                                                               | $O(D^3 + D)$                |  |

Table 2.3: Common used smoothness function models

Figure 2.7: Example of smoothness cost penlties by truncated linear model

on the disparity dissimilar positions in energy function. Figure 2.10 is an example of

Figure 2.8: Example of smoothness cost penlties by linear model

Figure 2.9: Linear Model

Figure 2.10: Potts Model

a Potts model which performs superior in disparity discontinuous regions than linear model. However, the Potts model performs poorly in reconstructing slanted surfaces. To solve this weakness of Potts model, a modified Potts model introduces a lower cost penalty to trivial dissimilarity of disparities. The modification not only allows the Potts model to handle slight slanted surfaces but also permits disparity discontinuous regions.

Figure 2.11: Example of smoothness cost penlty by Potts model

The Second (higher) order model is proposed by Woodford [46], which improves the disparity map in curvature surface regions. The second order model detects slanted planes and assigns lower cost penalty to them. Besides, the truncated concept can also be applied to this model. In recent researches, this possesses the state-of-the-art disparity quality among the above mentioned models. However, the computation complexity is relatively complex than the first order model.

#### **Dynamic Programming**

Dynamic programming (DP) solves the complex problem in a coarse-to-fine manner. Since stereo matching problems can be formulated as searching the optimal disparity values within 2D image or 1D (i.e. along image row) through minimizing the energy function E(D), dynamic programming is proposed to solve the stereo matching problem. However, 2D image energy minimization problem is much more complicated than 1D energy minimization problem [41] [4] Therefore, dynamic programming in stereo matching commonly refers to the 1D scanline energy minimization problem. After the cost aggregation step, each pixel position has Dmax (maximum disparity range) number of matching cost C(j,d), where the term j represents the position on the image row (scanline) and d is defined within the disparity range. Then the DP algorithm can be computed in two steps, forward pass and backward pass, to find the optimal disparity solution for each scanline.

#### 1. Forward Pass

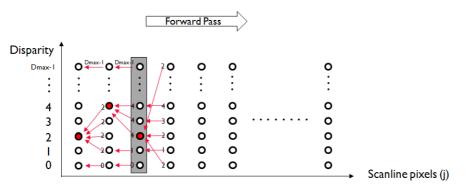

Figure 2.12: Example of forward pass function

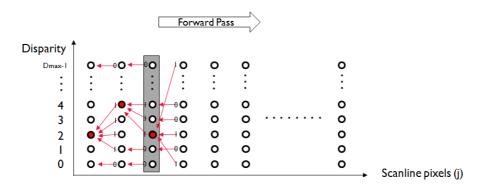

The forward pass procedure seeks optimal backward disparity entries (path) along a scanline by selecting the minimum matching cost energy with smoothness assumption. Figure 2.12 illustrates the forward pass procedure as an example. As we mentioned before, most global optimization methods can be regarded as energy minimization problems. In the formula of forward pass Equation 2.4, the second term can be represented as an energy function which includes aggregation, matching cost and smoothness penalty terms. Therefore, the second term searches for the minimum sum of aggregation, matching cost and smoothness penalty for each disparity candidate of pixel along the scanline. In each iteration, the winner of minimum aggregation cost energy (second term) will be summed with matching cost (first term) as an aggregation cost again for the next iteration of the calculation. When executing a forward pass step, the dynamic programming tree path information is stored in Backward\_Path array Equation 2.5 for a later backward pass. It is worthy of note that the minimum selection path is the information that the backward pass step is searching for but not the aggregation cost.

$C_{agg}(j,d) = C_{raw}(j,d) + \min_{j \in scanline} \ W_{d' \in [0, D_{max}-1]} \{ C_{agg}(j-1,d') + S(d,d') \}$ (2.4)

where  $d \in [0, D_{max} - 1]$  $C_{agg}(j, d)$  is a matching cost aggregation array  $C_{raw}(j, d)$  is raw cost array S() is smoothness cost function

$$Backward_Path(j,d) = arg \ min_{d' \in [0,D_{max}-1]}(C_{agg}(j-1,d') + S(d,d'))$$

(2.5)

where  $d \in [0, D_{max} - 1]$

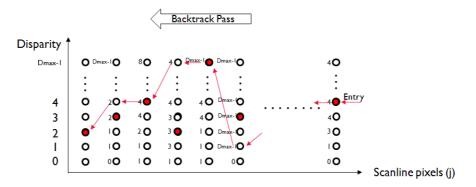

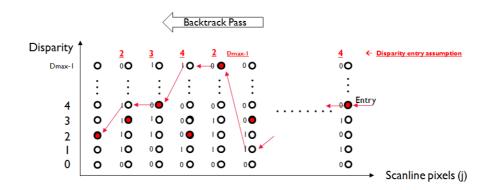

2. Backward Pass

Figure 2.13: Example of backward pass procedure

The backward pass step tracks the backward pass paths in order to obtain an optimal solution over the scanline. In the beginning of the backward pass step, the initial disparity entry of the last point is decided by the minimum winner of disparity matching cost candidates as Equation 2.6. Afterward, the backward path searching Equation 2.7 follows the backward paths from the last pixel of the scanline back to start-up pixel. Finally, the final backward pass path is regarded as the optimal disparity solution over the scanline. Figure 2.13 shows the backward pass procedure as an example.

Initially, the entry point at the end of the line (W-1, d(W-1)) is computed from:

$$d(W-1) = \arg \ \min_{d \in [0,D]} C_{aqq}(W-1,d)$$

(2.6)

where W-1 represents the last pixel of image scanline

Then we traverse backwards from j = W - 1 to j = 0 along the paths that were built in the forward pass stage iteratively:

$$d(j-1) = Backward_Path(j, d(j))$$

(2.7)

#### 2.2.4 Disparity Map Refinement

This section surveys three common used disparity map refinement algorithms [49] including Left-Right Consistency Check, Cross-based Disparity Voting, and median filter for design references.

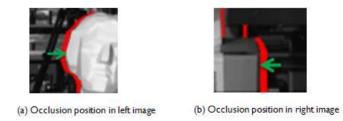

1. Occlusion handling - Left-Right Consistency Check Occlusion issue is introduced from the lack of correspondence matching position in stereo image pairs. Figure 2.14 illustrates that the marked regions are unmatchable on the stereo image pairs. There is no corresponding position on the other scene because the cover of foreground object. The same scenario happens on both scenes. In general, occlusion regions usually adhere to object boundaries.

Figure 2.14: Example of occlusion problem

Left-Right consistency check is a commonly used technique to detect the occlusion regions of disparity map. Equation 2.8 checks whether the disparity value on left disparity map shares the same disparity value with the corresponding pixel position of the right disparity map. The same scenario happens on checking the right disparity map, Equation 2.9 checks whether the disparity value on right disparity map shares the same disparity value with the corresponding pixel position on the left disparity map. If their difference is larger than a threshold, we can regard the disparity pixel is inconsistent.

Consistency check of left disparity map

$$\begin{cases} Good Disparity, & if |d_{right'}(x - d_{left}(x, y), y) - d_{left}(x, y)| \leq Threshold \\ Occlusion, & if |d_{right'}(x - d_{left}(x, y), y) - d_{left}(x, y)| > Threshold \end{cases}$$

(2.8)

Consistency check of right disparity map

$$\begin{cases} Good Disparity, & if |d_{left'}(x+d_{right}(x,y),y)-d_{right}(x,y)| \leq Threshold \\ Occlusion, & if |d_{left'}(x+d_{right}(x,y),y)-d_{right}(x,y)| > Threshold \end{cases}$$

(2.9)

Since the occlusion regions can be detected by L-R consistency check method, the simplest solution to fix them is to replace the occlusion regions by the nearest good disparity pixels. Taking the left occlusion map as an example, the occlusion part can be replaced by the nearest good disparity value from the left side. On the contrary, the right occlusion map can be replaced by the nearest good disparity from the right side. Figure 2.15 demonstrates that the occlusion regions can be replaced by the nearest good disparity values from a different direction in left and right scenes. Another solution is to replace the occlusion region by the good disparity value from the same segment. In the next item, disparity voting technique will be introduced, which are based on the idea of image segmentation.

2. **Disparity Voting** A disparity voting technique is applied based on the segmentation region method. It is assumed that the segmentation with similar

Figure 2.15: Simple occlusion handling method

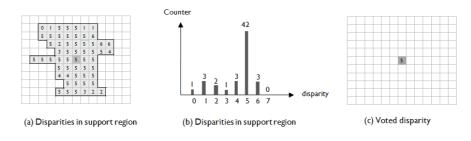

color intensity shares the same disparity value. Therefore, the disparity voting stage counts the disparity values within the support region to the central pixel into a histogram and then chose the winner as a disparity value. Figure 2.16 demonstrates an example of 2D support region voting for disparity map refinement.

Figure 2.16: 2D disparity voting

In this thesis, we apply the cross-based algorithm that was proposed by Zhang [49] to construct the support segment region. The cross-arms information is used again to include the voting members by masking. The number of disparity values within the support region are counted into a histogram. The disparity value has maximum population within the support region is regarded as the voting result. In Lu's proposed design [51], he simplified the 2D voting into two-pass 1D voting in order to reduce the computational complexity Figure 2.17. The maximum computational complexity can be reduced from  $O(N^2)$  to O(N), where N is the maximum double lengths of the cross-arm.

Figure 2.17: Two-pass 1D disparity voting

3. Median Filter Median filter is wildly used in image processing applications to eliminate the so-called pepper and salt noises. It is implemented as a  $N \times N$  window. Median filter selects the median value within the window pixels to form the final result of central pixel. It helps alleviate speckle and impulsive noises.

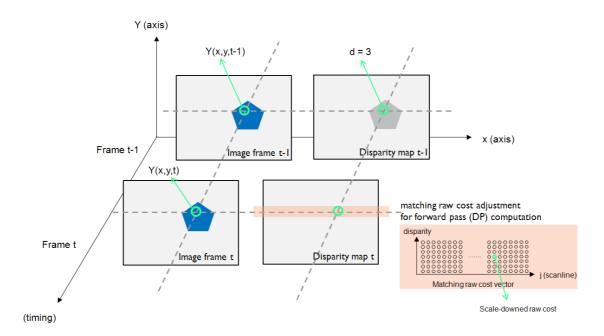

## 2.3 Temporal Consistency for Disparity Sequence

Previous researches [10][26][8] have proposed using energy minimization approach to enhance the temporal consistency of disparity map sequences. The general idea is to update the matching cost based on the information of motion detection. A disparity map generation reference software, DERS (Depth Map Reference Software), that comes from MPEG community also achieves temporal consistency by updating the cost function for Graph Cut stereo matching algorithm. The DERS defines the motion regions with pixel blocks by using mean absolute difference (MAD) method with threshold value. In the static regions, the data cost corresponding to the disparity value of the previous frame is scaled down. The result shows that the stability of disparity map sequences is enforced.

# Stereo Matching Algorithm Implementation and Optimization on Hardware

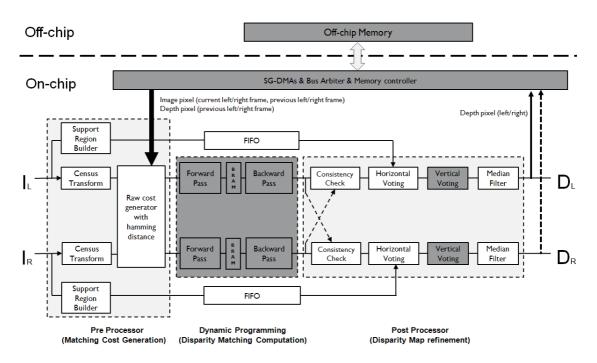

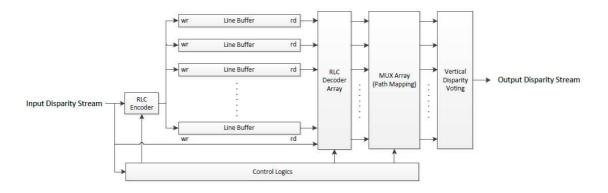

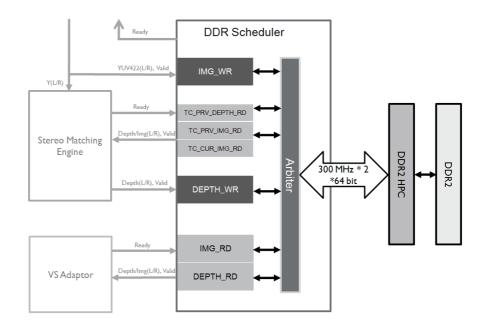

This thesis proposes a SoC architecture for stereo matching computation in Figure 3.1. The arechitecture includes three parts: pre-processor, dynamic programming, and post-processor. In the design of pre-processor, the matching costs are generated from census transform and vertical aggregation functions. In the disparity matching processor, dynamic programming algorithm is chosen for disparity map computation and optimization step. Finally, the post-processor refines the disparity maps by L-R consistency check function, cross-based disparity voting, and median filter. Beyond the stereo matching engine, a external memory hierarchy is designed to support frame bufferring function for enhancing the temporal consistency of disparity map sequences. In this thesis, we will focus on the gray regions include Dynamic Programming and Vertical Voting functions. The peripheral components include video adaptors, color space converters, and memory hierarchy will be proposed in Chapter 5 to support the stereo matching engine .

Figure 3.1: System architecture of stereo matching engine

Two proposals are implemented on Dynamic Programming and Vertical Voting functions to improve the hardware utilization. Because dynamic programming algorithm requires tremendous memory resources for storing the backward path information, this thesis will propose a hardware efficient architecture in Section 3.1. In addition, an unconventional on-chip memory architecture with run-length encoder/decoder will be proposes in Section 3.2 to reduce the on-chip memory consumption of the Vertical Voting Processor.

Temporal inconsistency is an issue in disparity map sequences. The flickering noises are caused from the lack of links between disparity maps in the stereo matching algorithm. Any reasons such as camera noise, depth mismatching, occlusion problem, etc. could cause disparity map sequences be inconsist. Therefore, Section 3.3 introduces temporal consistency algorithm into the stereo matching computation flow in order to increase the video stability.

## 3.1 Hardware Efficient Dynamic Programming Processor

This section proposes a hardware-friendly dynamic programming architecture. As in the synthesis results that have been mentioned in the beginning of this chapter, dynamic programming approach requires tremendous a memory space to store the scan line length of backward path information. Therefore, this section will implement a path data simplification idea that is inspired by Zhang Ke by taking the advantage of Potts model smoothness function. Finally, a dynamic programming architecture with Potts model smoothness function design will be presented in the last subsection.

#### 3.1.1 Dynamic Programming Algorithm and Architecture Co-design

First, the parallelism of dynamic programming algorithm is explored for hardware implementation. Equation 3.1 shows the conventional minimum energy searching method of dynamic programming with Potts model smoothness function. The computational complexity is  $O(W \cdot D_{max}^2)$  and the memory consumption is  $(W \cdot D_{max} \cdot D_{bit})$ . The term W represents the image width, and  $D_{max}$  represents the maximum disparity range. To make the hardware design be more efficient, we simply rewrite the minimum energy searching functions in Equation 3.2.

$$C_{agg}(j,d) = C_{raw}(j,d) + min_{d' \in [0,D_{max}-1]} \{C_{agg}(j-1,d') + S(d,d')\}$$

Backward\_Path(j,d) = arg min\_{d' \in [0,D-1]} \{C\_{agg}(j-1,d') + S(d,d')\}

(3.1)

where the smoothness function  $S(d, d') = \begin{cases} 0, & \text{if } d = d' \\ C, & \text{if otherwise} \end{cases}$  is potts model d and d' are adjacent disparity arrays  $\in [0, D_{max} - 1]$

j represents the pixel position of a scanline

C is constant for smoothness cost penalty

$$C_{minAssum} = min_{d' \in [0, D_{max} - 1]} \{ C_{agg}(j - 1, d') \} + C$$

$$C_{agg}(j, d) = C_{raw}(j, d) + min\{ C_{minAssum}, C_{agg}(j - 1, d') \}$$

$$Backward_Path(j, d) = arg min\{ C_{minAssum}, C_{aag}(j - 1, d') \}$$

(3.2)

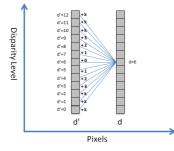

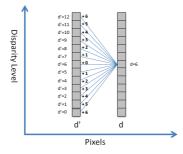

The minimum aggregated cost is computed firstly and summed up with a smoothness cost penalty to form a minimum aggregate cost assumption  $C_{minAssum}$ . Then the term,  $C_{minAssum}$ , will be compared with the original aggregation cost array  $C_{agg}(j-1,d')$ . The compared results represent the encoded backward path information which will be stored into on-chip Block RAM. It is noteworthy that only the path information, the selection information of minimum aggregation cost, is needed for the backward step but not the minimum cost itself. If the aggregate cost is less than  $C_{minAssum}$ , the backward path will point to the same disparity position. If  $C_{minAssum}$  is less than the aggregate cost value  $C_{agg}$ , the backward path will point to the corresponding disparity value of  $C_{minAssum}$ . After rewriting the forward pass equation, the computational complexity can be reduced from  $O(W \cdot D_{max}^2)$  to  $O(W \cdot D_{max})$ . The term W represents the width of image, and  $D_{max}$  represents the maximum disparity range.

# 3.1.2 Dynamic Programming - On-chip Memory Optimization - Backward Path Data Compression

The backward path information can be further simplified in order to reduce the on-chip memory requirement. In Equation 3.2, the memory requirement for storing the backward path can be formulated in Equation 3.3.

$$BRAM \quad for \quad backward \quad path(bit) = (W-1) \times D_{max} \times D_{bit} \tag{3.3}$$

where W represents scanline length  $D_{max}$  is maximum disparity range  $D_{bit}$  is the bit numbers of backward pass path information

To reduce the memory consumption, the backward path can be represented in Equation 3.4. Thanks to the characteristic of the Potts model, the backward path only has two decisions in the dynamic programming tree: to retain the same disparity or jump to the path which has the minimum sum of aggregation cost  $C_{minAssum}$ . After applying the proposed backward path reduction idea, the memory requirement for storing backward path is formulated in Equation 3.5. The memory stores the decision of the backward path in 1 bit and the path with minimum aggregation cost assumption. It uses 1 bit to store the backward path decisions, jump (1) or not jump (0) to the disparity assumption with minimum aggregation cost, instead of using full  $D_{bit}$  physical path. Equation 3.5 shows the memory requirement after the simplification. The  $D_{bit}$  term contains the maximum disparity range number of 1 bit encoded paths, and D bit is the path with the minimum aggregation cost assumption. Finally, the memory consumption complexity is reduced from  $(W \cdot D_{max} \cdot D_{bit})$  to  $(W \cdot (D_{max} + D_{bit}))$ . The term W represents the image width, and  $D_{max}$  represents the maximum disparity range.

$$Backward\_Path(j,d) = \begin{cases} 1 , & if \quad C_{minAssum} \leq C_{agg}(j-1,d) \\ 0 , & if \quad C_{minAssum} > C_{agg}(j-1,d) \end{cases}$$

(3.4)

$$Backward\_MinC\_Path(j) = arg \quad min_{d \in [0,D-1]} \{C_{agg}(j-1,d)\}$$

where  $j \in [0, \text{Image Width} - 1]$

D represents maximum disparity range

BRAM for backward path (bit) =

$$(W - 1) \times (D_{max} + D_{bit})$$

(3.5)

where W represents scanline width

$D_{max}$  is maximum disparity range

$D_{bit}$  is the bit number of backward path information

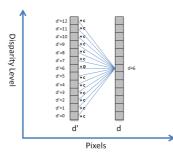

Figure 3.2 is an example shows each backward path information is encoded in one bit. The red dot represents the path with minimum aggregation cost assumption.

Figure 3.2: Forward pass with backward path encoding

In the backward pass step, the backward path information will be decoded as the Equation 3.6. When the path decision is 0, the backward entry retains the same disparity. When the path decision is 1, the backward entry will point to the path with the minimum aggregation cost assumption. Finally, Figure 3.3 is an example that shows how to decode the backward path data and traverse the procedure work.

$$d(j-1) = \begin{cases} Backward\_MinC\_Path(j), & if \ Backward\_Path(j,d) = 1\\ d(j), & if \ Backward\_Path(j,d) = 0 \end{cases}$$

(3.6)

where j represents image scanline pixels

# 3.1.3 Dynamic Programming - On-chip Memory Data Mapping

This thesis proposes using only one scanline length of 2-Port Block RAM (BRAM) to store the backward path data for the Dynamic Programming architecture. 2-Port RAM

Figure 3.3: Example of backward pass with decoded path data

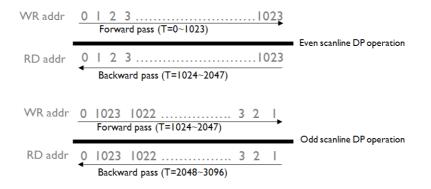

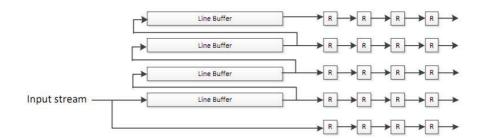

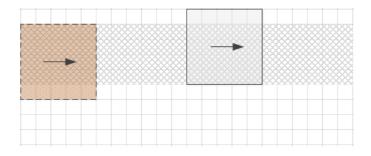

allows that writing and reading commands can operate concurrently. As Figure 3.4 shows, the forward pass loop writes the new incoming backward path data into BRAM; meanwhile, the backward pass loop reads the backward path data that was generated for the previous scanline from BRAM. So the Dynamic Programming processor can keep processing the matching cost inputs and generating disparity output simultaneously in pipeline architecture. In order to avoid data conflict problem, a relatively sophisticated address generated in a back and forth order, and the memory reading address (backward pass) is generated in a back and forth order, and the memory writing address (forward pass) will follow the reading address in 1 cycle of delay. Figure 3.5 is an example of memory address access pattern for 1024 data length of line buffer. By applying the 2-Port-RAM and a sophisticated address generator, the Dynamic Programming processor is able to achieve pipeline processing and utilize the on-chip memory efficiently.

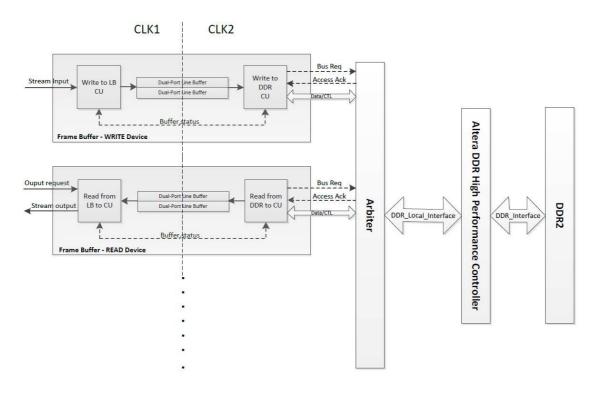

Figure 3.4: DP operation sequence

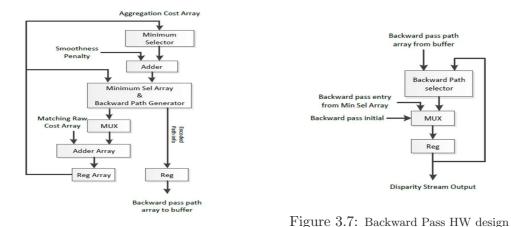

## 3.1.4 Dynamic Programming Processor - Hardware Architecture