# An Overview of Power Reduction Techniques for Single and Multicore Systems

Mahroo Zandrahimi Zaid Al-Ars

Delft University of Technology, Mekelweg 4, 2628 CD Delft, The Netherlands

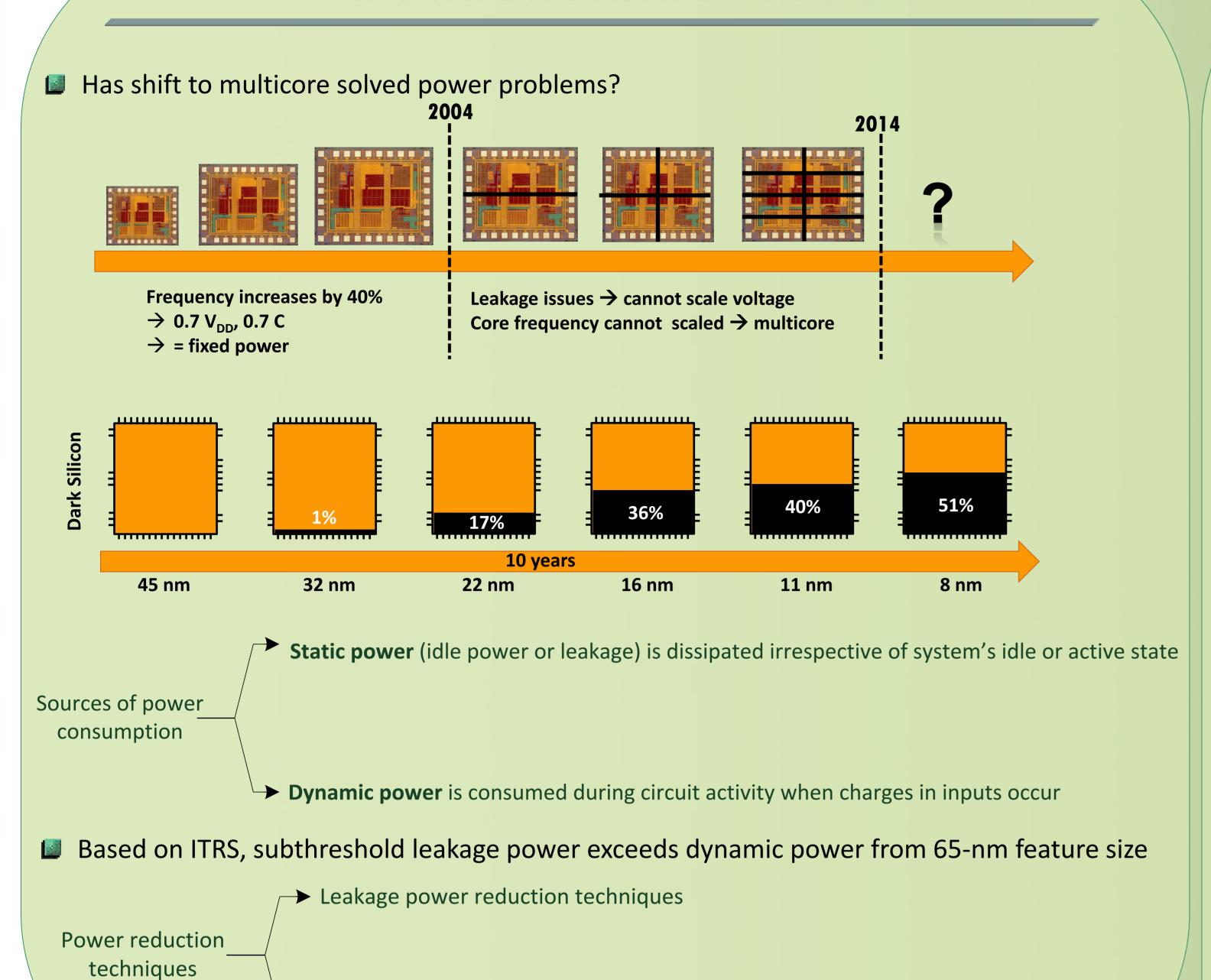

## Introduction/Motivation

# Leakage Power Reduction Techniques

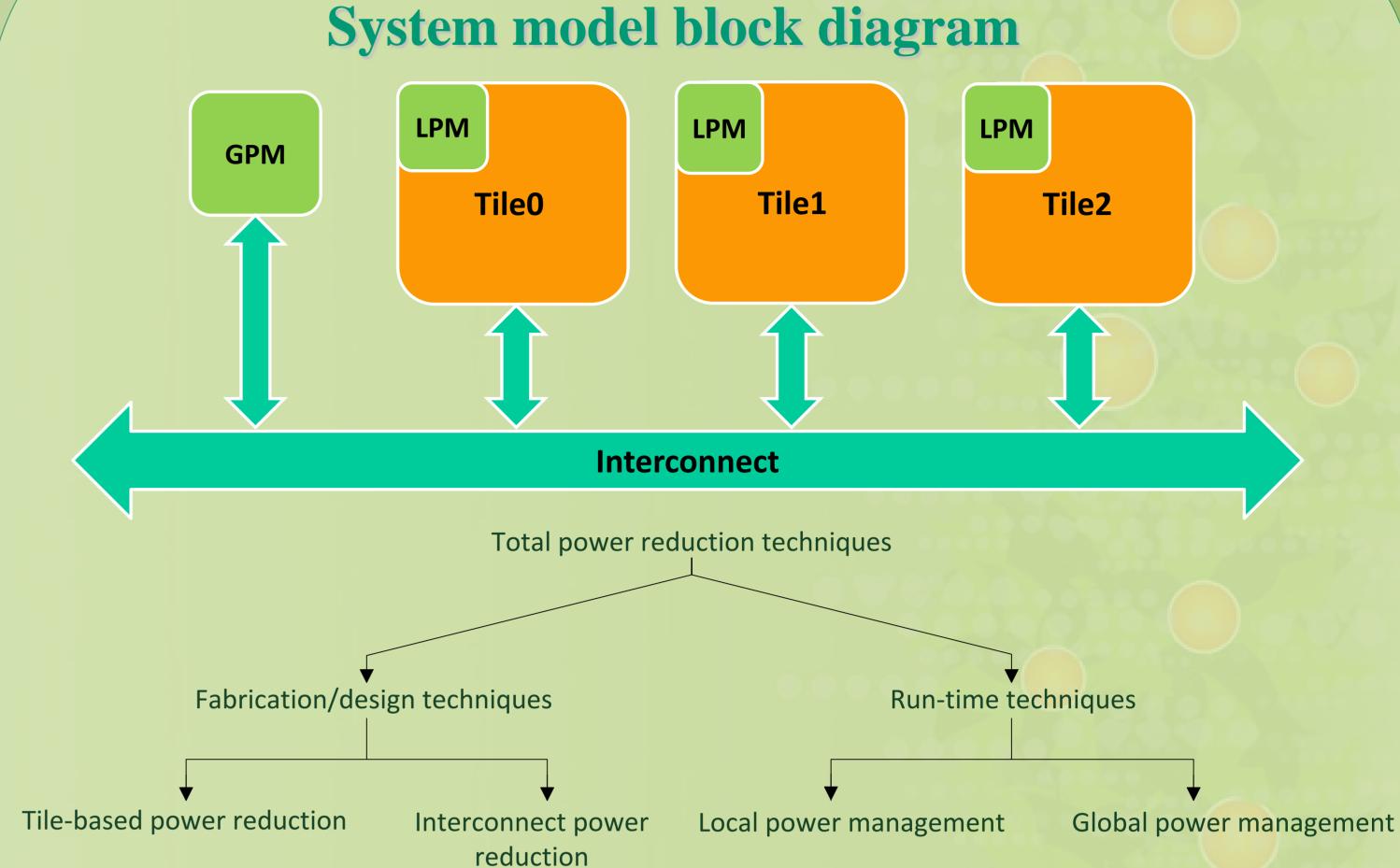

Total power reduction techniques, including both dynamic and leakage power

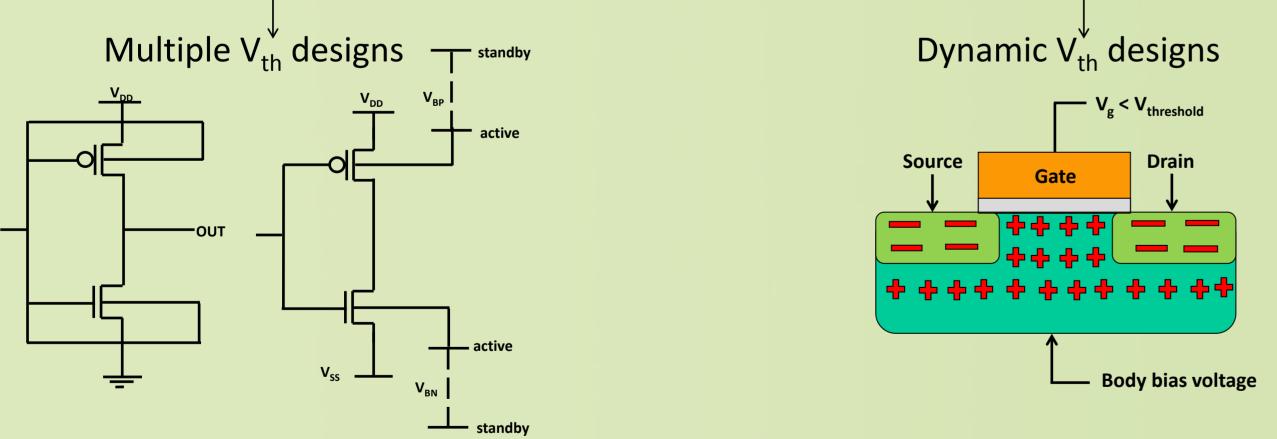

# Forced stack Input vector control W/L=3 Pull-down network 2. Increasing threshold voltage

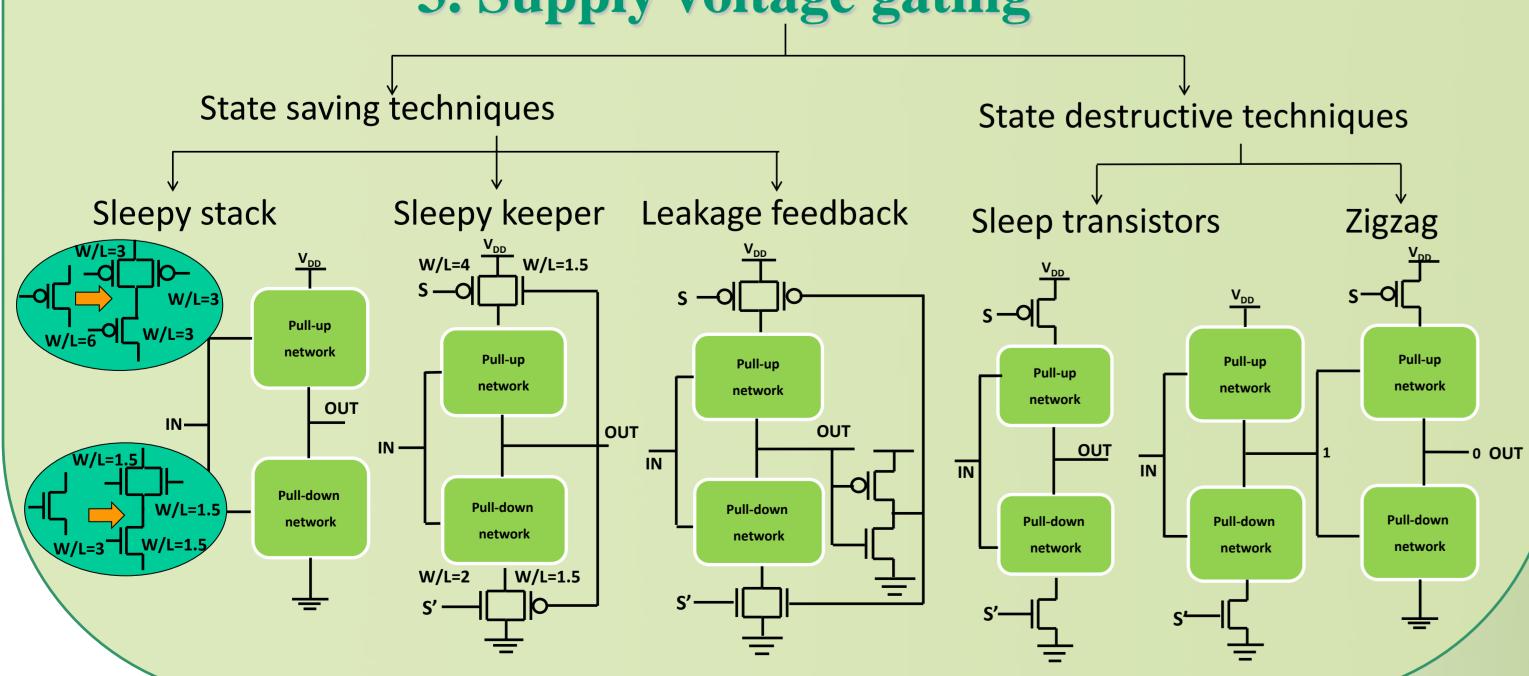

### 3. Supply voltage gating

# **Total Power Reduction Techniques**

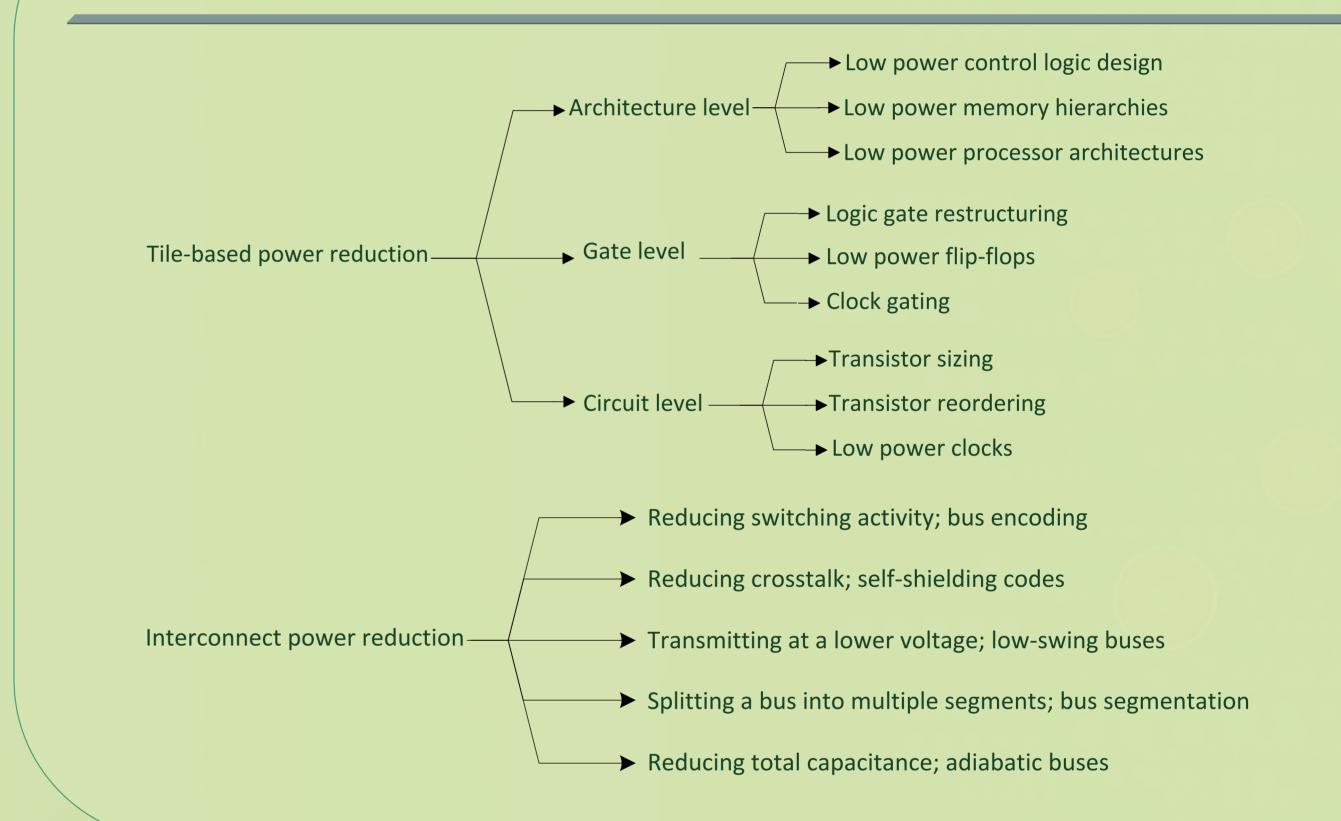

# Fabrication/design Techniques

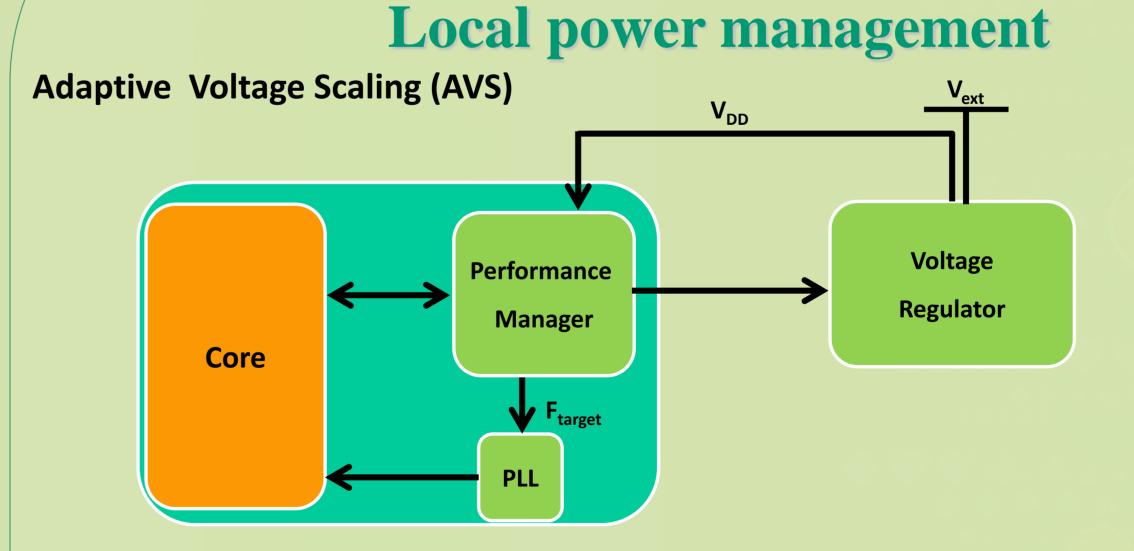

# Run-time Techniques

### Joint Adaptive Voltage Scaling and Body Biasing

- Using dynamic voltage scaling together with adaptive body biasing

- Much more effective than using any of them individually

### Global power management

AVS techniques can also be utilized for multi-core processors at different levels of granularity:

- 1) Per-chip, the supply voltage is set globally for the whole chip

- 2) Per-core, the supply voltage is set for each core, which means that only cores that require higher frequency are set to the higher supply voltage, while other cores operate at lower supply voltage or are completely shut down