# Communication Driven Mapping of Applications on Multicore Platforms

# Communication Driven Mapping of Applications on Multicore Platforms

#### **Proefschrift**

ter verkrijging van de graad van doctor

aan de Technische Universiteit Delft,

op gezag van de Rector Magnificus prof. ir. K. C. A. M. Luyben,

voorzitter van het College voor Promoties,

in het openbaar te verdedigen op donderdag 28 april 2016 om 10:00 uur

door

#### **Imran ASHRAF**

Master of Science in Embedded Systemen geboren te Mansehra, Pakistan.

This dissertation has been approved by the promotor:

Prof. dr. K. L. M. Bertels

Composition of the doctoral committee:

Rector Magnificus, voorzitter

Prof. dr. K. L. M. Bertels, Delft University of Technology, promotor

Independent members:

Prof. dr. E. Charbon, Delft University of Technology Prof. dr. A. Mendelson, Technion University, Israel

Prof. Dr.-Ing. M. Hübner, Ruhr-Universität Bochum, Duitsland Dr. F. Silla, Technical University of Valencia, Spain

Prof. dr. ir. P. F. A. Van Mieghem, Delft University of Technology, reserve member

Other members:

Dr. J. C. Le Lann, ENSTA-Bretagne, Brest, France Dr. Z. Al-Ars, Delft University of Technology

Keywords: Data-communication profiling, heterogeneous computing, binary

instrumentation, code parallelization, shadow memory

Copyright © 2016 by I. Ashraf

All rights reserved. No part of this book may be reproduced, stored in a retrieval system or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, without the prior permission of the author.

ISBN 978-94-6186-633-2

An electronic version of this dissertation is available at

http://repository.tudelft.nl.

To the children; Usman, Simra, Moiz and Fatima, for bringing joy to our family.

## Acknowledgements

Alhamdolillah, it is a matter of great pleasure and satisfaction for me to write this last part of my dissertation. Although I had my moments of ups and downs during this arduous journey, I consider myself exceedingly fortunate to have some wonderful people to keep my morale high.

First and foremost, I am grateful to Koen for providing me the opportunity to pursue my PhD research under his guidance. His experience, perseverance, bigheartedness, and consistent supervision enabled me to develop as an independent researcher. I am thankful to him for admitting me in various European projects; helping me to excel in collaboration in both academia and industry. At CE Lab, I relished working as lab designer and teaching assistant, occasional lecturer and supervisor of graduate and undergraduate students. Koen had always been able to provide ample time despite his tight and busy schedules. But above all, CE Lab should be thankful to Koen for creating a friendly environment; encouraging various social events, promoting open-door policy for all, emphasizing on coffee-breaks and brainstorming sessions. Overall, all these measures helped in increasing connectivity and friendliness among CE faculty and students.

My special gratitude goes to the members of my PhD committee for accepting their role, reading my dissertation, and providing useful feedback. I am also grateful to the graduate school for channelizing the PhD process by introducing various courses and workshops. I was the first test-case of the graduate school at CE Lab, which confused me a bit in the beginning, due to the uncertainty of the process, but eventually it ameliorated my research and personality. I also appreciate the administrative and technical support provided by Lidwina, Eef and Erik.

I am overwhelmed with gratitude to all my office mates. In initial days, Roel Meeuws and Arash Ostadzadeh assisted me with their insightful technical discussions. Later on, I joined Hamid, Nauman, and Nader, who always engaged me with exciting discussions and debates. Moreover, I am thankful to Vlad for his useful and encouraging contribution throughout my PhD. Vlad has a remarkable experience in tool development which really helped me. In particular, I want to mention Mota for being a great friend in all thick and thin. He is a wonderful person who is always ready to help, even when help is not needed. :)

I am also grateful to Mota and Faisal for the time taken to proof-read my papers and parts of thesis by providing useful comments, feedback, and suggestions. I am also thankful to the rest of CE fellows for being wonderful colleagues. One cannot forget Marius and Mihai for organizing the weekly CE football event.

I would also like to thank all my Pakistani friends in Delft, especially the senior PhD fellows — Hasham, Husnul Amin, Mehfooz, Laiq, and Hamayun — for supporting me like their younger brother. I am also grateful to my friends Faisal, Seyab, Fakhar, Umer Altaf, Muhammad Nadeem, Sajjad Sandilo, Di Cao, Haroon Sadiq, Shakeel and their families for all the gatherings, dinners, card games and appreciation of my cooking prowess. I never felt away from home. Thanks to the members of Delft Cricket Club, Shah G, Patel the great, Fahim, Usama the saddar, Umer Ijaz, Tabish, Atif, Ragu, Ram, Rahul, JK and many more for enjoyable cricket matches.

I must also appreciate my UET friends Saad, Moeen and Shoaib for always being there for me in low times. I am especially thankful to Sadi, who has been my best buddy since times immemorial. I am also thankful to MaanJi for her affection and prayers throughout my studies.

On this important juncture of my life, I am sure that nobody in the world will be as happy as my parents; my Ammi and Abbu g. You have sacrificed all your comforts to see me successful. I can never thank you enough. I am also thankful to my brothers and sisters for taking care of my parents while I was away from home for such a long time.

Last but not least, my special thanks and admiration go to Sonia, Usman and Fatima. Sonia! I do not have words to express my appreciation towards you. Without you, I would not have had the peace of mind to work. I thank you for your understanding and cooperation especially during the busy times of my PhD process. Usman and Fatima, thank you so much for bringing joy and happiness to my life. Your hugs and smiles imparted the right energy to maintain momentum in my research.

Imran Ashraf March 23, 2016 Delft, The Netherlands

## Contents

| Li | st of | Acronyms                                              | xiii |

|----|-------|-------------------------------------------------------|------|

| 1  | Intr  | roduction                                             | 1    |

|    | 1.1   | Background                                            | . 1  |

|    |       | 1.1.1 Application Partitioning                        | . 2  |

|    |       | 1.1.2 Classes of Parallelism                          | . 3  |

|    |       | 1.1.3 Classes of Parallel Architectures               | . 3  |

|    |       | 1.1.4 Heterogeneous Computing                         | . 4  |

|    |       | 1.1.5 Profilers                                       | . 4  |

|    |       | 1.1.6 Memory Profilers                                | . 5  |

|    |       | 1.1.7 Data-Communication Profilers                    | . 6  |

|    | 1.2   | Problem Overview                                      | . 8  |

|    | 1.3   | Research Questions                                    | . 13 |

|    | 1.4   | Dissertation Contributions                            | . 14 |

|    | 1.5   | Dissertation Organization                             | . 14 |

| 2  | Bac   | kground and Related Work                              | 17   |

|    | 2.1   | Introduction                                          | . 17 |

|    | 2.2   | Memory Profilers based on Profiling Objective         | . 18 |

|    |       | 2.2.1 Memory Profiling for Memory-access Optimization | . 18 |

|    | 2.3   | Memory Profilers based on Input Application           | . 24 |

|    |       | 2.3.1 Profiling Sequential Applications               | . 24 |

|   |      | 2.3.2 Profiling Parallel Applications                        | 24 |

|---|------|--------------------------------------------------------------|----|

|   | 2.4  | Memory Profilers based on the Profiling Technique            | 24 |

|   | 2.5  | Comparison of Data-Communication Profilers                   | 26 |

|   |      | 2.5.1 Comparison of the Generated Profiles                   | 28 |

|   |      | 2.5.2 Overhead Comparison                                    | 29 |

|   | 2.6  | Discussion and Recommendations                               | 31 |

|   | 2.7  | Conclusion                                                   | 31 |

| 3 | MCI  | PROF: Memory and Communication Profiler                      | 33 |

|   | 3.1  | Introduction                                                 | 33 |

|   | 3.2  | Related Work                                                 | 34 |

|   | 3.3  | Practical Considerations                                     | 36 |

|   | 3.4  | MCPROF: Memory and Communication PROFiler                    | 36 |

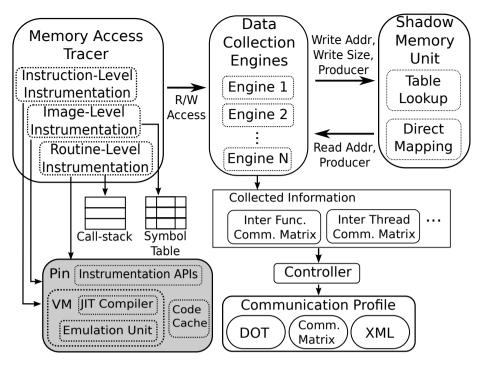

|   |      | 3.4.1 Memory Access Tracer                                   | 36 |

|   |      | 3.4.2 Data Collection Engines                                | 37 |

|   |      | 3.4.3 Shadow Memory                                          | 38 |

|   | 3.5  | Case-study                                                   | 40 |

|   |      | 3.5.1 Implementation without Data-communication Optimization | 41 |

|   |      | 3.5.2 Optimization of Data-communication                     |    |

|   | 3.6  | Experimental Results                                         | 45 |

|   | 3.7  | Overhead Comparison with Existing Profilers                  | 46 |

|   |      | Conclusion                                                   | 47 |

| 4 | Prof | file Driven Application Parallelization                      | 51 |

| - |      | Introduction                                                 |    |

|   |      | Background and Related Work                                  |    |

|   | 1.4  | Davistouria and related work                                 | 04 |

|   | 4.3                               | Parall                | lelization using Existing Commercial Compilers                                                                 | 52                         |

|---|-----------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------|----------------------------|

|   |                                   | 4.3.1                 | CC1                                                                                                            | 53                         |

|   |                                   | 4.3.2                 | CC2                                                                                                            | 54                         |

|   |                                   | 4.3.3                 | Lessons Learned                                                                                                | 55                         |

|   | 4.4                               | MCPr                  | of-xpu Semi-automatic Approach                                                                                 | 55                         |

|   |                                   | 4.4.1                 | Profiling The Sequential Application using MCProf                                                              | 56                         |

|   |                                   | 4.4.2                 | Granularity Adjustment                                                                                         | 58                         |

|   |                                   | 4.4.3                 | Parallelization Using xpu                                                                                      | 59                         |

|   | 4.5                               | MCPF                  | ROF-XPU Parallelizing Framework                                                                                | 62                         |

|   |                                   | 4.5.1                 | ROSE Compiler                                                                                                  | 62                         |

|   |                                   | 4.5.2                 | MCPROF Extensions                                                                                              | 63                         |

|   |                                   | 4.5.3                 | MXIF Generator                                                                                                 | 63                         |

|   |                                   | 4.5.4                 | Case-study                                                                                                     | 64                         |

|   | 4.6                               | Concl                 | lusion                                                                                                         | 66                         |

| 5 | Data<br>form                      |                       | munication Optimization for Accelerator-based Plat-                                                            | 69                         |

|   | 5.1                               | Case                  | Study 1: Software-based Optimizations                                                                          | 70                         |

|   |                                   | 5.1.1                 | Research Context and Experimental Setup                                                                        | 70                         |

|   |                                   | 5.1.2                 | Mapping Steps                                                                                                  | 70                         |

|   |                                   |                       | Erropins antal Dagatta                                                                                         | 73                         |

|   |                                   | 5.1.3                 | Experimental Results                                                                                           |                            |

|   | 5.2                               |                       | Study 2: Hardware-based Optimizations                                                                          |                            |

|   | 5.2                               | Case                  | -                                                                                                              | 74                         |

|   | <ul><li>5.2</li><li>5.3</li></ul> | Case 5.2.1 Case-      | Study 2: Hardware-based Optimizations                                                                          | 74<br>75<br><del>n</del> - |

|   |                                   | Case 5.2.1 Case-aware | Study 2: Hardware-based Optimizations  Design Choices  study 03: Evaluation Methodology for Data Communication | 74<br>75<br>n-<br>77       |

|    |       | 5.3.3 Evaluation of Multi-objective Task Clustering Algorithm | 80  |

|----|-------|---------------------------------------------------------------|-----|

|    |       | 5.3.4 Experimental Results                                    | 82  |

|    | 5.4   | Conclusions                                                   | 85  |

| 6  | Con   | clusion and Future Work                                       | 87  |

|    | 6.1   | Conclusion                                                    | 88  |

|    | 6.2   | Future Research Directions                                    | 89  |

| Bi | bliog | graphy                                                        | 91  |

| Su | mma   | ar <del>y</del>                                               | 101 |

| Sa | men   | vatting                                                       | 103 |

| Pu | blica | ations                                                        | 105 |

| Cu | rric  | ulum Vitæ                                                     | 107 |

## List of Acronyms

| API   | Application Programming Interface54                                         |

|-------|-----------------------------------------------------------------------------|

| BRAM  | Block RAM, a local block of RAM on FPGA70                                   |

| CPU   | Central Processing Unit                                                     |

| DSP   | Digital Signal Processor or Digital Signal Processing4                      |

| ELF   | Executable and Linkable Format, formerly known as Extensible Linking Format |

| FPGA  | Field Programmable Gate Array4                                              |

| GPP   | General-Purpose Processor70                                                 |

| GPU   | Graphical Processing Unit3                                                  |

| GPGPU | General Purpose Computing on GPUs4                                          |

| PE    | Processing Element77                                                        |

| FLOPS | Floating Point Operations Per Second                                        |

| PCIe  | Peripheral Component Interconnect Express11                                 |

| NoC   | Network on Chip74                                                           |

1

### Introduction

The growing demand for processing is being satisfied by the growing number of homogeneous and heterogeneous processing cores in a computing platform. However, this trend goes hand-in-hand with issues pertaining to program parallelization, application partitioning, deep memory hierarchy, limited communication bandwidth, power consumption, etc. Some of these problems could be alleviated by utilizing tools to unleash the performance of these emerging computing systems. In this chapter, we present current computing trends and describe the basic concepts required to understand the questions raised in the dissertation. Subsequently, we discuss some opportunities offered by these multicore platforms and highlight the main challenges in the efficient utilization of these platforms. Thereafter, we briefly describe the research directions of this dissertation followed by the main contributions. Finally, we provide an outline to the remainder of the dissertation.

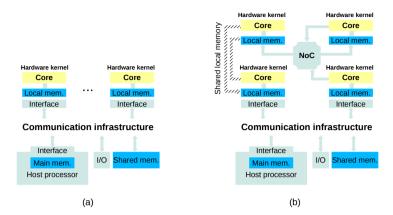

#### 1.1. Background

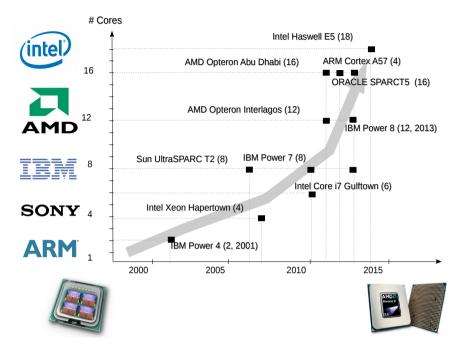

Although the number of transistors per chip is growing due to technology scaling [2], increasing the clock rate of processors is becoming economically less viable due to fabrication cost and power consumption [3]. These limitations shifted the trend towards the integration of a growing number of homogeneous or heterogeneous processing cores [4] in general-purpose [5], embedded [6, 7] and high-performance computing platforms [8] as depicted in Figure 1.1. However, these multicore architectures pose specific challenges regarding their programmability, as the effective utilization of these platforms in an architecture agnostic way is not possible. Hardware constraints, such as memory bandwidth, local scratch-pad memory etc. need

Figure 1.1: Multicore processor proliferation [1].

to be explicitly taken into account.

Because of the growing gap between processor and memory speeds [9], it is becoming more and more important to optimize memory-access behavior of applications. Secondly, with the growing number of cores, the degradation of performance improvement exacerbates, as communication is typically more time-consuming than computation. Hence, this communication is considered as the major design challenge in multicore architectures [10]. In addition, it is a major source of energy consumption [11].

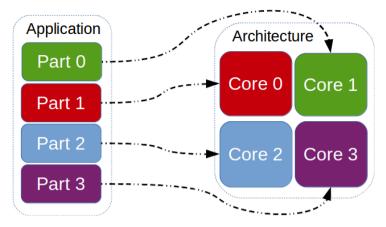

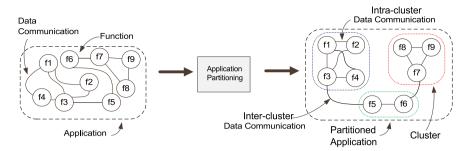

#### **1.1.1.** Application Partitioning

There is a huge code base of legacy, sequential applications which need to be ported to emerging multicore architectures, and thus need to be parallelized. To port an existing sequential application to multicore architecture, applications must be divided into smaller parts which are mapped to the available cores in the architecture as shown in Figure 1.2. This is known as application partitioning and it is a critical task, as an improper partitioning and mapping may result in performance degradation. Main identifiable reasons are irregular memory-access patterns and the communication among cores which may reduce the anticipated performance improvement.

Figure 1.2: Partitioning of an application into four parts to be mapped on the available four cores in the architecture.

#### 1.1.2. Classes of Parallelism

Parallel computing is the form of computing in which various computations can be carried out simultaneously. This is possible because of the availability of parallelism in applications. Parallelism exists in applications in two forms.

- Data-Level Parallelism refers to the class of parallelism in which there are many data items that can be processed in parallel. For instance, addition of two matrices where addition of elements can happen in parallel.

- Task-Level Parallelism refers to the class of parallelism in which various tasks in application can be processed in parallel. For instance, if in an application we have to add, subtract and multiply two matrices, then these three tasks can be executed in parallel.

#### 1.1.3. Classes of Parallel Architectures

Computing systems exploit the parallelism available in application to gain performance. This can be done in four major ways.

- Instruction-Level Parallelism exploits data-level parallelism available in the application by pipelining and speculative execution.

- Data-Level Parallelism is exploited by vector architectures and Graphical Processing Unit (GPU) by applying a single instruction to multiple data items in parallel.

- Thread-Level Parallelism exploits data-level or task-level parallelism. This is achieved in a tightly coupled hardware model where parallel threads can interact among each other.

- Request-Level Parallelism exploits task level parallelism among largely decoupled tasks specified by operating system or programmer.

#### 1.1.4. Heterogeneous Computing

Heterogeneous computing utilizes heterogeneity in the architecture to perform efficient processing. Heterogeneity refers to the availability of more than one kind of cores in the architecture. Some cores have good single thread performance, whereas, the other cores have high throughput. Heterogeneous systems gain high performance and energy efficiency due to these dissimilar cores which are specialized for specific type of processing. This means that each application or part of an application is matched to the core, based on its performance demand.

A well known form of heterogeneous computing utilizes accelerators to gain performance. Here, compute intensive parts of an application are off-loaded to the accelerator. An accelerator is a computing unit comprised of many simple processing units specifically designed to run computationally intensive part of the application very fast.

GPU is a well known example of an accelerator. GPU was originally designed to efficiently process images, but their ability to perform floating point operations at extremely high speed has given rise to the form of computing coined as General Purpose Computing on GPUs (GPGPU). Apart form GPU, Xeon-Phi [12], Digital Signal Processor (DSP) [7] and Field Programmable Gate Array (FPGA) [6, 8] are also used as accelerators in various application domains.

#### **1.1.5.** Profilers

Profilers are program analysis tools which provide information about various aspects of programs, for instance, number and types of instructions, frequency of function calls [13], time consumed per function[14, 15], call-graph [13–16] etc. In [17], the need for such tools has been well formulated as:

"Program analysis tools are extremely important for understanding program behavior. Computer architects need such tools to evaluate how well programs will perform on new architectures. Software writers need tools to analyze their programs and identify critical sections of code. Compiler writers often use such tools to find out how well their instruction scheduling or branch prediction algorithm is performing."

#### Sec-1.1: Background

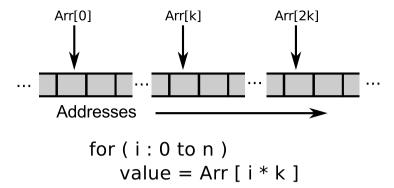

Figure 1.3: Memory-access with a stride of k.

#### 1.1.6. Memory Profilers

When a function loads/stores data from/to an address in memory, it is known as read/write memory-access. Memory profilers [14, 15, 18–20] monitor these memory reads and writes to provide information about the memory-access patterns of functions.

Cache memories try to make predictions mainly based on the following types of access patterns:

- 1. **Temporal:** recently accessed data will be needed again in the near future.

- 2. **Spatial:** data adjacent to the currently referenced data, will be accessed.

- 3. **Strided:** memory is accessed in some predictable pattern. An example of strided memory-access with a stride of *k* is shown in Figure 1.3. The code snippet performing this memory-access is also shown, where different values of *k* will result in different amounts of strides.

- When k=1, *Array* elements are accessed as 0, 1, 2, 3, ···. This pattern is known as sequential memory-access.

- When k=2, Array elements are accessed as 0, 2, 4, 6, ···.

- 4. **Random:** data is accessed randomly and is un-predictable.

Due to the growing gap between processor and Memory speeds [9], it is becoming increasingly important to characterize the memory-access patterns of applications for performance improvement. For instance, the information about access patterns is utilized by caches, which are small memories utilized to hide the main memory-access latency by predicting the next memory-access [21, 22]. Cache designers need the information about the memory-access patterns to design efficient cache controllers. Programmers need this information to match the access patterns of an application at hand with the cache architecture.

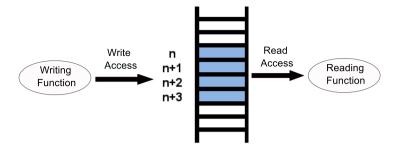

Figure 1.4: A memory write access followed by one or more memory read accesses form a data-communication relationship.

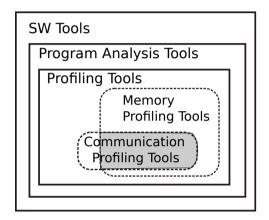

Figure 1.5: Data-communication profilers are generally special class of memory profiling tools. Some data-communication profilers report communication without tracing memory accesses.

#### 1.1.7. Data-Communication Profilers

Data-communication in an application occurs when certain part of a program writes data into memory and later the same data is read by another (or same) part of the application. Therefore to track data-communication, both memory read and write accesses need to be tracked as shown in Figure 1.4.

At the fine-granularity level, this data-communication can be reported at the instruction or the basic block level. At the coarser-granularity, data-communication can be reported between functions in a sequential application or between threads in parallel applications. Profilers that provide this inter/intra-function data-communication information are termed as data-communication profilers. Figure 1.5 shows the clear relationship between memory profilers and data-communication profilers, where it can be seen that data-communication profilers are a sub class of memory profilers. Furthermore, it can also be seen that some data-communication profilers do not utilize memory access information to report data-communication. These profilers track, for instance, network traffic to report communication.

#### Sec-1.1: Background

Figure 1.6: An application is partitioned into three clusters depicting intra-cluster and inter-cluster datacommunication.

Data-communication can occur in various patterns [23]. We briefly describe here the common data-communication patterns.

- Read-only: In this communication pattern, data is written to a memory location once but read multiple times. This pattern involves reading the same data over and over again like reading constants, which are initialized once but read multiple times throughout the execution of application.

- 2. **Migratory:** This communication pattern occurs when a data structure is repeatedly read and then written by a number of threads in the atomic regions during program execution. An example can be the processing of an image by various threads repeatedly in a pipeline fashion.

- 3. **Producer-consumer:** Producer of a data structure is the thread which writes data to a data structure. The thread that reads this data structure is called the consumer. Hence, the process occurs in the form of a producer-consumer communication pattern.

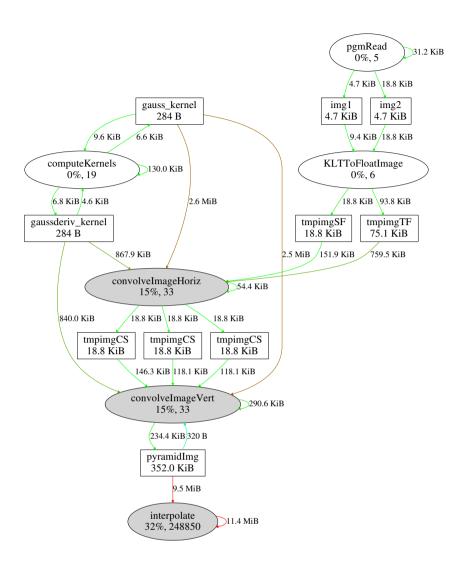

In order to provide a motivational example for data-communication profiling, consider the inter-function data-communication at the application level depicted on the left side of Figure 1.6. To map this application on a multicore architecture, functions can be clustered together as depicted on the right-hand side after application partitioning. Each cluster can be mapped onto a core in multicore architecture, converting inter-cluster communication into the inter-core communication. Consequently, it is very important to perform partitioning, utilizing the data-communication information in an intelligent manner in order to avoid expensive external communication.

For homogeneous architectures the data-communication information can be utilized by setting the thread affinity to bind highly communicating threads to the same core to reduce inter-core communication. For heterogeneous architectures, which utilize Central Processing Unit (CPU)/FPGA/DSP/Xeon-Phi as an accelerator, this information can be utilized to perform the mapping such that the expensive

Figure 1.7: Performance of SP benchmark degrades with growing number of cores [26].

data-communication between CPU and the accelerator is reduced as much as possible.

#### 1.2. Problem Overview

Due to technology scaling [2], the computing performance increased orders of magnitude during the last few decades. However, as the transistor size is approaching atomic scale, it is becoming increasingly difficult to improve microchip performance without making a considerable sacrifice on power and cost [4, 24, 25]. Due to this disproportional increase in power and cost, the industry can no longer rely on performance doubling every 18 months, though computational demands continue to increase sharply.

In order to satisfy the growing processing demands, the trend shifted towards growing number of cores [4, 27] to gain performance. Here, an application is analyzed to extract the parallel parts of the application which are executed as threads in parallel on the available cores in the architecture. Various challenges make it hard to parallelize applications to gain performance from multicore architectures [28–30]. First of all, not all applications are parallel in nature. Secondly, extracting the available parallelism from existing applications is not trivial because of the way they are written. For instance dependence analysis becomes difficult when features like indirect addressing, pointers, recursion and indirect functions are used. Secondly, determining the the loop boundaries and coordinating the accesses to global resources are also tedious and error prone.

Even if the applications are parallelized to take benefit of the available cores in the architecture, application performance does not necessarily scale with an increas-

Figure 1.8: Chip-level energy trends [36]

Table 1.1: Estimated energy consumption for arithmetic operations.

| ]         | Integer |         | Floatir | ng Point |

|-----------|---------|---------|---------|----------|

| Operation | Size    | Energy  | Size    | Energy   |

| Add       | 8-bit   | 0.03 pJ | 16-bit  | 0.4 pJ   |

| Auu       | 32-bit  | 0.1 pJ  | 32-bit  | 0.9 pJ   |

| Mult      | 8-bit   | 0.2 pJ  | 16-bit  | 1 pJ     |

| inuit     | 32-bit  | 3.1 pJ  | 32-bit  | 4 pJ     |

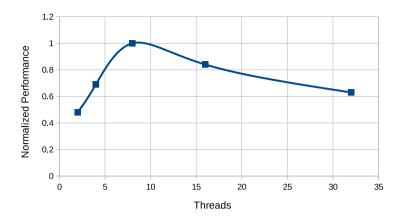

ing number of cores[31]. The performance is limited mainly due to the inter-core communication and contention while accessing shared memory [26, 32–34]. Figure 1.7 shows the performance of SP benchmark from NAS parallel benchmark suite [35] for various number of cores. It can be seen that the optimal number of cores is 8 and performance degrades for core count greater than 8. Similar results are reported in literature[31] for other real applications.

Realizing an exascale-level performance by the end of this decade imposes a major challenge on energy and power consumption [11, 36, 38]. The power consumption

Table 1.2: Estimated energy consumption for memory access.

| Memory Type | Size  | Energy       |

|-------------|-------|--------------|

|             | 8 KB  | 10 pJ        |

| Cache       | 32 KB | 20 pJ        |

|             | 1 MB  | 100 pJ       |

| DRAM        |       | 1.3 - 2.6 nJ |

Figure 1.9: Energy spent of DRAM refresh [37]

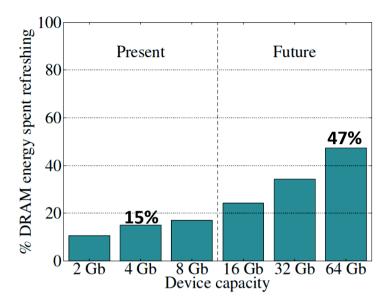

is increasingly dominated by data-transfer and memory accesses [36, 39, 40] in 65nm and smaller technologies as depicted in Figure 1.8. The research[38] presents the estimated energy cost for arithmetic operations and memory access (cache and DRAM) as given in Table 1.1 and Table 1.2, respectively. It can be seen that add and multiply operations of various sizes cost 0.03pJ-4pJ, whereas, cache memory access costs 10pJ-100pJ. The situation worsens if DRAM access is involved (1.3-2.6nJ of energy is consumed for a DRAM access [40]). DRAM consumes energy even when it is not being used due to cell refreshing. The energy consumption increases with the memory size [37], as depicted in Figure 1.9. The off-chip memory energy consumption is even worse as 40-50% of energy is spent in off-chip memory [38].

Heterogeneous multicores are envisioned to be a promising design paradigm to combat today's challenges in reducing power consumption and alleviate the impact of the memory wall [11, 27, 41]. This can be observed from the growing number of accelerator based systems in TOP500 list [42]. Currently the world's most powerful supercomputer, Tianhe-2 [43], utilizes accelerators. In general, the TOP500 list shows a growing momentum of accelerator based systems as currently more than 100 supercomputers use accelerators. These systems account for 143 petaflops of processing power which is over one-third of the list's total Floating Point Operations Per Second (FLOPS).

In these accelerator-based systems, the compute intensive part of the application is offloaded from CPU to the accelerator. The problem which arises from this offload model of computation is that data needs to be moved from CPU to the accelerator as this data-communication generally occurs on a slow bus, such as Peripheral

Component Interconnect Express (PCIe). This data-communication is considered as the primary bottleneck [44–47]. Recent work [48] shows that about 70% of the stalls are comprised of data-dependence and memory stalls. This percentage increases significantly when the peak bandwidth is reduced clearly indicating that limited off-chip memory bandwidth is a critical performance bottleneck for these applications. Therefore, partitioning an application to map on these architectures is a critical task [49, 50] as it requires structuring algorithms such that the expensive data-transfers are completely avoided or reduced as much as possible.

Another trend in computing, especially with accelerator-based computing, is that these architectures have deeper memory hierarchy. These systems normally have distinct on- and off-chip address spaces and require software to move data in between them. Example of such architectures exist in general purpose [5], [51], embedded [6, 7, 52], and high performance computing platforms [8, 53–55]. Explicit memory management is necessary for program correctness as well as to boost performance [25, 56–58] for these architectures. This implies that placing the data in the memory hierarchy closer to the processor is critical. This placement of data can be on-die cache or scratch-pad, local DRAM, or remote memory accessed over high-speed interconnect.

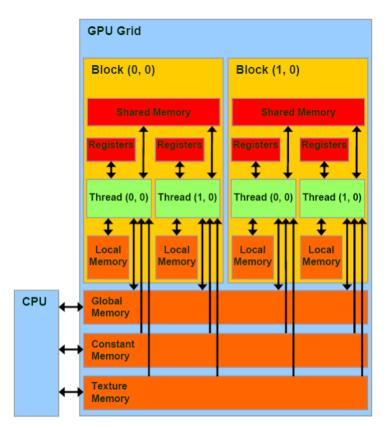

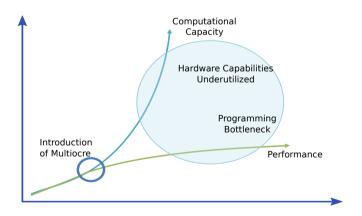

Figure 1.10 shows the memory hierarchy of the Nvidia GeForce GT-640 GPU architecture. Accessing the shared memory is an order of magnitude faster than accessing the global memory [60]. However, the trade off is that shared memory is limited and requires management by a programmer. The problem with these exposed memory hierarchy architectures is that it is not trivial to program these architectures. This is illustrated by Figure 1.11 where it can be seen that the computational capacity of multicore architectures is underutilized due to the programming bottleneck.

In a nutshell, the key to scaling computing performance is to reduce the data movement as much as possible. Accomplishing this requires a deep understanding of the memory access behavior of an application and careful look at the data flow in the application. Manual analysis of applications is tedious and error prone. Therefore, tools are required to characterize the data-communication in an application and highlight the communication hot spots. These tools can help programmers to perform communication-aware partitioning and mapping decisions based on detailed quantitative application profile. These tools are also helpful to system architects to design future interconnects considering the communication behavior of the target application domain.

#### 1.3. Research Questions

To efficiently map a sequential application onto a multicore architecture, various aspects need to be taken into account. These aspects are detection of computational

Figure 1.10: GPU memory hierarchy [54]

Figure 1.11: Productivity gap [59]

and memory hot-spots, extraction of parallelism, application partitioning, design space exploration, memory assignment, data-movement among cores etc. In this work we focus on some of the research questions as listed below.

**Question 1 -** How can we efficiently report data-communication among parts of an application at various granularity levels?

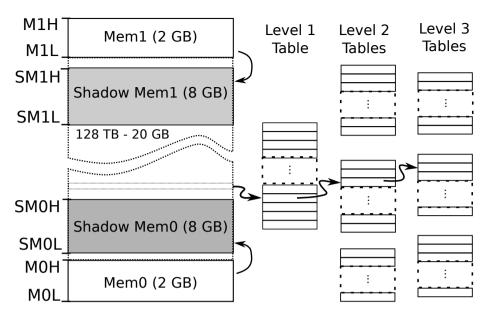

We discussed earlier that to report data-communication information, all the write and read memory accesses need to be related together to form data-communication relationship. The challenge lies in the fact that these reads and writes can happen anywhere in the 128 TB user address space, so keeping track of the writer of a memory location efficiently, is not trivial. Hence, the design of the tool has a great impact on the execution-time and memory-usage overheads of a profiler.

**Question 2 -** How far can we automate the process of application parallelization based on the detailed static and dynamic application profile?

Ideally we want to perform the application parallelization automatically by parallelizing compilers. But this approach has not been successful as compilers do not have enough information such as dependence at compile time. Therefore, the challenge is to utilize the detailed run-time information in conjunction with compile time information to automate the process as much as possible.

**Question 3 -** How can we utilize the data-communication patterns to assign the data-structures in an application to the available memory-hierarchy in the architecture?

Data-structures are allocated in memory and accessed by various parts of an application. Recent systems have various memory spaces available in the architecture. These spaces have different access-time and sizes. Proper utilization of these memory spaces based on the access pattern is critical to gain performance. The challenge in this regard is to report the access patterns in application at the data-structure level so that it can be utilized to perform proper memory assignment.

**Question 4 -** How can we utilize the memory-access and data-communication patterns in an application to design efficient hybrid interconnects for embedded and high performance computing platforms utilizing FPGA as an accelerator?

Using FPGA as accelerator has the advantage that its internal structure can be customized based on the computation in the application. In order to reduce the performance loss due to data-communication, can the interconnect be customized to match the application data-communication patterns?

**Question 5 -** How can we evaluate the quality of solutions generated by different partitioning algorithms in terms of computation and communication time of an application?

Due to a large variety of architectures and the lack of proper benchmarks, it is hard to reproduce experimental results, for fair comparison, on the target platforms. Furthermore, the complexity furthers in case of reconfigurable architectures as the application development process involves building and synthesizing hardware blocks. Considering these challenges, can we have a proper methodology to quickly evaluate the quality of the partitioning algorithms?

#### 1.4. Dissertation Contributions

In order to answer the research questions posed in the previous section, this thesis makes the following contributions.

- **Contribution 1 -** Developed an efficient, open-source profiler, *MCProf*. This profiler has at least an order of magnitude less overhead as compared to the state-of-the-art data-communication profilers for a variety of benchmarks. Furthermore, *MCProf* generates a detailed memory-access and data-communication profile of the application at various granularity levels. To generated information is related to the source-code making it easy for programmers or tools to utilize it.

- **Contribution 2 -** Developed a framework which automates the process of application parallelization. Source-level information is combined with the run-time information generated by *MCProf* to automatically generate parallel representation of an input sequential application.

- **Contribution 3 -** Validated the tool by utilizing the memory-access information generated by *MCProf* for the memory-intensive objects in the application to assign data-structures to the available memory spaces available in the accelerator, such as GPU and FPGA.

- **Contribution 4 -** Developed a Partition Evaluation Tool (PET) which can compare various partitioning algorithms based on the quality of the solutions found by these algorithms.

#### **1.5.** Dissertation Organization

Remainder of this dissertation is organized as follows.

**Chapter 2** surveys the memory-access optimization profilers and presents propose a classification of these profilers. Focus is on data-communication profilers which is a sub-class of memory-access optimization profilers. A detailed comparison of data-communication profilers is provided to highlight their strong and weak

aspects. Finally, recommendations for improving existing data-communication profilers and/or designing the future ones are thoroughly discussed.

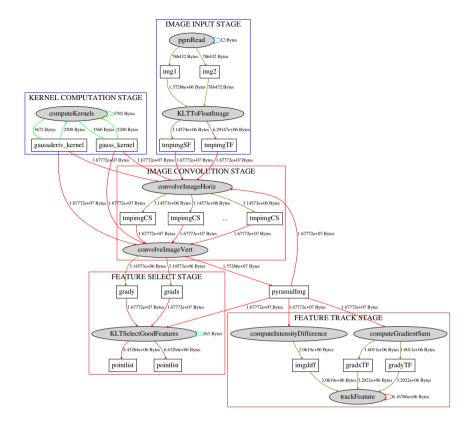

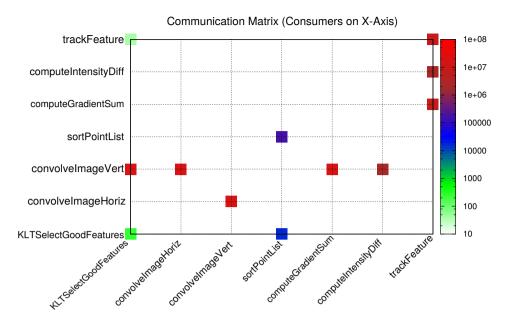

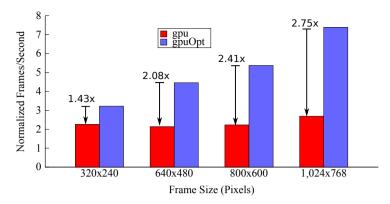

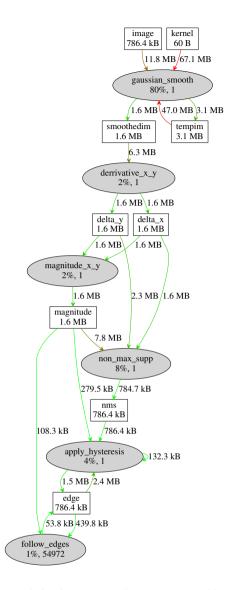

**Chapter 3** presents the design of *MCProf*, an efficient memory-access and data-communication profiler. In contrast to prior work, *MCProf* reports detailed profile at various granularity levels with manageable overheads for realistic workloads. Experimental results show that on the average, the proposed profiler has at least an order of magnitude less overhead as compared to the state-of-the-art data-communication profilers for a variety of benchmarks. A case-study is presented which shows the utilization of *MCProf* to efficiently map a sequential application on a platform using GPU as an accelerator.

**Chapter 4** first presents a semi-automatic parallelization methodology based on *MCProf* to help programmers extract and express parallelization. Later on, a toolchain is presented which automates the whole process of application parallelization to generate parallel representation of the input sequential application. We compare our approach with automatic parallelization and other semi-automatic parallelization and outline the advantages and limitations of each approach.

**Chapter 5** addresses the challenges of efficiently utilizing accelerator based architectures by utilizing the detailed memory access and data-communication profile of an application. Both software and hardware based optimizations for platforms utilizing FPGA as accelerator are presented. Experimental results are provided for real applications to show the effectiveness of the optimizations.

**Chapter 6** concludes this dissertation and presents future research areas.

# 2

# Background and Related Work

With the advent of technology, multi-core architectures are prevalent in embedded, general-purpose as well as high-performance computing. Efficient utilization of these platforms in an architecture agnostic way is an extremely challenging task. Hence, profiling tools are essential for programmers to optimize the applications for these architectures and understand the bottlenecks. Typical bottlenecks are irregular memory-access patterns and datacommunication among cores which may reduce anticipated performance improvement.

In this chapter, we survey the memory-access optimization profilers and propose a classification of these profilers. Focus is on data-communication profilers which is a sub-class of memory-access optimization profilers. A detailed comparison of data-communication profilers is provided to highlight their strong and weak aspects. Finally, recommendations for improving existing data-communication profilers and/or designing the future ones are thoroughly discussed.

#### 2.1. Introduction

Profilers are program analysis tools which provide information about various aspects of programs. For instance, number and types of instructions, frequency of function calls, time consumed per function call, etc. A lot of work is available in literature for profilers that focus at the fine granularity of instructions or at the coarse granularity of individual functions [13, 61, 62]. Cache profiling, which is a kind of

memory profiling [63], has also been studied extensively. However, very few tools exist which provide intra-application data-communication information. Therefore, in this work our focus is on memory profiling tools with a focus on those which provide intra-application data-communication information. Even though there is no generally acknowledged classification of memory profilers, we propose to organize the discussion based on the following three aspects of profiling:

- Profiling objective (Section 2.2)

- Profiling input ( Section 2.3 )

- Profiling technique (Section 2.4)

The remainder of this paper is organized as follows. We start by detailing the proposed classification in Section 2.2, Section 2.3 and Section 2.4. In Section 3.7, we compare existing memory profilers which provide the data-communication information. To the best of our knowledge, we have included all the tools in this regard. Based on this study, we provide some recommendations for the improvements of the existing data-communication profilers or design of the future ones, in Section 2.6. Finally, Section 2.7 concludes the paper.

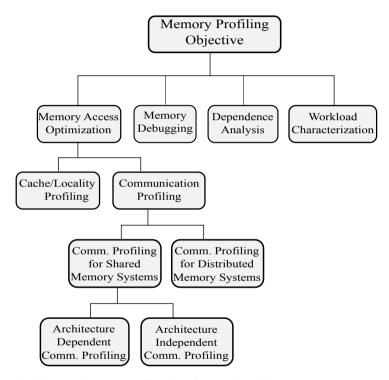

#### **2.2.** Memory Profilers based on Profiling Objective

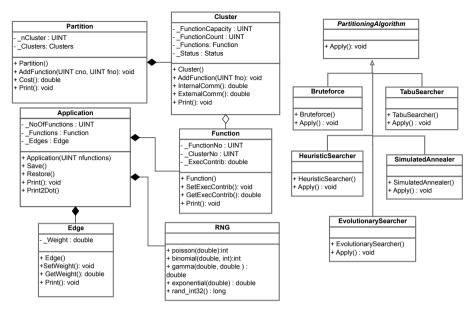

Based on the profiling objective, we further classify memory profilers into four classes, namely, memory-access optimization, memory debugging, dependence analysis and workload characterization, depicted in Figure 2.1. Furthermore, memory-access optimization profilers are further classified into cache/locality profilers and data-communication profiling. The focus of this work is on profilers designed for memory-access optimization. We believe that the other classes of profilers have been discussed in other studies and a number of example tools are available.

#### **2.2.1.** Memory Profiling for Memory-access Optimization

Profilers in this class analyze performance issues related to memory accesses in applications. For instance, the performance of an application may suffer because of pure locality of memory accesses. Cache/locality profilers can highlight the parts of the application responsible for such behavior. Another aspect of performance optimization is the communication among the parts of applications running on separate homogeneous/heterogeneous cores. Data-communication profilers provide such information and highlight communication related performance bottlenecks.

Figure 2.1: Classification of memory profilers based on profiling objective.

Table 2.1: Cache/Locality profilers

| Counters,                    | <b>HWC</b> : Hardware Counters, | Development Environment, h           | nand line, <b>IDE</b> : Integreted E        | ation, <b>CL</b> : Comn | y Instrument. | ration, <b>SBI</b> : Static Binar<br>oring Unit | Instrument | Src: Source, ST: Single Threaded, MT: Multi threaded, DBI: Dynamic Binary Instrumentation, SBI: Static Binary Instrumentation, CL: Command line, IDE: Integreted Development Environment, HV IBS: Instruction Based Sampling, TBS: Time Based Sampling, PMU: Performance Monitoring Unit | hreaded, <b>MT:</b> Multi thr<br>ampling, <b>TBS</b> : Time Ba | Src: Source, ST: Single TIBS: Instruction Based Si |

|------------------------------|---------------------------------|--------------------------------------|---------------------------------------------|-------------------------|---------------|-------------------------------------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------|

| SPARC,<br>X86-64             |                                 | Free                                 | Arch. Perf. Counters,<br>VampirTrace(MPI)   | НWС                     | IDE           | Graphical Reports                               | MT         | C, C++, OpenMP,<br>MPI, Java                                                                                                                                                                                                                                                             | Src for detailed graphical reports                             | Solaris Studio[71]                                 |

| Intel, AMD                   | Win                             | Free                                 | Arch.<br>Perf.<br>Counters                  | HWC                     | CL, IDE       | Graphical Reports                               | МТ         | C, C++, C#, C++ AMP, Visual Basic, Visual F#, Java Script, OpenMP                                                                                                                                                                                                                        | Src for detailed<br>graphical reports                          | Visual Profiler[70]                                |

| AMD                          | Linux, Win                      | Commercial(AMD),<br>Open-Src (Linux) | Arch. Perf. Counters<br>(AMD IBS, TBS)      | HWC                     | CL, IDE       | Graphical Reports                               | MT         | C, C++,<br>OpenCL                                                                                                                                                                                                                                                                        | Src for detailed graphical reports                             | CodeXL [69] (successor<br>(of Code Analyst)        |

| HP Integrity<br>Servers      | HP-UX                           | Commercial(HP) Free(Non-Commercial)  | •                                           | DBI                     | CL, IDE       | Graphical Reports                               | МТ         | C, C++                                                                                                                                                                                                                                                                                   | Src for detailed<br>graphical reports                          | Caliper[68]                                        |

| Intel                        | Tru64                           | Commercial<br>(HP)                   | АТОМ                                        | SBI                     | CL, IDE       | Graphical Reports                               | МТ         | C, C++,<br>pthreads                                                                                                                                                                                                                                                                      | Src for detailed<br>graphical reports                          | Graphical Program Analysis Toolkit[67]             |

| Intel                        | Linux, Win                      | Commercial<br>(Intel)                | Arch. Perf.<br>Counters (Intel PMU),<br>Pin | HWC, DBI                | CL, IDE       | Graphical Reports                               | МТ         | C, C++, C#, Java<br>Fortran, OpenMP,<br>MPI, OpenCL                                                                                                                                                                                                                                      | Src for detailed<br>graphical<br>reports                       | Vtune[15]                                          |

| Intel, AMD,<br>ARM           | Linux, OSX<br>Windows           | Free                                 | Arch. Perf.<br>Counters                     | HWC                     | CL, IDE       | Graphical Reports                               | МТ         | NA                                                                                                                                                                                                                                                                                       | Binary                                                         | Zoom[20]                                           |

| AMD                          | Linux                           | Open-Src                             | Arch. Perf.<br>Counters (AMD IBS)           | HWC                     | CL.           | Text Reports                                    | МТ         | NA                                                                                                                                                                                                                                                                                       | Binary                                                         | Dprof[66]                                          |

| Intel                        | Linux                           | Open-Src                             | Arch. Perf.<br>Counters (Intel PMU)         | HWC                     | CL            | Text Reports                                    | МТ         | NA                                                                                                                                                                                                                                                                                       | Binary                                                         | NUMATop[65]                                        |

| Intel, AMD,<br>ARM, PPC, IBM | Linux                           | Open-Src                             | Arch. Perf.<br>Counters                     | HWC                     | CL            | Text Reports                                    | МТ         | NA                                                                                                                                                                                                                                                                                       | Binary                                                         | Oprofile[14]                                       |

| Intel, AMD,<br>PPC           | Linux, OSX<br>Android           | Open-Src                             | Valgrind                                    | DBI                     | CL, IDE       | Text Reports,<br>Graphical Reports              | TM         | NA                                                                                                                                                                                                                                                                                       | Binary                                                         | Cachegrind[64]                                     |

| S Architecture               | OS                              | Availability                         | Based on                                    | Technique               | CL/IDE        | Output                                          | ST/MT      | Language                                                                                                                                                                                                                                                                                 | Src/Binary                                                     | Profiler                                           |

| od Blatform                  | Cimporto                        |                                      |                                             |                         | _             |                                                 | _          | Tool+                                                                                                                                                                                                                                                                                    |                                                                |                                                    |

#### Locality/Cache Profilers

To decrease the gap between processor and main memory, small but very fast memories, known as caches, are used. As the size of these memories is small, only the most frequently used data can be stored in these memories based on the prediction of the algorithm in cache controller. Hence, analysis of cache behavior is crucial to increase the performance of the programs, and/or design new cache algorithms. Various tools exist which profile applications to analyze cache behavior as listed in Table 2.1. A few well-known open-source tools are detailed below.

Cachegrind [64] is Valgrind tool which can detect first and last level instruction and data cache misses for C/C++ programs. Cachegrind tracks cache statistics (I1, D1 and L2 hits and misses) for every individual line of source code executed by the program. At program termination, it prints a summary of global statistics, and dumps the line-by-line information to a file. This information can then be used by an accompanying script to annotate the original source code with per-line cache statistics. KCachegrind, a visualization tool for the profiling data generated by Cachegrind, is also available.

Oprofile [14] is a hardware dependent, open-source profiling tool that works on recording events from hardware performance measurement units. Apart from various other performance events, it can sample events related to L1, L2 instruction and data caches to provide information about cache hits/misses by an application on a certain platform. The profiler is controlled by using the opcontrol and the reports are generated by the opreport utility.

NumaTOP [65] is an open-source tool for runtime memory locality characterization and analysis of processes and threads running on a NUMA system. It utilizes Intel hardware performance counters sampling technologies to identify where NUMA related performance bottlenecks reside. This performance data is associated with Linux runtime information to provide real-time analysis in a GUI on production systems.

#### **Data-communication Profilers**

Memory profilers in this class, profile applications to measure communication among various parts of an application. These profilers are further classified in to the following two classes.

**Shared Memory Data-communication Profilers** Table 2.2 provides a summary of such profilers. Quad (Quantitative Usage Analysis of Data) [72] provides dynamic information regarding data usage between any pair of co-operating functions in an application. This tool is based on Pin [76] and it tracks the reads and writes to a memory location at the granularity of byte. When a function writes to a memory location, it is saved as a producer of this memory location in a Trie

Table 2.2: Data-communication profilers

| Src: So                                                                                                                                              | Redux[75]               | CETA[74]                   | Pincomm[73]                  | QUAD[72]                     | Profiler     |                    |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|----------------------------|------------------------------|------------------------------|--------------|--------------------|--|

| urce, ST                                                                                                                                             | [75]                    | 74]                        | m[73]                        | [72]                         |              |                    |  |

| : Single Threaded, MT: Mul                                                                                                                           | binary                  | binary                     | binary                       | binary                       | Src/binary   | Input              |  |

|                                                                                                                                                      | NA                      | NA                         | NA                           | NA                           | Language     |                    |  |

| ti threaded                                                                                                                                          | ST                      | ST                         | MT                           | ST                           | ST/MT        |                    |  |

| d, <b>DBI</b> : Dynai                                                                                                                                | text                    | DOT                        | CSV                          | DOT, XML                     | Output       |                    |  |

| nic Binary                                                                                                                                           | CL                      | CL                         | CL                           | CL                           | CL/IDE       |                    |  |

| Instrumentation                                                                                                                                      | DBI                     | architecture<br>simulation | DBI                          | DBI                          | Technique    |                    |  |

| , <b>CL</b> : Commai                                                                                                                                 | Valgrind                | Virtutech<br>Simics        | Intel Pin                    | Intel Pin                    | Based on     |                    |  |

| nd line, IDE: I                                                                                                                                      | Open-Src                | Open-Src                   | Open-Src                     | Open-Src                     | Availability |                    |  |

| Src: Source, ST: Single Threaded, MT: Multi threaded, DBI: Dynamic Binary Instrumentation, CL: Command line, IDE: Integreted Development Environment | Linux, Android,<br>OS X | Win, Linux                 | Win, Linux,<br>Android, OS X | Win, Linux,<br>Android, OS X | OS           | Supported          |  |

|                                                                                                                                                      | Intel, AMD,<br>ARM, PPC | Intel                      | Intel, ARM                   | Intel, ARM                   | Architecture | Supported Platform |  |

data structure. The function reading this memory location is called the consumer and by getting the information from the Trie, a producer-consumer communication relationship is established. Apart from providing the quantitative information about the number of bytes, two other metrics are also reported. The first metric is the number of unique memory addresses, while the second metric is the number of data values uniquely communicated from producer to consumer.

Pincomm [73, 77] is a tool based on Pin [76] which constructs Dynamic Data Flow Graph (DDFG) to report the communication flow between various parts of the program. The parts can be functions, data structures, threads etc. which are represented on DDFG. The communication is reported in the form of producer-consumer relationship. The information can also be provided in terms of marked region in the code which appear on the DDFG. These markers can also be used to start and stop communication. The dynamic objects allocated during the execution of the program are also detected to report the communication through these objects.

CETA (Communication Extraction from Threaded Applications) [74] provides dataflow information between multiple threads. Memory reads and writes are tracked at runtime using Simics multiprocessor architecture simulator [78]. Hash table is utilized to record the writing thread of an address. When the read is performed the communication is updated in another hash table. After the completion of simulation, Python scripts report the collected information as a DOT graph.

Redux [75] is a Valgrind based tool for drawing the detailed dynamic data flow graphs of programs. Because of these details, it can only be used for small kernels or parts of programs, as discussed by authors. Secondly, the purpose of the tool as reported by authors is to represent the computational history of a program and not the communication behavior.

**Distributed Memory Data-communication Profilers** Message Passing Interface (MPI) [79] is a popular example of distributed memory programming model. The MPI provides communication functionality between a set of processes in a language independent way. This explicit communication is carried out through routines like MPI\_send and MPI\_recieve. Various commercial [71, 80, 81] and well maintained open-source [82–85] tools exist which track these routines to characterize communication in MPI programs. We refer the reader to the comparative studies [86, 87] for further details. We would like to highlight here that these tools are not designed to provide the communication profile of sequential applications. These tools are based on the technique which requires MPI parallel program as input. Hence, it only helps in validating the parallel program written only in MPI, rather than constructing one.

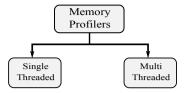

Figure 2.2: Classification of memory profilers based on profiling input.

# 2.3. Memory Profilers based on Input Application

Memory profilers can take sequential or parallel application as an input (Figure 2.2) to provide the memory access behavior of an application. Profilers also exist which can profile both sequential and parallel applications.

# 2.3.1. Profiling Sequential Applications

Profilers in this class profile sequential applications for performance analysis, report communication, trace bugs, detect data-races etc. QUAD [72] is an example of such profilers.

# 2.3.2. Profiling Parallel Applications

Profilers in this class provide information about the memory access behavior of the parallel applications. ParallelTracer [88] is a trace-based performance analysis framework for heterogeneous multicore systems. It instruments source code to trace various events in the application. It is an extension of Trace Collection and Trace Post Processing (TCPP) framework [89]. Furthermore, pin based tools [90], such as Parallel Amplifier, are available for the analysis and optimization of parallel C/C++ programs.

# **2.4.** Memory Profilers based on the Profiling Technique

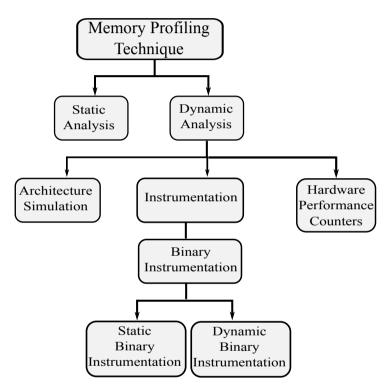

Based on the technique, memory profilers are broadly classified as static and dynamic analysis tools as shown in Figure 2.3. Static analysis tools provide the information based on the source-code without running the application. These tools can predict the communication in regularly structured programs. The polyhedral model is usually imposed in this analysis to compute the communication and data-dependencies analytically. For instance, the work presented in [91] uses exact data-dependence analysis provided by the polyhedral model to automatically explore the opportunities for communication/computation overlap. This kind of anal-

Figure 2.3: Classification of memory profilers based on profiling technique.

ysis is infeasible for a large number of existing and emerging applications as these programs have irregular structure. Furthermore, problems such as pointer analysis, is still very difficult, even exponential-time algorithms do not always produce sufficiently precise results [92].

Tools based on *dynamic analysis* collect information by running the application in a simulator or on the target platform. These are further classified as architecture simulation and instrumentation. *Architecture simulation* involves modeling a virtual computer system with CPU and memory hierarchy. SimpleScalar [93] is an example in this class, which can simulate various architectures with non-blocking caches, speculative execution, and state-of-the-art branch prediction. A drawback of this technique is that it is computationally intensive, which limit its use to small data inputs. Furthermore, simulation with these small data inputs may not exhibit the realistic memory-access patterns.

*Binary instrumentation* is a widely used instrumentation technique in which an instrumentation tool injects instrumentation code to the compiled binary. This type of instrumentation can be done statically or dynamically.

Static binary instrumentation was pioneered by ATOM [17]. ATOM organizes the final executable such that the application program and user's analysis routines run in the same address space. Hence, there is a possibility to mix code and data in an executable. Third Degree [94] and Graphical program analysis toolkit [67] by HP are example of tools in this regard.

Dynamic binary instrumentation involves the dynamic compilation of binary of an application to insert the instrumentation code anywhere in it. The program binary is instrumented just before its execution. Examples of tools utilizing this technique are Quad [72] and Pincomm [73, 77] which are based on Pin [76]. Similarly, Memcheck [18] and Redux [75] are examples of the tools based on Valgrind [16]. Dr. Memory [95] is another example of dynamic binary instrumentation based memory checking tool, based on open-source DynamoRIO [96] platform.

# **2.5.** Comparison of Data-Communication Profilers

Table 2.3 lists the profilers which can be utilized for memory-access optimizations. To present a combined view, this table depicts the classification of these profilers on the all the three aspects of the proposed criteria. An important observation that can be made from this table is that hardware performance counters and dynamic binary instrumentation is the most widely used technique utilized by these profilers. Another observation is that most of the existing tools focus on cache-access optimizations. Similarly, a number of tools exist with perform communication profiling for distributed memory systems where communication is explicit. However, very few tools provide architecture independent data-communication profiling information. Therefore, these tools are studied and there strengths and weaknesses are

Table 2.3: Classification summary of memory-access optimization profilers based on the proposed criteria.

|             |        |        | TM/T2  | A robito                   | O CHOCK                          | Profiling Technique               | Cachipac                                                     |

|-------------|--------|--------|--------|----------------------------|----------------------------------|-----------------------------------|--------------------------------------------------------------|

|             |        |        | 1MI/1S | Architecture<br>Simulation | static binary<br>Instrumentation | Dynamic binary<br>Instrumentation | nardware<br>Counters                                         |

| Cache/      |        |        | ST     |                            | HP Graphical                     |                                   | Oprofile[14], MS Visual Profiler[70], Zoom[20], NUMATop[65], |

| Locality    |        |        | +      |                            | Program                          | Cachegrind[64],                   | Vampir [81], Intel Vtune[15],                                |

| ofiler      |        |        |        |                            |                                  |                                   |                                                              |

| Pro         |        |        | Ш      |                            | Analysis Toolkit[67]             | HP Caliper[68]                    | AMD CodeXL[69], Dprof[66],<br>Oracle Solaris Studio[71]      |

| Shared      |        | Arch.  | L      | CETA[74]                   |                                  |                                   | NUMATop[65],<br>Intel Parallel Studio XE[80],                |

|             |        | Depend |        | ,                          |                                  |                                   | AMD CodeXL[69],<br>Nvidia NVVP[97]                           |

|             | _      |        |        |                            |                                  | QUAD[72],                         |                                                              |

| W N         |        | Arch.  | ST     |                            |                                  | Pincomm[73],                      |                                                              |

| <u>.</u>    |        | Indep. |        |                            |                                  | Redux[75]                         |                                                              |

|             | _      |        | ЬМ     |                            |                                  | Pincomm[73]                       |                                                              |

|             |        |        |        |                            |                                  | TAU[82], mpiP[83],                | Vampir Toolset[81], TAU[82],                                 |

| Distributed | 9      | nted   | Ε      |                            |                                  | Scalasca[84],                     | Intel Parallel Studio XE[80],                                |

| Memory      | $\Box$ | OLV    |        |                            |                                  | periscope[85]                     | Oracle Solaris Studio[71]                                    |

| Category                | QUAD                  | Pincomm                          |

|-------------------------|-----------------------|----------------------------------|

| Input                   | Binary                | Binary                           |

| Input Type              | ST                    | ST/MT                            |

| Output                  | dot, xml              | CSV                              |

| Technique               | DBI                   | DBI                              |

| Internal Data Structure | Trie                  | Hash table                       |

| Availability            | Open source           | Open source                      |

| Based on                | Intel Pin             | Intel Pin                        |

| Supported OS            | Win, Linux, OS X      | Win, Linux, OS X                 |

| Supported Architecture  | Intel, ARM            | Intel, ARM                       |

| Reported Metrics        | + (Bytes, UNMA, UNDV) | <ul> <li>(Bytes only)</li> </ul> |

| Profiling Granularity   | - (8-bit only)        | + (8,16,32,64-bit)               |

| Execution-time Overhead | +                     | - · · · · - · · · · · ·          |

| Memory-usage Overhead   | -                     | +                                |

| Documentation           | +                     | -                                |

Table 2.4: Comparitive summary of QUAD and Pincomm.

discussed and compared in this section.

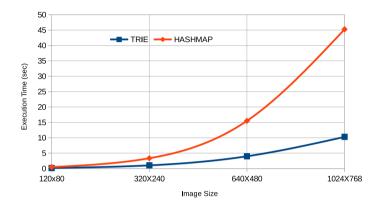

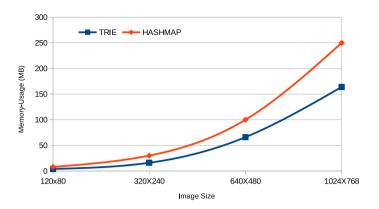

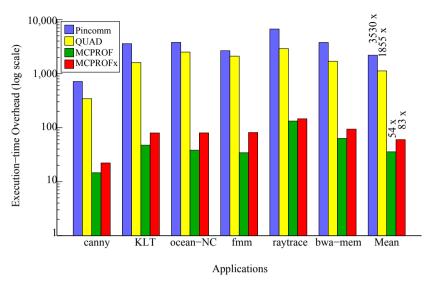

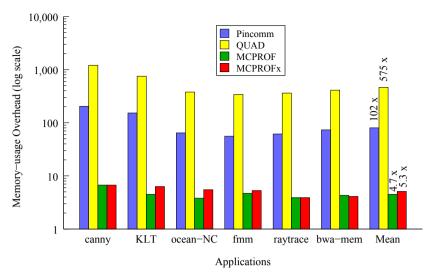

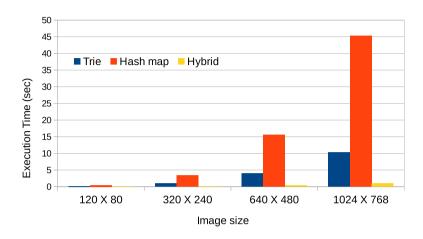

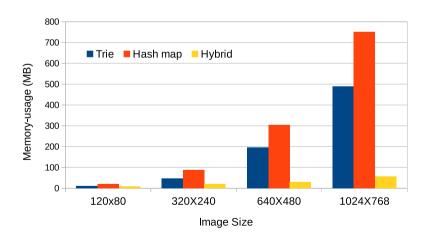

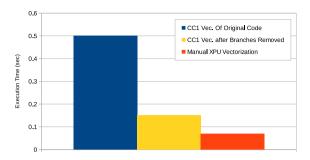

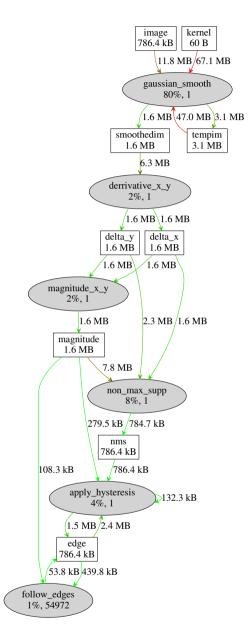

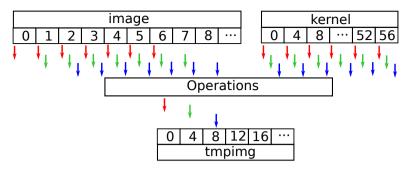

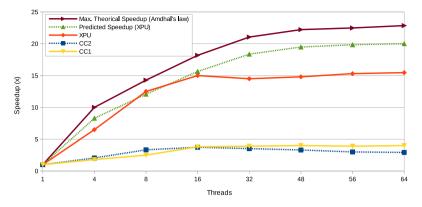

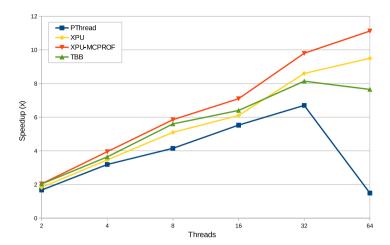

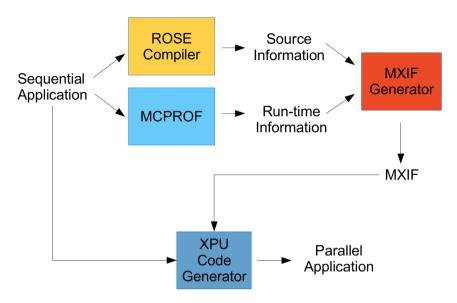

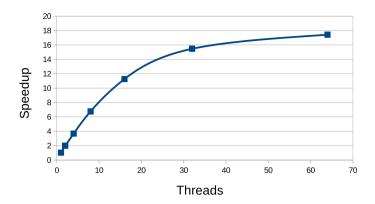

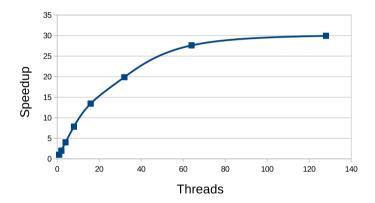

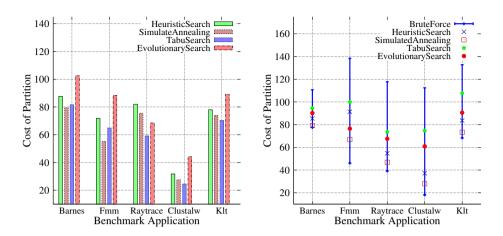

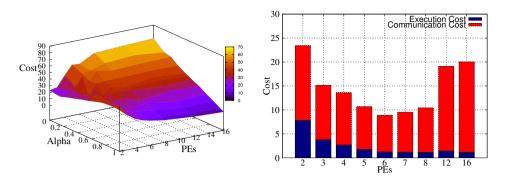

Redux provides the communication information at a fine-granularity of operations. Due to the amount of the details involved, it can only be used for very small toy applications, as indicated by the authors.