# MSc THESIS

# Experimental and Industrial Evaluation of Variability Resilient Schemes

Daniël Kraak

## Abstract

As semiconductor devices shrink further, the effects of *process variation* become more and more pronounced. They negatively impact the speed and power consumption of Integrated Circuits (ICs). Traditionally, a worst-case based design methodology is used to compensate for their potential impact. For modern technology this method means an increased penalty in area and power consumption. Therefore, Variability Resilient Schemes (VRSs) are introduced. They are used to improve the speed of ICs with slow processing and decrease the power consumption of ICs with fast processing. Thanks to these techniques a Better-Than-Worst-Case (BTWC) design methodology can be used. It improves performance, area, and power consumption.

The work in this thesis is performed within the Variability Resilient Architectures (VRA) project at NXP Semiconductors. In this project the potential of body biasing, clock stretching, and error avoidance flip-flops as VRSs is investigated. Circuits with VRSs run closer to their optimal performance. This means more extensive testing is necessary compared to worst-case based designs. Also, the usage of error avoidance flip-flops bring new testability challenges. In order for designs with VRSs to be interesting yield and testability need to be high enough. This thesis evaluates the testability challenges of the VRSs used in the VRA project. A cost model is proposed to compare the cost of worst-case based designs with designs with VRSs. The testability of the error avoidance flip-flop is evaluated and a solution is proposed for stuck-at and path delay testing of the error output. Finally, the potential of body biasing to compensate process variation is investigated, by comparing the performance of a worst-case based design and a BTWC design, which has an area reduction of 25%. The performance of both designs is compared by measuring path delays in both simulations and measurements. It is shown that with around 0.2 V forward body biasing the performance of the BTWC design is comparable to the worst-case design.

**CE-MS-2016-04**

Faculty of Electrical Engineering, Mathematics and Computer Science

# Experimental and Industrial Evaluation of Variability Resilient Schemes

#### THESIS

submitted in partial fulfillment of the requirements for the degree of

#### MASTER OF SCIENCE

$\mathrm{in}$

#### COMPUTER ENGINEERING

by

Daniël Kraak born in Dordrecht, The Netherlands

Computer Engineering Department of Electrical Engineering Faculty of Electrical Engineering, Mathematics and Computer Science Delft University of Technology

## Experimental and Industrial Evaluation of Variability Resilient Schemes

#### by Daniël Kraak

#### Abstract

As semiconductor devices shrink further, the effects of *process variation* become more and more pronounced. They negatively impact the speed and power consumption of Integrated Circuits (ICs). Traditionally, a worst-case based design methodology is used to compensate for their potential impact. For modern technology this method means an increased penalty in area and power consumption. Therefore, Variability Resilient Schemes (VRSs) are introduced. They are used to improve the speed of ICs with slow processing and decrease the power consumption of ICs with fast processing. Thanks to these techniques a Better-Than-Worst-Case (BTWC) design methodology can be used. It improves performance, area, and power consumption.

The work in this thesis is performed within the Variability Resilient Architectures (VRA) project at NXP Semiconductors. In this project the potential of body biasing, clock stretching, and error avoidance flip-flops as VRSs is investigated. Circuits with VRSs run closer to their optimal performance. This means more extensive testing is necessary compared to worst-case based designs. Also, the usage of error avoidance flip-flops bring new testability challenges. In order for designs with VRSs to be interesting yield and testability need to be high enough. This thesis evaluates the testability challenges of the VRSs used in the VRA project. A cost model is proposed to compare the cost of worst-case based designs with designs with VRSs. The testability of the error avoidance flip-flop is evaluated and a solution is proposed for stuck-at and path delay testing of the error output. Finally, the potential of body biasing to compensate process variation is investigated, by comparing the performance of a worst-case based designs is compared by measuring path delays in both simulations and measurements. It is shown that with around 0.2 V forward body biasing the performance of the BTWC design is comparable to the worst-case design.

| Laboratory | : | Computer Engineering |

|------------|---|----------------------|

| Codenumber | : | CE-MS-2016-04        |

Committee Members

| Advisor:     | dr. ir. Said Hamdioui, CE, TU Delft       |

|--------------|-------------------------------------------|

| Chairperson: | dr. ir. Said Hamdioui, CE, TU Delft       |

| Member:      | dr. ir. Bram Kruseman, NXP Eindhoven      |

| Member:      | dr. ir. Andre Bossche, EI, TU Delft       |

| Member:      | dr. ir. Mottaqiallah Taouil, CE, TU Delft |

Dedicated to my family and friends

# Contents

| List of Figures  | х    |

|------------------|------|

| List of Tables   | xi   |

| List of Acronyms | xiii |

| Acknowledgements | xv   |

| 1        | Intr | oducti   | on 1                                                        | L |

|----------|------|----------|-------------------------------------------------------------|---|

|          | 1.1  | Impac    | t of Process Variation                                      | 1 |

|          | 1.2  | State-   | of-the-Art                                                  | 2 |

|          | 1.3  | Main     | Contributions                                               | 3 |

|          | 1.4  | Thesis   | outline                                                     | 1 |

| <b>2</b> | Var  | iability | 7 Resilient Schemes 5                                       | 5 |

|          | 2.1  | Proces   | s Variation                                                 | ó |

|          | 2.2  | Motiva   | ation for Variability Resilient Schemes                     | 7 |

|          | 2.3  | Body     | Biasing                                                     | 3 |

|          | 2.4  | Error    | Avoidance Flip-Flop                                         | ) |

|          | 2.5  | Clock    | Stretching                                                  | 2 |

|          | 2.6  | Advan    | tages and Disadvantages 13                                  | 3 |

|          |      | 2.6.1    | Body Biasing                                                | 1 |

|          |      | 2.6.2    | Error Avoidance Flip-Flop                                   | 1 |

|          |      | 2.6.3    | Clock Stretching 16                                         | 3 |

|          |      | 2.6.4    | Comparison                                                  | 3 |

|          | 2.7  | Conclu   | 1sions                                                      | 7 |

| 3        | Eva  | luatior  | 19 Methodology for Variability Resilient Schemes            | ) |

|          | 3.1  | Cost N   | Model for Variability Resilient Schemes                     | ) |

|          |      | 3.1.1    | Taking Variability Resilient Schemes into account           | ) |

|          |      | 3.1.2    | Variability Resilient Schemes versus conventional design 20 | ) |

|          |      | 3.1.3    | Case Study                                                  | 1 |

|          |      | 3.1.4    | Validation                                                  | 2 |

|          | 3.2  | Variab   | ility Resilient Schemes vs Testability                      | 3 |

|          |      | 3.2.1    | Conventional Design Testing Method                          | 3 |

|          |      | 3.2.2    | Body Biasing                                                | 5 |

|          |      | 3.2.3    | Clock Stretching                                            | 7 |

|          |      | 3.2.4    | Error Avoidance Flip-Flop                                   | 3 |

|          | 3.3  | Conclu   | $1$ sions $\ldots$ $\ldots$ $\ldots$ $35$                   | 5 |

| <b>4</b>     | $\mathbf{Exp}$ | erimenta   | l and      | Industrial    | Evaluation              | of | Variability | Resilier | nt        |

|--------------|----------------|------------|------------|---------------|-------------------------|----|-------------|----------|-----------|

|              | Sch            | emes       |            |               |                         |    |             |          | <b>37</b> |

|              | 4.1            | Experime   | ntal Set   | ир            |                         |    |             |          | . 37      |

|              |                | 4.1.1 Te   | st Platf   | orm           |                         |    |             |          | . 37      |

|              |                | 4.1.2 Pa   | th Dela    | y Test Genera | ation $\ldots$ $\ldots$ |    |             |          | . 40      |

|              |                |            |            | -             |                         |    |             |          |           |

|              | 4.2            |            | e          |               | esults                  |    |             |          |           |

|              | 4.3            |            |            |               |                         |    |             |          |           |

|              |                |            |            | e             |                         |    |             |          |           |

|              |                |            |            |               | ns                      |    |             |          |           |

|              | 4.4            |            |            |               |                         |    |             |          |           |

|              |                |            |            |               | es                      |    |             |          |           |

|              |                |            |            |               |                         |    |             |          |           |

|              |                |            |            |               |                         |    |             |          |           |

|              | 4.5            |            |            |               | nts                     |    |             |          |           |

|              | 4.6            |            | e          |               |                         |    |             |          |           |

|              | 4.7            | Conclusio  | ns         |               |                         |    |             |          | . 69      |

| 5            | The            | sis Summ   | iarv an    | d Future W    | ork                     |    |             |          | 71        |

| Ŭ            | 5.1            |            | •          |               |                         |    |             |          | • –       |

|              | 5.2            |            |            |               |                         |    |             |          |           |

|              | -              |            |            |               |                         |    |             |          |           |

| Bi           | bliog          | graphy     |            |               |                         |    |             |          | <b>78</b> |

| ٨            | Cos            | t Model (  | Code       |               |                         |    |             |          | 79        |

| л            |                |            |            |               |                         |    |             |          |           |

|              |                | *          |            |               | erm                     |    |             |          |           |

|              | 11.2           | 0050 1000  | ici wittii |               |                         |    |             |          | . 00      |

| в            | Mea            | asuremen   | t Proce    | essing Script | -                       |    |             |          | 83        |

| С            | Tra            | nsient Sir | nulatio    | ns            |                         |    |             |          | 87        |

| D            | Mea            | asuremen   | t Resul    | ts Typical I  | Processing              |    |             |          | 91        |

| $\mathbf{E}$ | Mea            | asuremen   | t Resul    | ts Slow Pro   | cessing                 |    |             |          | 95        |

# List of Figures

| 1.1               | Impact of process variations on performance and power for ICs from the same wafer for a $180 \text{ nm}$ process (from [1])                                                                                                 | 2        |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1.2               | Classification diagram of Variability Resilient Schemes                                                                                                                                                                     | 3        |

| 2.1               | Global variations can be recognized lot-to-lot, wafer-to-wafer, and within-wafer.                                                                                                                                           | 6        |

| 2.2               | Local variation is the variation within a die, also called within-die variation                                                                                                                                             | 6        |

| 2.2<br>2.3<br>2.4 | Probability density function of the speed of an IC after fabrication<br>Old versus modern technology speed distributions. The frequency de-                                                                                 | 7        |

|                   | notes the normalized clock speed of the circuit.                                                                                                                                                                            | 8        |

| 2.5               | Silicon speed distributions before and after body biasing                                                                                                                                                                   | 9        |

| 2.6               |                                                                                                                                                                                                                             | 10       |

| 2.7               |                                                                                                                                                                                                                             | 10       |

| 2.8               |                                                                                                                                                                                                                             | 11       |

| 2.9               |                                                                                                                                                                                                                             | 13       |

| 2.10              |                                                                                                                                                                                                                             | 13       |

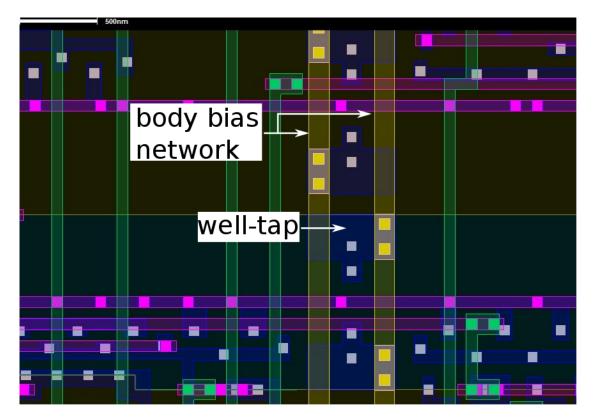

| 2.11              | GDSII image showing the body bias power networks that connect using well-taps to the n- and p-wells                                                                                                                         | 15       |

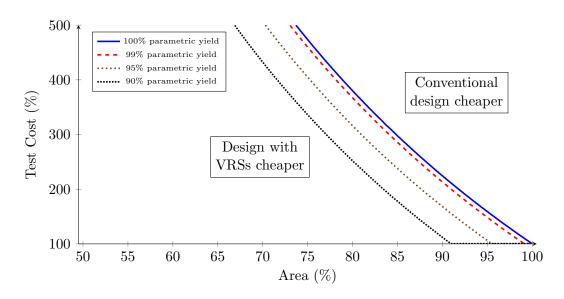

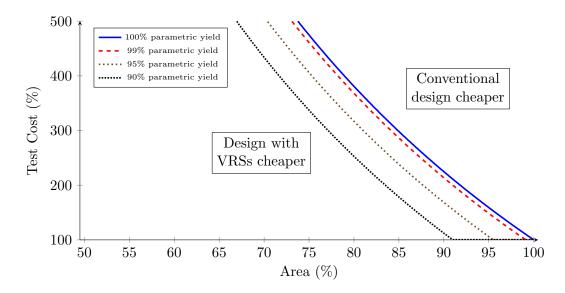

| 3.1               | Cost model results for the case study. Results are shown for 100%, 99%, 95%, and 90% parametric yield. When below the line, design with VRSs                                                                                | ~~~      |

| 3.2               | Cost model results for the case study, but now using the gross die per                                                                                                                                                      | 22       |

| <u></u>           |                                                                                                                                                                                                                             | 23<br>05 |

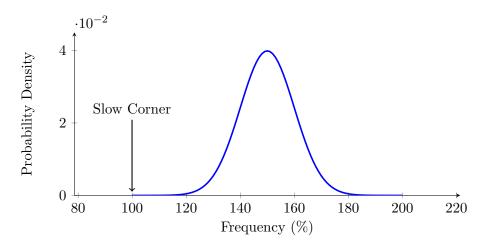

| $3.3 \\ 3.4$      | Example of probability distribution of IC speed for older technology<br>Example of effect of small-delay defect in older technology. As can be<br>seen the affected IC still has a speed above the worst-case corner, which | 25       |

|                   | -                                                                                                                                                                                                                           | 25       |

| 3.5               |                                                                                                                                                                                                                             | 26       |

| 3.6               |                                                                                                                                                                                                                             | 28       |

| 3.7               |                                                                                                                                                                                                                             | 29       |

| 3.8               |                                                                                                                                                                                                                             | 30       |

| 3.9               |                                                                                                                                                                                                                             | 30       |

| 3.10              |                                                                                                                                                                                                                             | 31       |

| 3.11              | Stuck-at-'0' testing of error avoidance flip-flop's ERROR output using                                                                                                                                                      |          |

|                   |                                                                                                                                                                                                                             | 32       |

| 3.12              | Proposed DFT circuit of error avoidance flip-flop. A NAND gate is                                                                                                                                                           |          |

|                   | added, so the propagation of the value in M1 to the slave latch is blocked,                                                                                                                                                 |          |

|                   | 0                                                                                                                                                                                                                           | 33       |

| 3.13              |                                                                                                                                                                                                                             | 34       |

| 3.14              | Alternative DFT solution for the error avoidance flip-flop.                                                                                                                                                                 | 35       |

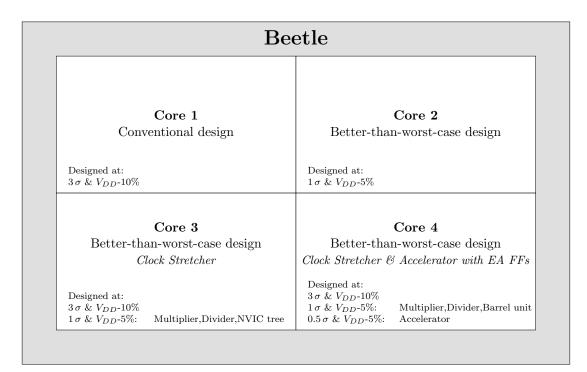

| 4.1  | Beetle Platform, showing its four cores and synthesis constraints                                                   | 39 |

|------|---------------------------------------------------------------------------------------------------------------------|----|

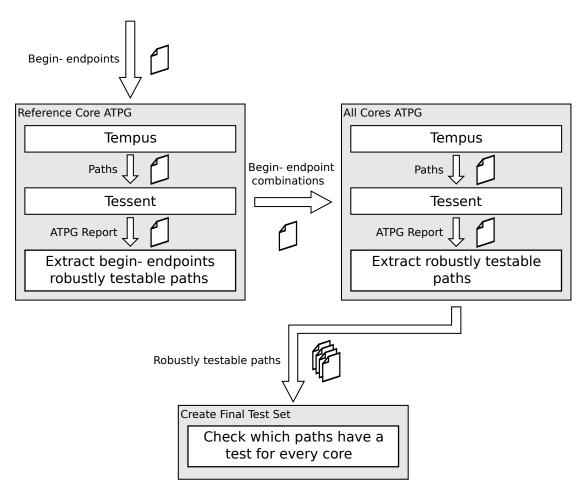

| 4.2  | Flowchart of the Path Delay ATPG process                                                                            | 42 |

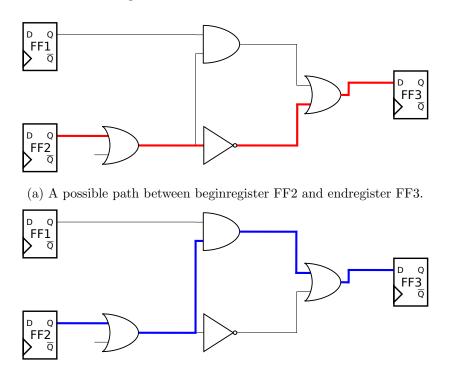

| 4.3  | Multiple paths exist between beginnegister FF2 and endregister FF3                                                  | 43 |

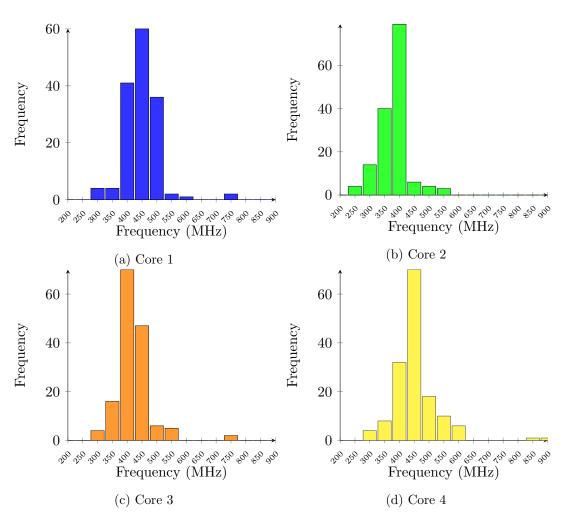

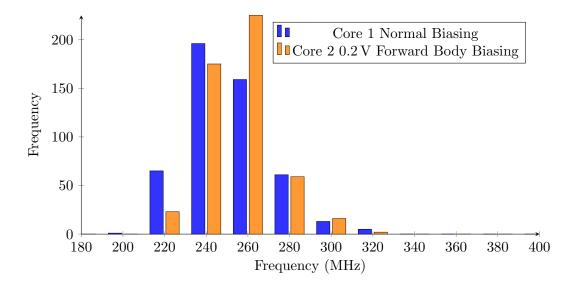

| 4.4  | Histograms of frequencies of the paths in the test set for each core. The                                           |    |

|      | frequencies are based on Static Timing Analysis (STA) for tt corner,                                                |    |

|      | $V_{DD} = 1.1 \mathrm{V}, \mathrm{T} = 25 ^{\circ}\mathrm{C}.$                                                      | 48 |

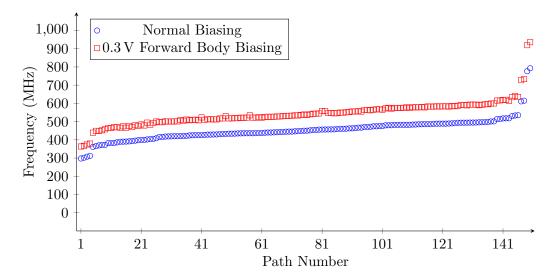

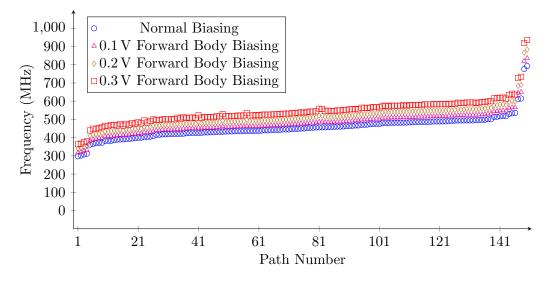

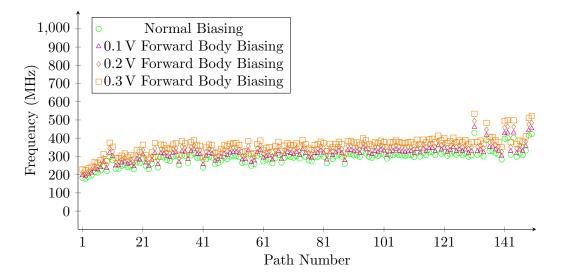

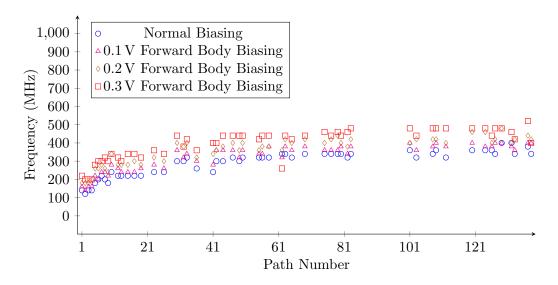

| 4.5  | Simulated path frequencies for core 1 under typical conditions: tt corner,                                          |    |

|      | $V_{DD}=1.1 \text{ V}, \text{ T}=25 ^{\circ}\text{C}$                                                               | 49 |

| 4.6  | Simulated path frequencies for core 2 under typical conditions: tt corner,                                          |    |

|      | $V_{DD}=1.1 \text{ V}, \text{ T}=25 ^{\circ}\text{C}$                                                               | 50 |

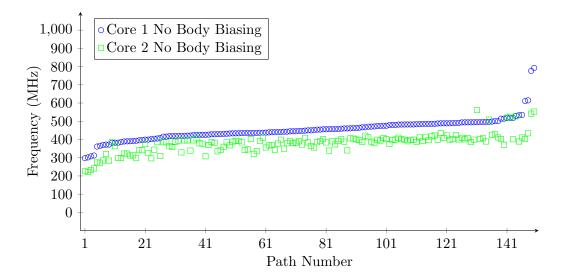

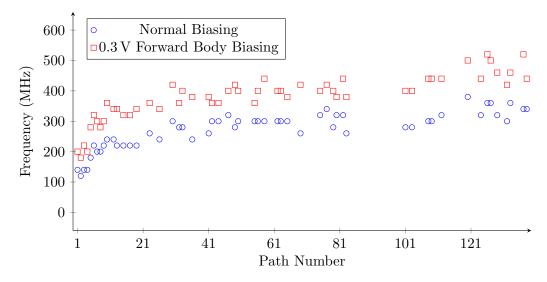

| 4.7  | Comparison of simulated path frequencies for cores 1 and 2 under typical                                            |    |

|      | conditions: tt corner, $V_{DD}$ =1.1 V, T=25 °C                                                                     | 51 |

| 4.8  | Comparison of simulated path frequencies for cores 1 and 2 under typical                                            |    |

|      | conditions: tt corner, $V_{DD}=1.1$ V, T=25 °C. Core 2 has 0.3 V forward                                            |    |

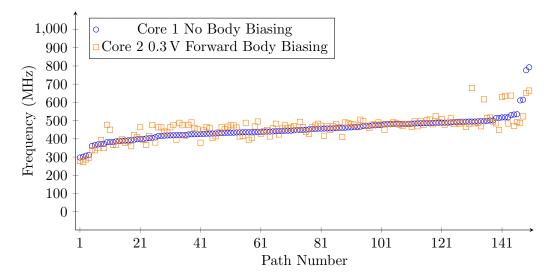

|      | body biasing.                                                                                                       | 51 |

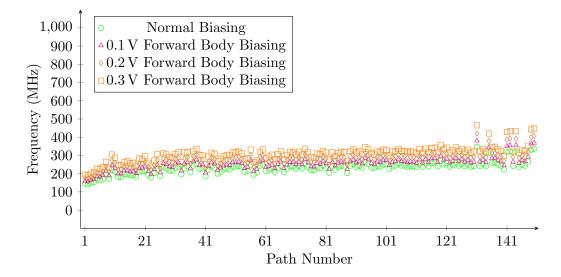

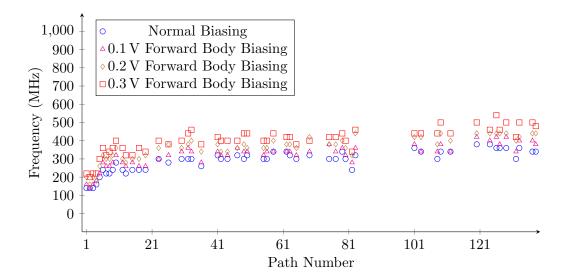

| 4.9  | Comparison of simulated path frequencies for cores 1 and 2 under worst-                                             |    |

|      | case conditions: ss corner, $V_{DD}$ at minimum specification of the specific                                       |    |

|      | core, T=125 °C $\ldots$                                                                                             | 52 |

| 4.10 | Comparison of simulated path frequencies for cores 1 and 2 under worst-                                             |    |

|      | case conditions: ss corner, $V_{DD}$ at minimum specification of the specific                                       |    |

|      | core, T=125 °C Core 2 has 0.1 V forward body biasing                                                                | 53 |

| 4.11 | Comparison of simulated path frequencies for cores 1 and 2 under worst-                                             |    |

|      | case conditions: ss corner, $V_{DD}$ at minimum specification of the specific                                       |    |

|      | core, $T=-40$ °C                                                                                                    | 54 |

| 4.12 | Path 1 Monte Carlo simulation results for cores 1 and 2 with $T=25$ °C,                                             |    |

|      | $V_{DD}=1.1$ V                                                                                                      | 55 |

| 4.13 | Path 1 Monte Carlo simulation results for cores 1 and 2 with $T=25$ °C,                                             |    |

|      | $V_{DD}=1.1$ V. Core 2 has 0.3 V forward body biasing.                                                              | 56 |

| 4.14 | Path 1 Monte Carlo simulations for cores 1 and 2 with T=125 °C, $V_{DD}$                                            |    |

|      | at minimum specification of the specific core                                                                       | 57 |

| 4.15 | Path 1 Monte Carlo simulations for cores 1 and 2 with T=125 °C, $V_{DD}$                                            |    |

|      | at minimum specification of the specific core. Core 2 has $0.2\mathrm{V}$ forward                                   |    |

|      | body biasing                                                                                                        | 57 |

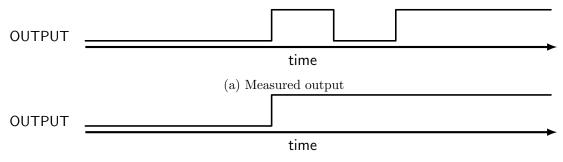

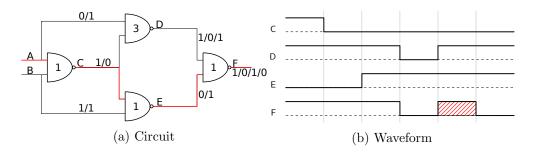

| 4.16 | Waveform showing an example of the unexpected glitches at the output                                                |    |

|      | observed for a lot of paths during measurements. In this example the                                                |    |

|      | path has a rising transition at the output.                                                                         | 58 |

| 4.17 | Example of a transition on a path with glitches on off-path inputs that                                             |    |

|      | control the output of the path. The gate delay is marked inside the gate.                                           |    |

|      | The path that the transition passes through is highlighted. On A a 0 $\rightarrow$                                  |    |

|      | 1 transition is created. This will create a $1 \rightarrow 0$ transition on the output                              |    |

|      | F. On D, however, a hazard occurs, pulling output F high for a short                                                |    |

|      | time                                                                                                                | 59 |

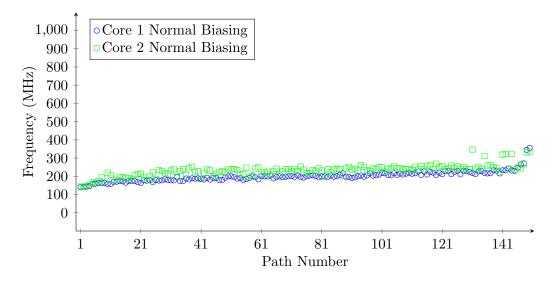

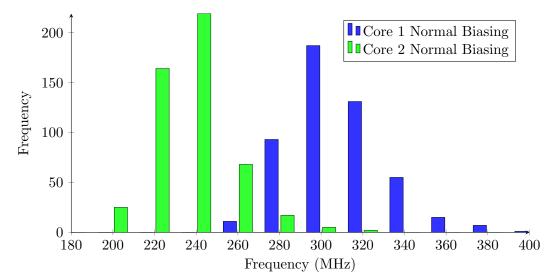

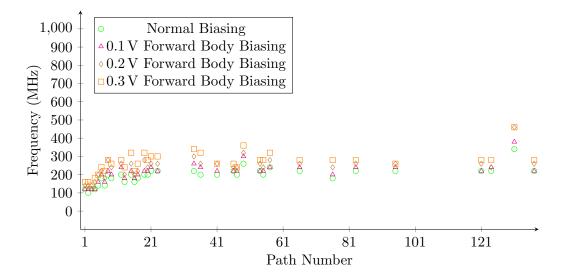

| 4.18 | Measured path frequencies for core 1 of sample A010 (tt corner). Room                                               |    |

|      | temperature, $V_{DD} = 1.0 \text{ V} \dots \dots$ | 60 |

|      |                                                                                                                     |    |

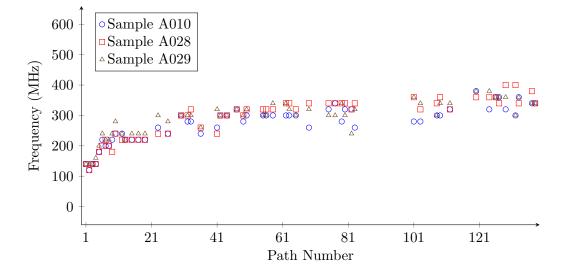

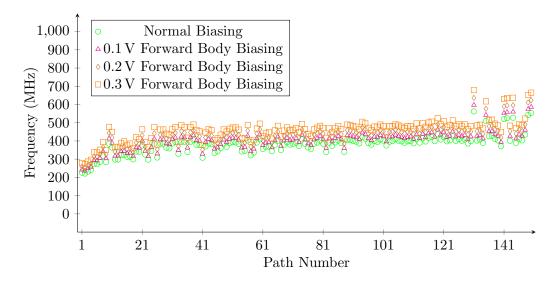

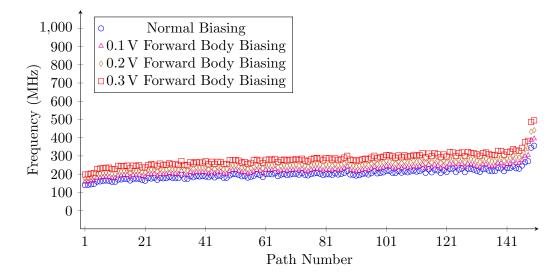

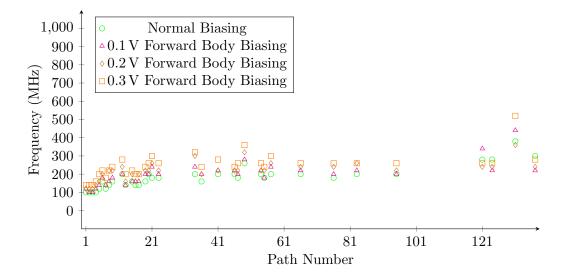

| 4.19 | Comparison of measured path frequencies for core 1 of samples A010, A028, and A029 (tt corner). Room temperature, $V_{DD}=1.0$ V                                                                                                                      | . 61 |

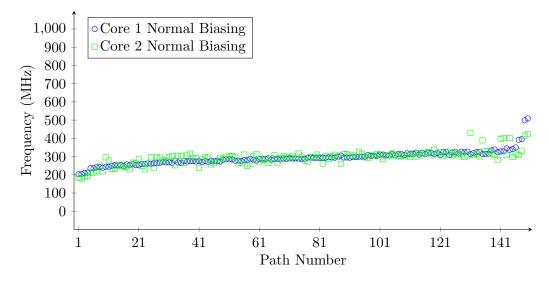

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

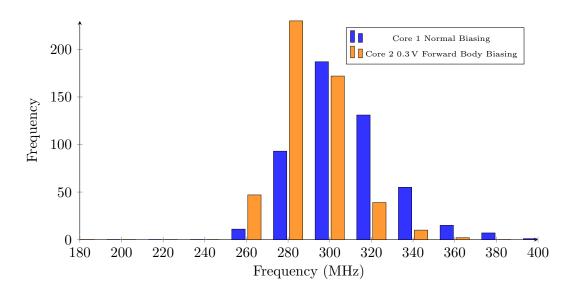

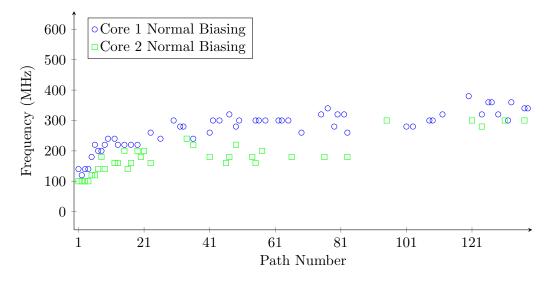

| 4.20 | Comparison of measured path frequencies for cores 1 and 2 of sample A010 (tt corner). Room temperature, $V_{DD}=1.0$ V                                                                                                                                |      |

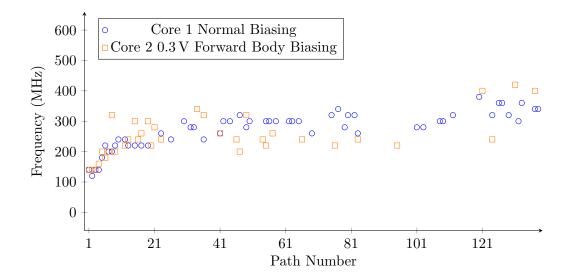

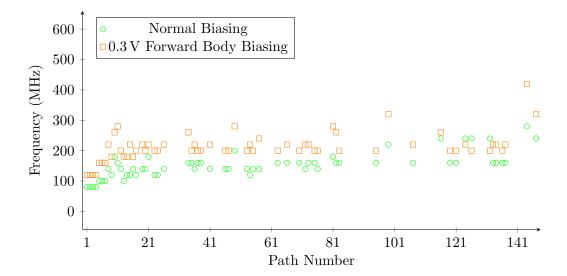

| 4.21 | Comparison of measured path frequencies for cores 1 and 2 of sample A010 (tt corner). Room temperature, $V_{DD}=1.0$ V. Core 2 has 0.3 V                                                                                                              | -    |

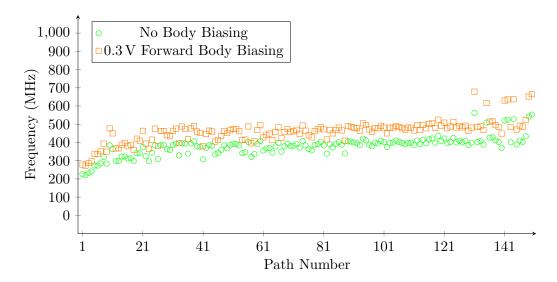

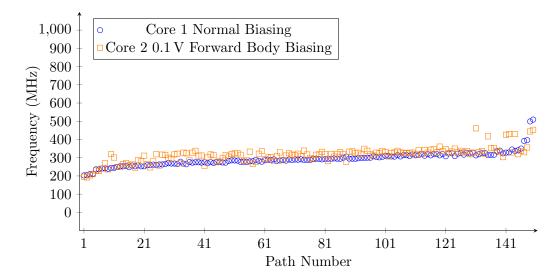

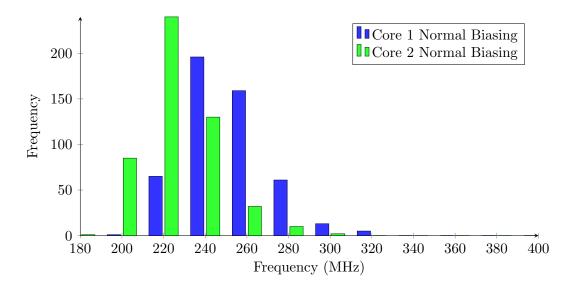

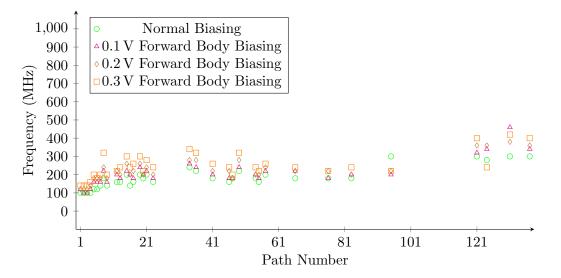

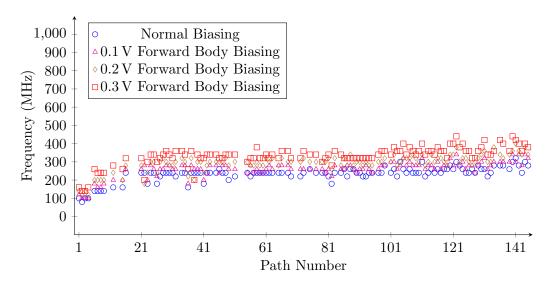

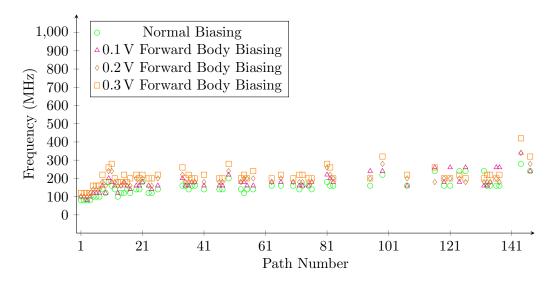

| 4.22 | forward body biasing                                                                                                                                                                                                                                  | 63   |

|      | temperature, $V_{DD}$ =1.0 V                                                                                                                                                                                                                          | 64   |

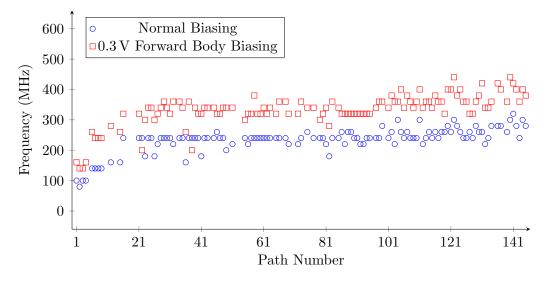

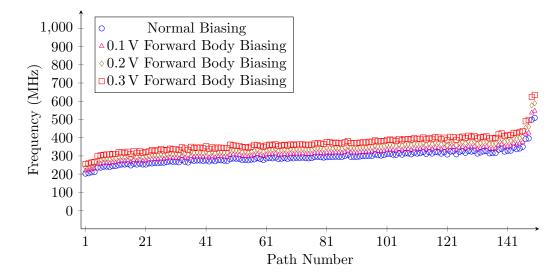

| 4.23 | Measured path frequencies for core 2 of sample C001 (ss corner). Room temperature, $V_{DD}=1.0$ V                                                                                                                                                     | 65   |

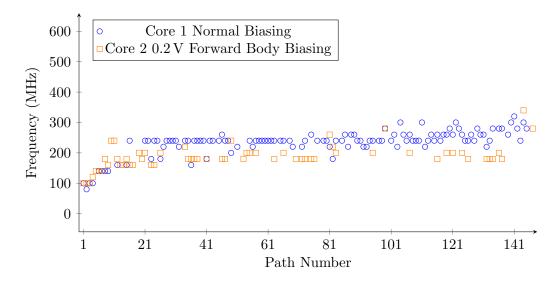

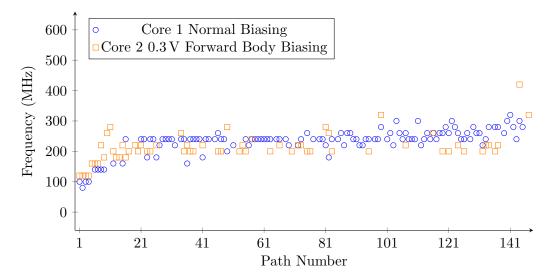

| 4.24 | Comparison of measured path frequencies for cores 1 and 2 of sample C001 (ss corner). Room temperature, $V_{DD}=1.0$ V. Core 2 has $0.2$ V                                                                                                            |      |

| 4.95 | forward body biasing.                                                                                                                                                                                                                                 | 66   |

| 4.25 | Comparison of measured path frequencies for cores 1 and 2 of sample C001 (ss corner). Room temperature, $V_{DD}=1.0$ V. Core 2 has $0.3$ V forward body biasing.                                                                                      | 66   |

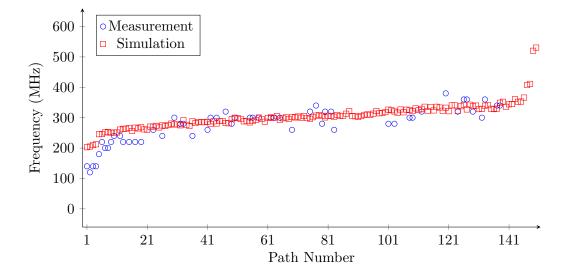

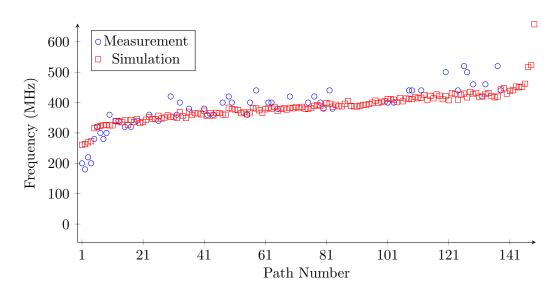

| 4.26 | Comparison of measured and simulated path frequencies for core 1 with                                                                                                                                                                                 | 00   |

|      | normal biasing. Measurements results are from sample A010 and are                                                                                                                                                                                     |      |

|      | done at room temperature, $V_{DD}=1.0$ V. Simulation results from tt corner, T=25 °C, and $V_{DD}=0.99$ V                                                                                                                                             | 67   |

| 4.27 | Comparison of measured and simulated path frequencies for core 1 with                                                                                                                                                                                 | 07   |

|      | $0.3\mathrm{V}$ forward body biasing. Measurements results are from sample A010                                                                                                                                                                       |      |

|      | and are done at room temperature, $V_{DD}=1.0$ V. Simulation results from tt corner, T=25 °C, and $V_{DD}=0.99$ V                                                                                                                                     | 68   |

|      |                                                                                                                                                                                                                                                       | 00   |

| C.1  | Simulated path frequencies for core 1 under typical conditions: tt corner,<br>$V_{DD}=1.1 \text{ V}, \text{ T}=25 ^{\circ}\text{C} \dots \dots$ | 87   |

| C.2  | $V_{DD}$ =1.1 V, 1=25 C                                                                                                                                                                                                                               | 01   |

|      | $V_{DD} = 1.1 \text{ V}, \text{ T} = 25 \text{ °C}$                                                                                                                                                                                                   | 87   |

| C.3  | Simulated path frequencies for core 1 under worst-case conditions: ss<br>$V_{\rm eq} = 0.00  {\rm M}  {\rm Tr} = 125  {\rm gc}$                                                                                                                       | 00   |

| C.4  | corner, $V_{DD}=0.99$ V, T=125 °C Simulated path frequencies for core 2 under worst-case conditions: ss                                                                                                                                               | 88   |

| -    | corner, $V_{DD} = 1.045$ V, T=125 °C                                                                                                                                                                                                                  | 88   |

| C.5  | Simulated path frequencies for core 1 under worst-case conditions: ss $V_{i} = 0.00 V_{i} T_{i} = 40.0 C_{i}$                                                                                                                                         | 00   |

| C.6  | corner, $V_{DD}=0.99$ V, T=-40 °C                                                                                                                                                                                                                     | 89   |

|      | corner, $V_{DD}$ =1.045 V, T=-40 °C                                                                                                                                                                                                                   | . 89 |

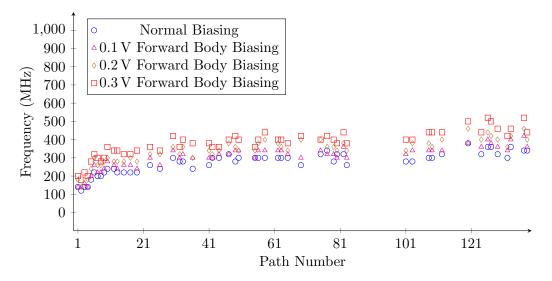

| D.1  | Measured path frequencies for core 1 of sample A010 (tt corner). Room                                                                                                                                                                                 |      |

|      | temperature, $V_{DD}$ =1.0 V                                                                                                                                                                                                                          | 91   |

| D.2  | Measured path frequencies for core 1 of sample A028 (tt corner). Room terms are tune, $V_{\rm corn} = 1.0 V_{\rm c}$                                                                                                                                  | 01   |

| D.3  | temperature, $V_{DD}=1.0$ V                                                                                                                                                                                                                           | 91   |

|      | temperature, $V_{DD}$ =1.0 V                                                                                                                                                                                                                          | 92   |

|      |                                                                                                                                                                                                                                                       |      |

| D.4 | Measured path frequencies for core 2 of sample A010 (tt corner). Room taxes $V_{i} = 1.0 V_{i}$                                             | 00 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | temperature, $V_{DD} = 1.0 \text{ V} \dots \dots$ | 92 |

| D.5 | Measured path frequencies for core 2 of sample A028 (tt corner). Room                                                                       |    |

|     | temperature, $V_{DD}$ =1.0 V                                                                                                                | 93 |

| D.6 | Measured path frequencies for core 1 of sample A029 (tt corner). Room                                                                       |    |

|     | temperature, $V_{DD} = 1.0 \text{ V} \dots \dots$                         | 93 |

| E.1 | Measured path frequencies for core 1 of sample C001 (ss corner). Room                                                                       |    |

|     | temperature, $V_{DD}$ =1.0 V                                                                                                                | 95 |

| E.2 | Measured path frequencies for core 2 of sample C001 (ss corner). Room                                                                       |    |

|     | temperature, $V_{DD}$ =1.0 V                                                                                                                | 95 |

# List of Tables

| $2.1 \\ 2.2$ | Thruth tables for (a) P0, (b) P1, and (c) ERROR signals Comparison between different Variability Resilient Schemes                        | $\begin{array}{c} 12\\17\end{array}$ |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| 3.1          | Paramater values used in the case study for the cost comparison of con-<br>ventional design versus design with VRSs                       | 21                                   |

| $4.1 \\ 4.2$ | Common specifications between four cores on the Beetle test chip<br>Area of each core of the Beetle platform. The area usage is expressed | 38                                   |

|              | relative to the area of core 1                                                                                                            | 38                                   |

| 4.3          | Example of when a path is added to the final test set. Only paths that                                                                    |                                      |

|              | have a test for every core are added to the test set                                                                                      | 41                                   |

| 4.4          | Critical paths for each core, based on STA results for tt corner,                                                                         | 4.77                                 |

| 4.5          | $V_{DD}=1.1 \text{ V}, \text{ T}=25 ^{\circ}\text{C}.$ Final path delay test set specifications, based on STA results for tt              | 47                                   |

| 4.0          | Final path delay test set specifications, based on STA results for the corner, $V_{DD}$ =1.1 V, T=25 °C.                                  | 47                                   |

| 4.6          | Average frequencies of simulated paths for cores 1 and 2 under typical                                                                    | т                                    |

| 1.0          | conditions: tt corner, $V_{DD}$ =1.1 V, T=25 °C                                                                                           | 50                                   |

| 4.7          | Average frequencies of simulated paths for cores 1 and 2 under worst-                                                                     |                                      |

|              | case conditions: ss corner, $V_{DD}$ at minimum specification, T=125 $^{\circ}\mathrm{C}$                                                 | 53                                   |

| 4.8          | Average frequencies of simulated paths for cores 1 and 2 under worst-                                                                     |                                      |

|              | case conditions: ss corner, $V_{DD}$ at minimum specification, T=-40 °C                                                                   | 54                                   |

| 4.9          | Critical paths for each core, based on STA results for tt corner,                                                                         |                                      |

| 1 1 0        | $V_{DD} = 1.1 \text{ V}, \text{ T} = 25^{\circ} \text{C}$                                                                                 | 59                                   |

| 4.10         | Average frequencies of measured paths for samples A010, A028, and                                                                         | 01                                   |

| 4 1 1        | A029 (tt corner). Room temperature, $V_{DD}$ =1.0 V                                                                                       | 61                                   |

| 4.11         | Average frequencies of measured paths of sample C001 (ss corner).                                                                         | C A                                  |

| 1 19         | Room temperature, $V_{DD}$ =1.0 V                                                                                                         | 64                                   |

| 4.12         | Average frequencies of simulated paths for core 1 with tt corner, $V_{DD}$                                                                | 68                                   |

|              | at $0.99 \mathrm{V}, \mathrm{T}=25 ^{\circ}\mathrm{C}$                                                                                    | υð                                   |

# List of Acronyms

- **ABB** Adaptive Body Biasing

- ATPG Automatic Test Pattern Generation

- **BTI** Bias Temperature Instability

${\bf BTWC} \ {\rm Better-Than-Worst-Case}$

- ${\bf CGU}$  Clock Generation Unit

- ${\bf CPU}\,$  Central Processing Unit

- DCO Digitally Controlled Oscillator

- ${\bf DFT}\,$  Design For Test

- $\mathbf{DVS}\,$  Dynamic Voltage Scaling

- GPU Graphics Processing Unit

- HCI Hot Carrier Injection

- IC Integrated Circuit

- ${\bf JTAG}$  Joint Test Action Group

- LDO Low Dropout Regulator

- **PVT** Process, Supply Voltage, and Temperature

- **PVTA** Process, Supply Voltage, Temperature, and Aging

- ${\bf SE}~{\rm Scan}~{\rm Enable}$

- **STA** Static Timing Analysis

- SSTA Statistical Static Timing Analysis

- **STIL** Standard Test Interface Language

- $V_{th}$  Threshold Voltage

- **VRA** Variability Resilient Architectures

- **VRS** Variability Resilient Scheme

# Acknowledgements

Creating this thesis has been a long journey. I would like to thank a number of people for their help and support.

First of all, I would like to thank my supervisor at NXP, Bram Kruseman. Your support and guidance during the project could not have been any better. You always made time to have meetings and gave excellent feedback on my work. I really learned a lot.

Secondly, I would like to thank my supervisor at TU Delft, Said Hamdioui. Thanks to your feedback, I was able to give the work a more academic background. The meetings were always very useful and gave several opportunities to expand and improve the work.

I would also like to thank Mottaqiallah Taouil for attending several meetings and providing feedback on my work. Your immediate understanding of the project and also the technical work helped a lot.

Finally, I would like to thank Boris Ljevar for helping me a lot with the Cadence tools and Zavarin Gagov for dedicating a lot of his time to create the measurement setup.

Daniël Kraak Delft, The Netherlands January 22, 2016

1

This section serves as an introduction of this thesis. Section 1.1 discusses the impact of process variation. Section 1.2 addresses the state-of-the-art solutions. Section 1.3 describes the current shortcomings and the contributions this thesis makes. Finally, Section 1.4 presents the outline of the thesis.

## 1.1 Impact of Process Variation

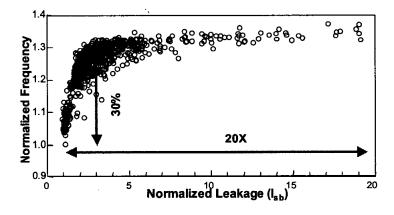

With the ongoing shrinking of semiconductor devices, the performance of Integrated Circuits (ICs) is improved. However, as the gates shrink further and further, ICs are more and more hampered by process variations, causing electrical parameters to vary. Process variations can negatively impact the the speed and power consumption of ICs. This is illustrated in Figure 1.1, which shows the distribution of frequency and standby leakage of ICs in a wafer for a 180 nm process. It can be seen there is a spread of around 30% in IC frequency and a spread of roughly 20x in standby leakage. This variation will only increase as technology shrinks further.

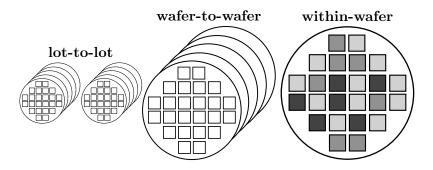

Process variations are usually categorized into global and local variations[6]. With global variations device parameters, such as the oxide thickness and dopant concentrations, change in an equal manner for all transistors. Process variations that are induced wafer-to-wafer, lot-to-lot, fab-to-fab, and within-wafer fall into this category. Local variations are caused by mismatch. Within-die variations fall under local variations. These process variations may negatively impact yield, as some produced ICs may not perform within specifications.

Traditionally, designers add margins to the design to make sure slow ICs will still run at the required speed. This design method is referred to as worst-case based design. With the increasing impact of process variations in modern technology, the worst-case based design method means a higher amount of area is wasted on these margins. This added area also negatively impacts power consumption. Therefore, with modern technology it is no longer sufficient to optimize on speed, as it can introduce a severe penalty in terms of area usage and power consumption.

These problems with worst-case based design for modern technology have led to the development of new design techniques, which guarantee high yield without compromising on area and power consumption. These techniques provide resilience against process variation, so a Better-Than-Worst-Case (BTWC) design approach can be used. The state-of-the-art techniques are discussed in the next section.

Figure 1.1: Impact of process variations on performance and power for ICs from the same wafer for a 180 nm process (from [1])

#### 1.2 State-of-the-Art

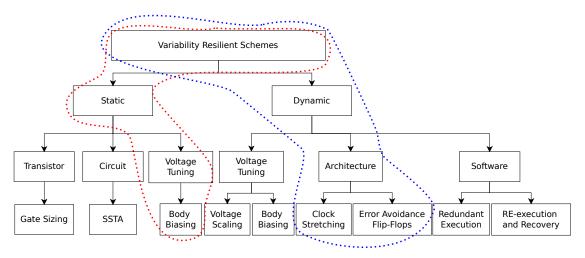

Figure 1.2 shows a classification diagram of the most common Variability Resilient Schemes (VRSs). It can be seen that VRSs are possible in a static and a dynamic fashion.

Static schemes can be applied at transistor level, circuit level, and even by tuning the supply voltage. An example of a technique at transistor level is Variation Aware Gate Sizing, where gates are sized against process variations to optimize for high yield and a good balance between power and performance[7, 8]. Statistical Static Timing Analysis (SSTA) is a popular circuit level technique. SSTA is an improved version of Static Timing Analysis (STA). With STA a circuit's timing is analyzed based on worstcase propagation times of logic gates. With SSTA the normal deterministic timing of gates is replaced with probability distributions. This way a more realistic estimate can be made of the speed of paths in an IC. Thanks to this technique an acceptable yield can be achieved without adding excessive margins[9]. Using body biasing it is possible to let a circuit run faster. After production the silicon speed of the IC is measured. When the produced silicon is slow, internal voltage regulators are programmed *once* to apply forward body biasing, so the circuit is able to run faster[10, 11].

With the dynamic schemes the circuit's behavior is constantly being monitored during runtime and when necessary action is taken. These schemes can also be called *sense and adapt* strategies[12]. Voltage tuning techniques can also be applied in a dynamic fashion. In this case, based on, for example, temperature or aging of the IC, body biasing[13] can be applied or dynamic voltage scaling[14] to make the IC faster or more power efficient. Techniques on the architectural level, such as clock stretching[15] and time borrowing[16] are meant to give the circuit extra time in order to avoid timing errors. With clock stretching the frequency of the clock is dynamically changed. With error avoidance flip-flops, long paths can borrow time from the succeeding clock cycle. This way timing errors are avoided. Finally, process variation resilience can also be addressed at the software level. An example of a software level technique is redundant execution. With redundant execution[17] critical portions of the program are run redundantly on multiple cores. The outputs are then compared to see if any errors are introduced. Another example is Re-execution and Recovery. Re-execution and Recovery focuses on reexecuting portions of the application that have been detected as being corrupted[18].

The work in this thesis is performed within the Variability Resilient Architectures (VRA) project<sup>1</sup>. The VRA project integrates and evaluates the *static* variant of body biasing, clock stretching, and error avoidance flip-flops (highlighted in Figure 1.2). Therefore, the work in this thesis will focus on these techniques only.

Figure 1.2: Classification diagram of Variability Resilient Schemes

## **1.3** Main Contributions

Circuits with VRSs run closer to their optimal performance and have less headroom. This means more extensive testing is necessary compared to conventional worst-case based designs. Also, the usage of elements that allow for time borrowing, such as error avoidance flip-flops bring new testability challenges. This thesis evaluates the three VRSs (body biasing, clock stretching, and error avoidance flip-flops) from the VRA project. Providing high quality ICs at high yield is needed for production and sales. Furthermore, increased test costs need to stay low enough. Otherwise, the money saved on area or earned on improved performance will be wasted on testing again.

This thesis makes the following contributions:

- Gives an overview of the three VRSs used in the VRA project.

- Creation of a cost model to compare cost of designs using VRSs with conventional design cost. Using this model the allowed increase of test cost can be estimated.

- Evaluation of testability of the error avoidance flip-flop. New testing methods are proposed.

- Evaluation of body biasing for a BTWC design using path delay testing.

<sup>&</sup>lt;sup>1</sup>The VRA project is a research project at NXP semiconductors[19].

## 1.4 Thesis outline

The thesis outline is as follows:

- Chapter 2 gives an overview of the VRSs used in the VRA project. The chapter ends with a comparison of the schemes.

- Chapter 3 discusses the evaluation methodology for the three VRSs.

- Chapter 4 describes the performed experiments and the results.

- Chapter 5 concludes the thesis and gives recommendations for future work.

Modern CMOS technologies suffer from increased process variation. This process variation impacts functionality, performance, reliability, and yield of devices. Therefore, Variability Resilient Schemes (VRSs) are proposed. They aim at the creation of design methods and solutions with the objective to minimize or prevent the impact of process variations and, therefore, achieve higher cost-effectiveness and better reliability. In this chapter, the variability resilience concept and the used schemes are discussed and compared. This chapter serves as background information. Section 2.1 discusses the types and effects of process variation. Section 2.2 provides a motivation for the need of VRSs. After this, the main VRSs are addressed: Body biasing in Section 2.3, the error avoidance flip-flop in Section 2.4, clock stretching in Section 2.5. Then, Section 2.6 discusses the advantages and disadvantages of these techniques. Finally, Section 2.7 concludes the chapter.

#### 2.1 Process Variation

Process variation refers to the occuring difference in device parameters of an Integrated Circuit (IC) due to fabrication, environmental, and temporal conditions. These variations affect the switching speed of the transistors in the circuit and thus the overall speed of the circuit. Therefore, these variations need to be taken into account during design. Otherwise, it cannot be guaranteed that the design will be able to run at the required speed. Process variation sources include Process, Supply Voltage, Temperature, and Aging (PVTA)[6].

Variations in the process are caused by imperfections in the manufacturing process (fabrication). This is, for instance, caused by imperfect lithographic process control and errors in alignment. This causes fluctuations in the width W and the length L of transistors, hence affecting the drive current of transistors. During the doping process atoms are randomly placed into the channels of transistors. This results in statistical variations of dopant atoms in the channels of transistors. This leads to variations of the Threshold Voltage  $(V_{th})$ , which directly affects the switching speed and drive strength of the transistor.

Environmental variations are caused by fluctuations in supply voltage and temperature. Supply voltage fluctuations are mainly caused by IR drop and di/dt noise. IR drop is caused by the voltage drop that occurs due to current going through the parasitic resistance of the power grid. Di/dt noise is caused by the parastic inductance of the power grid. The fluctuations in power supply voltage affect the delay of logic gates. The lower the supply voltage the higher the delay will be. The temperature in the IC varies due to the environment temperature. The temperature also varies on the IC, due to power dissipation in the transistors and wires. Regions in the IC with a lot of switching activity can create a high local temperature called a hot-spot. An increase in temperature makes a circuit typically slow down, due to reduced mobility of carriers and increased interconnect resistance.

Temporal variations are caused by aging effects. The aging effects cause the transistors to wear-out. Wear-out effects, such as Hot Carrier Injection (HCI) and Bias Temperature Instability (BTI) degrade the drive current of transistors during use. During design these wear-out effects need to be taken into account. Enough margin needs to be added to the design so it will continue to work throughout its lifetime under these effects.

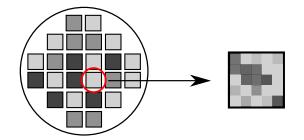

Besides categorizing variations into fabrication, environmental, and temporal variations, process variations are also often categorized into *local* and *global* variations[20]. With global variations, device parameters change in an equal manner for all devices on the IC. Process variations that are induced fab-to-fab, wafer-to-wafer, lot-to-lot, and within-wafer fall into this category (illustrated in Figure 2.1). Local variations refer to variations within a single IC. This variation is called within-die variation (illustrated in Figure 2.2).

Figure 2.1: Global variations can be recognized lot-to-lot, wafer-to-wafer, and within-wafer.

Figure 2.2: Local variation is the variation within a die, also called within-die variation

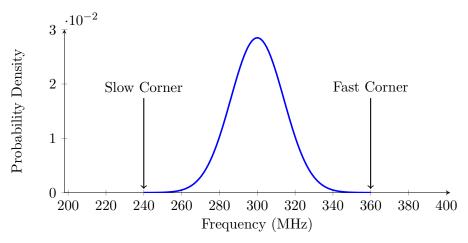

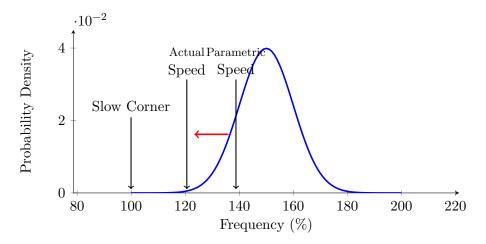

Due to the process variations some fabricated ICs will be slower and some will be faster. The speed of fabricated ICs is often modeled with a gaussian probability density function. Figure 2.3 shows an example probability density of the speed of an IC. The slow (ss) corner and the fast (ff) corner are indicated by arrows. The slow corner and the fast corner represent the most extreme cases of divergence from the nominal characteristics.

The norminal characteristics are often called the typical (tt) corner. For the slow corner the process variations are combined in such a way that the IC is the slowest possible. For the fast corner the process variations are combined in such a way so the IC is the fastest possible. The fast corner suffers from the highest leakage, so fast ICs have the highest power consumption.

At the end of the design phase of an IC, *corner lots* are usually produced. Corner lots are wafers which have been purposely skewed by a fab to a corner, such as so or ff corner[21]. Using the corner lots it can then be verified if the design is able to run at the required specifications (speed, power consumption) for all extreme cases of process variation.

Figure 2.3: Probability density function of the speed of an IC after fabrication.

#### 2.2 Motivation for Variability Resilient Schemes

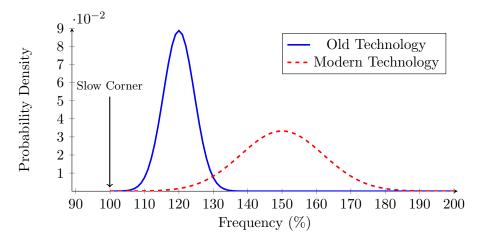

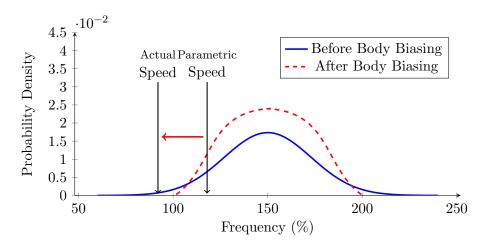

Figure 2.4 shows example distributions of silicon speed for old and modern technologies after manufacturing. As can be seen the distribution for modern technology is wider than the distribution for old technology. This happens because the variability is higher for modern technology. On average the modern technology is faster. Slow samples, however, have a performance similar to old technology.

For some designs, such as high performance Central Processing Units (CPUs) and Graphics Processing Units (GPUs), speed binning[22] is performed. This means the same design is sold at several maximum frequencies. Chips are tested extensively after manufacturing to determine their maximum frequency. The tests to determine the maximum frequency are very expensive[23]. However, chips with a bit more performance can be sold for more money. Therefore, it pays to do this extensive testing to determine which chips can be sold for a higher maximum frequency.

Some designs do not benefit from a higher maximum frequency. For instance, an audio chip just needs to run at a minimum target speed and does not benefit from running faster. For these chips speed binning is not an option. Therefore, in order to maximize yield, enough margin is built into the design to make sure also chips from the slow corner still meet the target frequency.

Adding enough margin to the design so even the chips from the slow corner are able to run at the target speed, is referred to as a worst-case based design. Also, the faster the silicon is, the higher the leakage, thus the higher the power consumption. Therefore, the worst-case parameters determine the specifications of the product. The slow corner determines the speed and the fast corner the power consumption. Due to the higher variability of modern technology, more margin needs to be built into the ICs to make sure chips from the slow corner will still meet the target frequency. When more margin is added to the chip it means the power consumption increases as well. Therefore, the slow corner and the fast corner are both responsible for competing specifications. With worst-case based design it is hard to optimize for both speed and power consumption at the same time.

VRSs minimize or prevent the effects of process variation, making the speed distribution of the manufactured chips more narrow again. VRSs enable slow silicon to run at higher frequencies. This way a Better-Than-Worst-Case (BTWC) design method can be used, as less margin needs to be added to make sure slow chips meet timing specifications. Furthermore, techniques are used to tune fast silicon to become less leaky, so the power consumption is reduced. With this area and power reduction a more cost effective use of modern technology is achieved.

Figure 2.4: Old versus modern technology speed distributions. The frequency denotes the normalized clock speed of the circuit.

## 2.3 Body Biasing

Body biasing is a technique that changes the transistor's threshold voltage. Body biasing is based on the transistor's *body effect*. The body effect models the threshold voltage change based on the voltage difference between the source and body of the transistor  $(V_{SB})$ . Normally, for an NMOS transistor the body is connected to ground, while for a PMOS transistor it is connected to  $V_{DD}$ . With body biasing the transistor bodies are connected to separate power networks instead of  $V_{DD}$  and ground. These power networks can either be supplied from off-chip or on-chip sources.

With forward body biasing the threshold voltage is lowered, making the transistor faster and leakier. Forward body biasing is done by applying a lower  $V_{SB}$  for an NMOS transistor. For a PMOS transistor the  $V_{SB}$  needs to be increased. Reverse body biasing raises the threshold voltage. This makes the transistor slower and less leaky. Reverse body biasing is done by applying a higher  $V_{SB}$  for an NMOS transistor and a lower  $V_{SB}$  for a PMOS transistor.

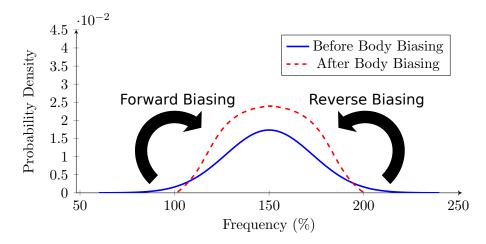

Body Biasing can be used to compensate the effects of global process variation. This is done by adding two extra power networks to the design that are used to control the body bias voltages of the NMOS and PMOS transistors. Furthermore, two on-chip sources are added that generate the body bias voltages. After the silicon is produced the characteristics of the silicon can be determined by measuring dedicated monitoring circuits, such as ring oscillators[24]. Based on the characteristics, for instance, fuses are set on the dies. These fuses control the on-chip sources for the body bias network. Chips with slow silicon can be made faster using forward body biasing. Chips with fast silicon can be made less leaky (and slower) using reverse body biasing.

In Figure 2.5 an example is shown of the probability distributions of silicon speed before and after body biasing. As can be seen the distribution with body biasing is a lot more narrow meaning effects of process variation are compensated.

Figure 2.5: Silicon speed distributions before and after body biasing

## 2.4 Error Avoidance Flip-Flop

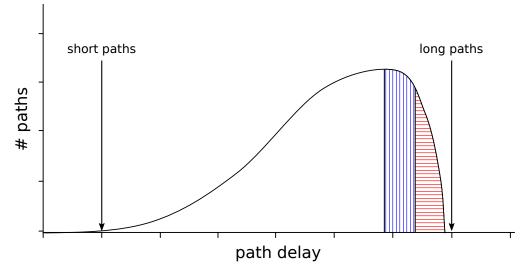

*Error avoidance flip-flops* can be used to counter both global and local process variation. The error avoidance flip-flop is a circuit that provides resilience against timing errors. Timing errors that arise when the propagation delay of a path exceeds the clock period are compensated by borrowing time from the successive clock cycle. The motivation for this arises from the study that only a small portion of the paths in a chip are critical paths[25]. Furthermore, the chance that two critical paths share the same flip-flop as

begin- and endpoint is small. This means most critical paths can borrow time from successive paths in the pipeline, because the successive path will still be able to finish within the reduced timing margin.

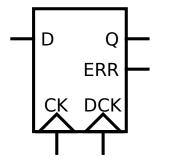

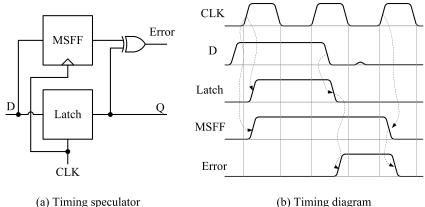

In Figure 2.6 the symbol of the error avoidance flip-flop is shown. Just like a normal D flip-flop it has a data input (D), a clock input (CK) and an output Q. The new signals are a delayed clock input (DCK) and an ERROR (ERR) output.

Figure 2.6: Error Avoidance Flip-Flop symbol

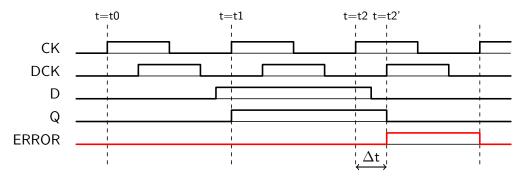

Figure 2.7 shows a timing diagram of the error avoidance flip-flop, illustrating how timing errors are compensated. Basically, an error avoidance flip-flop uses a delayed clock to resample the data input. By doing this, it checks for timing errors and corrects the output. At timestep t=t1, the D input changes within the normal clock period (CK). The D input is sampled and the sampled value is placed onto output Q. At timestep t=t2, a timing violation occurs: the new value for the D input is resolved too late and happens after the rising edge of the clock. The delayed clock is used to check for late transitions at the D input. The timing violation at timestep t=t2 is corrected at timestep t=t2': the data input is sampled at the rising edge of DCK and the Q output is updated with the correct value. Furthermore, the ERROR signal is raised, indicating a timing violation has occured.

Figure 2.7: Error Avoidance Flip-Flop waveform

The amount of timing violation that can be recovered equals the skew between the normal clock and the delayed clock, shown as  $\Delta t$  in Figure 2.7. The sampling with the delayed clock also puts a new constraint on the hold time at the D input. The hold time now needs to be increased with  $\Delta t$ . This means short paths in front of the data input

need to have sufficient delay, so the data input is not updated too early. If path delays are too short, there is a chance that the D input is updated before it is resampled with the delayed clock. In this case, the Q output is updated with the wrong value and the ERROR signal is raised unjustly.

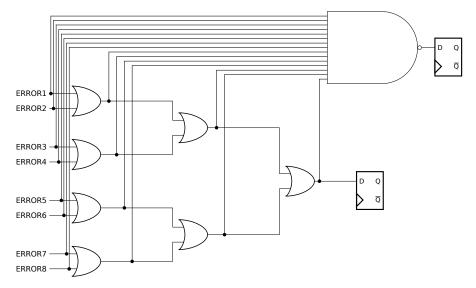

The ERROR signal of the error avoidance flip-flop can be used to inform a control unit that a timing error has occured. Based on the incoming ERROR signals, the control unit is able to detect when error avoidance is no longer possible. In this case the control unit can inform a higher system layer. For example, the software layer can be informed. The software layer is then responsible for performing a rollback and redoing the calculation at a lower frequency for instance.

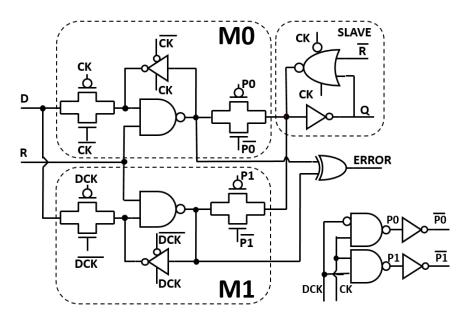

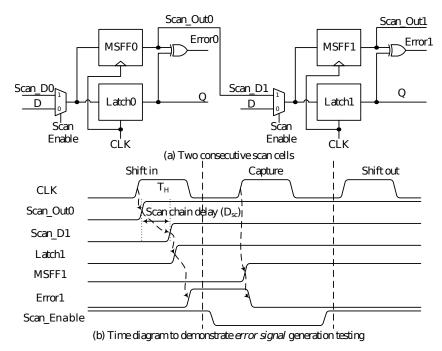

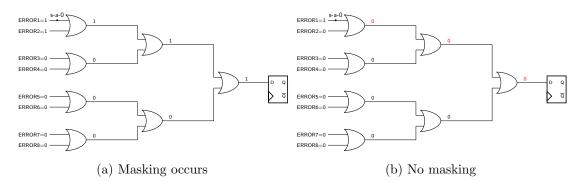

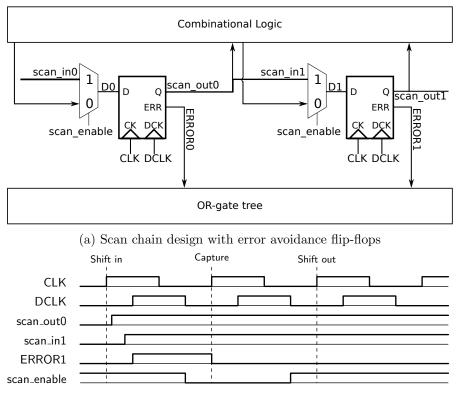

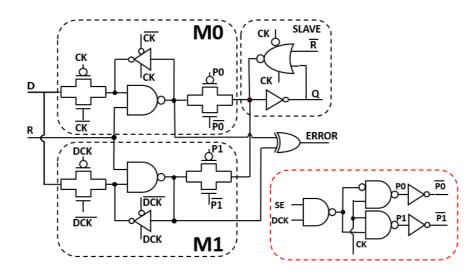

For the Variability Resilient Architectures (VRA) project the TIMBER flip-flop[2] is used. In Figure 2.8 the layout of the TIMBER flip-flop is shown. The TIMBER flip-flop consists of two master latches, M0 and M1, and a slave latch. Master latch M0 samples the D input at the rising edge of the normal clock and drives the slave latch with this value. Master latch M1 does this at the rising edge of the delayed clock.

Transmission gates control whether the value in latch M0 or M1 is passed to the slave latch. When P0 is low, latch M0 passes its captured value to the slave latch. For M1 this is the case, when P1 is low. The truth tables for the P0 and P1 are shown in Tables 2.1a and b. As can be seen latch M0 passes its value to the slave latch, when CK is high and DCK is low. M1 passes its value to the slave latch when both CK and DCK are high. This puts the constraint on the CK and DCK signals that the periods that they are high need to overlap.

The ERROR output is obtained by comparing the values saved in latches M0 and M1. If they are different, then a timing violation has occured and the ERROR signal needs to be raised. The ERROR signal is created by feeding the values in latches M0 and M1 to an XOR gate. The truth table for the ERROR signal is shown in Table 2.1c.

Figure 2.8: TIMBER Flip-Flop Circuit Design from ([2])

build 1.00

| CK | DCK | P0 | CK | DCK | P1 | M0 | M1 | ERRO |

|----|-----|----|----|-----|----|----|----|------|

| 0  | 0   | 1  | 0  | 0   | 1  | 0  | 0  | 0    |

| 0  | 1   | 1  | 0  | 1   | 1  | 0  | 1  | 1    |

| 1  | 0   | 0  | 1  | 0   | 1  | 1  | 0  | 1    |

| 1  | 1   | 1  | 1  | 1   | 0  | 1  | 1  | 0    |

|    | (a) |    |    | (b) |    |    | (0 | :)   |

Table 2.1: Thruth tables for (a) P0, (b) P1, and (c) ERROR signals

#### 2.5 Clock Stretching

Clock stretching is a technique that can be used to give critical paths in a design extra time to propagate. This is done by dynamically stretching the clock period, when a critical path is activated. In [26] clock stretching for arithmetic units, such as adders and multipliers is discussed. This is done by predicting when critical paths are activated. When this is the case the clock is stretched, giving the critical path more time to finish propagating. This approach is motivated by the fact that critical paths are rarely activated[10]. In conventional designs they do, however, determine the maximum frequency, hence maximum performance.

For the prediction of critical path activation a *decoder* is implemented. This decoder decides whether the clock should be stretched based on the input operands of the arithmetic unit. In [26] the clock stretching is mainly used to decrease power consumption, by using supply voltage scaling and reverse body biasing. This is possible, because the offcritical paths have plenty of timing margin and the critical paths have plenty of timing margin as well due to the clock stretching.

Instead of decreasing power consumption, it is also possible to save on area and/or increase performance. The VRA project investigates the potential of clock stretching to save area. Certain units in an IC can be built with less margin, meaning these units will not meet timing closure under all Process, Supply Voltage, and Temperature (PVT) conditions. A unit like this is referred to as a *relaxed unit*, indicating that the timing constraints have been relaxed. It must be noted here that the focus is not on performing clock stretching when a critical path is used, but on when a certain unit is used. This is mostly done, because it is easier to detect/predict if a certain unit is used.

In microprocessors arithmetic units such as the multiplier usually have high area overhead. These units are used relatively little. The idea is to build these units with less margin in order to save area. Using clock stretching the timing closure can still be met for all PVT conditions. This obviously occurs at a slight performance penalty, since the clock period is now longer. When only applying clock stretching when certain units in the IC are used, clock stretching can be used to provide resilience against global variation.

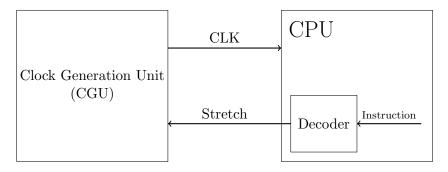

In Figure 2.9 an example design with a clock stretcher is shown. The design consists of a CPU and a Clock Generation Unit (CGU) that is responsible for providing the clock signal to the CPU. The CGU has an input signal *Stretch*. When this signal is

high, the CGU will stretch the clock period, giving the signals in the CPU more time to propagate. The CPU contains relaxed units such as the multiplier and divider. In the CPU a decoder is added that generates the Stretch signal. This decoder has as input the instruction that will be performed in the next cycle. If this instruction is a critical instruction that uses relaxed units, the Stretch signal is made high, indicating clock stretching is needed.

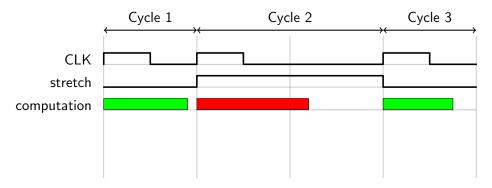

Figure 2.10 shows a waveform that shows how clock stretching works. In the waveform the CLK and stretch signal are shown. Furthermore, the *computation* signal indicates how long the execution actually takes (when all paths in the CPU have finished propagating). During cycle 1 a non-critical instruction is run, hence the stretch signal stays low. During cycle 2 a critical instruction is run. Therefore, the stretch signal is made high and the clock is stretched. In this case the clock is stretched to two times the clock period of the normal clock. During cycle 3, a non-critical instruction is run again, so the stretch signal is low again.

Figure 2.9: CPU design with clock stretcher

Figure 2.10: Clock stretcher operation

## 2.6 Advantages and Disadvantages

This section discusses the advantages and disadvantages of each scheme and compares them. A look is taken at area overhead, power consumption, and throughput.

#### 2.6.1 Body Biasing

In terms of area overhead for body biasing two extra power networks and also two body bias generators are added to the design. The two power networks connect to the body connections of the NMOS and PMOS transistors. There will hardly be any current going through these networks, however[13]. Therefore, the metal traces for these networks can be designed at minimum width. Furthermore, during design, the p-wells and n-wells of cells are connected to each other as much as possible. Figure 2.11 shows an example of the connection of the body bias power networks to the n- and p-wells. Using so-called *well-taps* the body bias power networks are connected to the n- and p-wells. Thus, it is not the case that every cell has a separate connection for the body. Therefore, there are relatively few places that the body bias network needs to be connected to. This will make the routing of the body bias power networks a lot easier. Considering this and the fact that the width of the metal for the body bias network can be made minimum width, the area overhead of the bias networks will be very minimum.

Also two body bias generators are needed to generate the body bias voltages. Usually, these body bias voltages are created with Low Dropout Regulators (LDOs). Again considering the low power requirements of the body bias network, these LDOs can be designed with very low area. In [27] a similar body biasing scheme to that of the VRA project is discussed. It uses two body bias generators as well, so body biasing can be applied for all NMOS and PMOS transistors in the IC. The area overhead of these generators and the additional routing of the body bias networks is estimated to be around 2%. Therefore, the area overhead of adding body biasing is small.

As said previously, there will hardly be any current going through the body bias networks. Therefore, the power consumption of body biasing will be very minimal.

When looking at the throughput of the design, it can be concluded that body biasing does not affect it. This is because slow silicon is tuned to become faster, so critical parts in the chips do not need extra time as with clock stretching for instance.

#### 2.6.2 Error Avoidance Flip-Flop

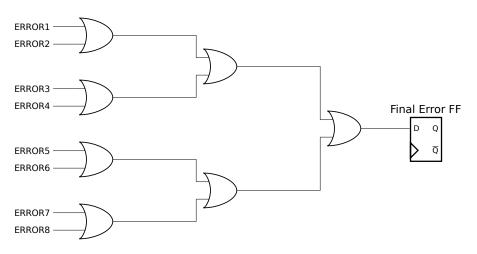

In terms of area overhead of the error avoidance flip-flop, there is the area overhead of the error avoidance flip-flop itself, the overhead of handling the ERROR signal, and the overhead of the delayed clock network. In the VRA project the TIMBER flip-flop is used. Compared to a normal flip-flop it uses an extra latch (M1), there is added logic for creating the P0 and P1 signals and and XOR gate is added for the ERROR signal. With this added logic, the TIMBER flip-flop is about twice as big as a normal flip-flop. Not all flip-flops need to be replaced with error avoidance flip-flops. Only the flip-flops that are the endpoint of a critical path. According to [2] about 50% of the flip-flops are the endpoint of a critical path. Replacing all these flip-flops will create a big area overhead. Because of this, it seems more feasible to only design parts of the system with less margin and add error avoidance flip-flops there to provide resilience to process variation. Furthermore, logic needs to be added to handle the ERROR signals. The ERROR signals are most likely captured at a central place in the design, so possibly the signal needs to travel a big distance. This means the logic needs to optimized for speed and will, therefore, have an increased area.

Figure 2.11: GDSII image showing the body bias power networks that connect using well-taps to the n- and p-wells

Also, a delayed clock is needed for the error avoidance flip-flop. This clock needs a certain timing relation to the normal clock. Usually it is already hard to control clock skew for one clock network. The problem of controlling the clock skew can be solved by delaying the normal clock using buffers. If every error avoidance flip-flop uses a buffer to generate the delayed clock from the normal clock, the delayed clock will have a well-defined clock skew to the normal clock. The problem of controlling the clock skew between the normal and delayed clock is solved with this. Obviously, this does cost an extra buffer per error avoidance flip-flop, which will cost a lot of area. To save some area it is possible to only use one buffer for error avoidance flip-flops that are close to each other. With this buffer a common delayed clock is then created for this group of nearby error avoidance flip-flops. Due to the area overhead of the error avoidance flip-flop itself, the overhead of handling the ERROR signal and the overhead of the delayed clock network, it can be expected that the total area overhead of the error avoidance flip-flop is rather high.

The power consumption that error avoidance flip-flops add is most likely high as well due to the high area overhead. Furthermore, the extra clock network for the delayed clock adds more switching activity increasing power consumption even more.

An advantage of error avoidance flip-flops is that one of the main goals is to only affect throughput when necessary. This is the case, because the timing error is compensated by borrowing time from the succeeding clock stage. Only when there are too many errors and error avoidance is no longer possible (when this happens depends on the implementation), the throughput will be affected. This is because in this case the system needs to redo the calculation at, for instance, a lower frequency.

#### 2.6.3 Clock Stretching

For clock stretching the area overhead lies in a CGU with the option to stretch the output clock and a decoder that determines when the clock needs to be stretched. The area overhead of the CGU and the decoders depends on how advanced the implementation of clock stretching is. For the CGU it depends on which precision of clock stretching is desired. Stretching the clock a whole cycle is easy, as it means the clock output of the CGU should be blocked for one cycle. If the clock needs to be stretched for, for instance, one tenth of the clock period, a clock with a higher speed than the output clock is needed to generate the output clock.

The area overhead of the decoder also depends on how advanced the implementation of clock stretching is. If the clock stretching is only based on which instruction is performed it can be implemented with a relatively low area overhead. If it is based on input vectors to arithmetic units such as the adder or multiplier a higher area overhead can be expected, as the input operands contain more bits.

Just like with the area overhead of clock stretching, the power consumption also depends on the complexity of the implementation. If clock stretching is based on the instruction that is performed the decoder will have low area overhead, thus also a low power consumption. If the clock stretching scheme is more complicated, for instance, based on the input vectors to arithmetic units the power consumption will increase.

A disadvantage of clock stretching is that it affects throughput. This happends because cycles in which the clock is stretched take longer. The penalty in performance depends on the added delay to the cycle, when clock stretching is applied.

#### 2.6.4 Comparison