Streaming FPGA Based Multiprocessor Architecture for Low Latency Medical Image Processing

Roelof Willem Heij

CE-MS-2016-15

## Abstract

In this work a fast and efficient implementation of a Field Programmable Gate Array (FPGA) based, fixed hardware, streaming multiprocessor architecture for low latency medical image processing is introduced. The design of this computation fabric is based on the p-VEX Very Long Instruction Word (VLIW) softcore processor and is influenced by architectures of modern Graphics Processing Unit (GPU) implementations. The computation fabric is capable of exploiting several types of parallelism, including pipelining, Instruction-level Parallelism (ILP) and Data-level Parallelism (DLP). The multiprocessor in the fabric is implemented by a chain of p-VEX processors that function as a processor pipeline. A memory architecture to support the high throughput of this processor pipeline has been created, making the computation fabric capable of stream processing. The basic building blocks of this memory architecture are single cycle accessible, dual port scratchpad memories. A total of 16 instances of the computation fabric are implemented on a Virtex-7 FPGA, creating an array of multiprocessors that is capable of processing 43.52 images per second when running a typical medical image processing algorithm workload on an operating frequency of 193 MHz. This makes the implementation suitable for real-time medical image processing. The processor pipeline depth of the computation fabric is generic, and can be changed according to the requirements posed by the algorithm workload. This makes the architecture flexible and general enough to handle changes and updates to the algorithm workload.

Computer Engineering Laboratory

Delft University of Technology

## Streaming FPGA Based Multiprocessor Architecture for Low Latency Medical Image Processing

## THESIS

submitted in partial fulfillment of the requirements for the degree of

## MASTER OF SCIENCE

in

## COMPUTER ENGINEERING

by

Roelof Willem Heij born in Krimpen aan den IJssel, The Netherlands

Computer Engineering Department of Electrical Engineering Faculty of Electrical Engineering, Mathematics and Computer Science Delft University of Technology

## Streaming FPGA Based Multiprocessor Architecture for Low Latency Medical Image Processing

### by Roelof Willem Heij

### Abstract

In this work a fast and efficient implementation of a FPGA based, fixed hardware, streaming multiprocessor architecture for low latency medical image processing is introduced. The design of this computation fabric is based on the  $\rho$ -VEX VLIW softcore processor and is influenced by architectures of modern GPU implementations. The computation fabric is capable of exploiting several types of parallelism, including pipelining, ILP and DLP. The multiprocessor in the fabric is implemented by a chain of  $\rho$ -VEX processors that function as a processor pipeline. A memory architecture to support the high throughput of this processor pipeline has been created, making the computation fabric capable of stream processing. The basic building blocks of this memory architecture are single cycle accessible, dual port scratchpad memories. A total of 16 instances of the computation fabric are implemented on a Virtex-7 FPGA, creating an array of multiprocessors that is capable of processing 43.52 images per second when running a typical medical image processing algorithm workload on an operating frequency of 193 MHz. This makes the implementation suitable for real-time medical image processing. The processor pipeline depth of the computation fabric is generic, and can be changed according to the requirements posed by the algorithm workload. This makes the architecture flexible and general enough to handle changes and updates to the algorithm workload.

| Laboratory<br>Codenumber |   | Computer Engineering<br>CE-MS-2016-15   |  |  |

|--------------------------|---|-----------------------------------------|--|--|

| Committee Members        | : |                                         |  |  |

| Advisor:                 |   | dr. ir. Zaid Al-Ars, CE, TU Delft       |  |  |

| Chairperson:             |   | dr. ir. Stephan Wong, CE, TU Delft      |  |  |

| Member:                  |   | dr. ir. Chris Verhoeven, ELCA, TU Delft |  |  |

Dedicated to my fiancée Sarah, and to my parents

## Contents

| List of Figures  | ix  |

|------------------|-----|

| List of Tables   | xi  |

| List of Acronyms | xiv |

| Acknowledgements | xv  |

| 1        | $\mathbf{Intr}$ | oduction 1                                         |

|----------|-----------------|----------------------------------------------------|

|          | 1.1             | Context                                            |

|          | 1.2             | Problem definition                                 |

|          | 1.3             | Design constraints                                 |

|          | 1.4             | Related work                                       |

|          | 1.5             | Thesis outline                                     |

| <b>2</b> | Pro             | cessors for image processing 5                     |

|          | 2.1             | Computation platform comparison                    |

|          | 2.2             | $\rho$ -VEX analysis                               |

|          |                 | 2.2.1 VLIW design philosophy                       |

|          |                 | 2.2.2 $\rho$ -VEX design                           |

|          |                 | 2.2.3 Instructions                                 |

|          | 2.3             | GPU analysis                                       |

|          |                 | 2.3.1 Parallelism                                  |

|          |                 | 2.3.2 GPU design                                   |

|          |                 | 2.3.3 Instructions                                 |

|          | 2.4             | Capability analysis                                |

|          |                 | 2.4.1 Architecture                                 |

|          |                 | 2.4.2 Memory architecture                          |

|          |                 | 2.4.3 Instruction Set Architecture                 |

|          |                 | 2.4.4 Scheduling 21                                |

| 3        | Ima             | ge processing algorithms 23                        |

|          | 3.1             | Analyzing algorithms                               |

|          |                 | 3.1.1 Basic metrics and analysis                   |

|          |                 | 3.1.2 Analysis for parallel algorithm execution    |

|          | 3.2             | General image processing algorithms overview       |

|          |                 | 3.2.1 Image processing algorithm classes and types |

|          |                 | 3.2.2 Parallelizing image processing algorithms    |

|          | 3.3             | Medical imaging algorithms                         |

|          | 3.4             | Adaptation of algorithm workload                   |

|          |     | 3.4.1            | Contents                                                                                                                          |

|----------|-----|------------------|-----------------------------------------------------------------------------------------------------------------------------------|

|          |     | 3.4.2            | Requirement analysis                                                                                                              |

| <b>4</b> | Des | igning           | the computation fabric 35                                                                                                         |

|          | 4.1 | 0 0              | rements                                                                                                                           |

|          | 4.2 | -                | rm                                                                                                                                |

|          | 4.3 |                  | sor architecture                                                                                                                  |

|          | 4.4 |                  | tion set architecture                                                                                                             |

|          | 4.5 | Memor            | ry architecture                                                                                                                   |

|          |     | 4.5.1            | Memory type                                                                                                                       |

|          |     | 4.5.2            | Memory hierarchy                                                                                                                  |

|          |     | 4.5.3            | Caches                                                                                                                            |

|          | 4.6 | Proces           | sor pipeline                                                                                                                      |

|          |     | 4.6.1            | Multicore setup                                                                                                                   |

|          |     | 4.6.2            | Peripherals                                                                                                                       |

|          |     | 4.6.3            | Data handling                                                                                                                     |

|          |     | 4.6.4            | Complete design                                                                                                                   |

|          | 4.7 | Multi-           | fabric design                                                                                                                     |

|          | 4.8 |                  | tions $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $42$                                                                  |

| -        | т   | 1                | 1                                                                                                                                 |

| 5        | -   | lement           |                                                                                                                                   |

|          | 5.1 | 5.1.1            | 1                                                                                                                                 |

|          |     | -                |                                                                                                                                   |

|          |     | 5.1.2            |                                                                                                                                   |

|          |     | 5.1.3            |                                                                                                                                   |

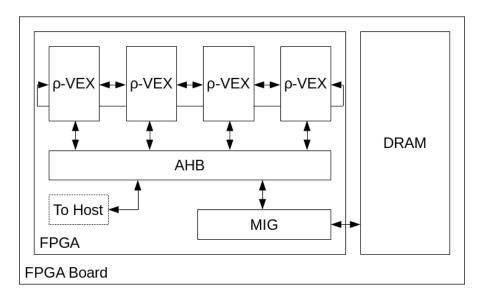

|          | 5.2 | 5.1.4<br>VC707   | 1                                                                                                                                 |

|          | 0.2 | 5.2.1            | 1                                                                                                                                 |

|          |     | -                |                                                                                                                                   |

|          |     | $5.2.2 \\ 5.2.3$ |                                                                                                                                   |

|          |     |                  | Operating frequency                                                                                                               |

|          |     | 5.2.4            | Multi-fabric implementation                                                                                                       |

| 6        | Mea | asurem           | ents and results 51                                                                                                               |

|          | 6.1 | Experi           | mental setup $\ldots \ldots 51$        |

|          |     | 6.1.1            | Input dataset                                                                                                                     |

|          |     | 6.1.2            | Used algorithm workload 51                                                                                                        |

|          |     | 6.1.3            | Processor configurations                                                                                                          |

|          |     | 6.1.4            | Resource utilization                                                                                                              |

|          | 6.2 | Evalua           | tion results $\ldots \ldots 52$ |

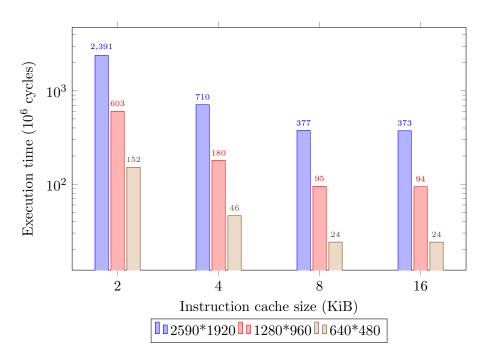

|          |     | 6.2.1            | Varying memory sizes                                                                                                              |

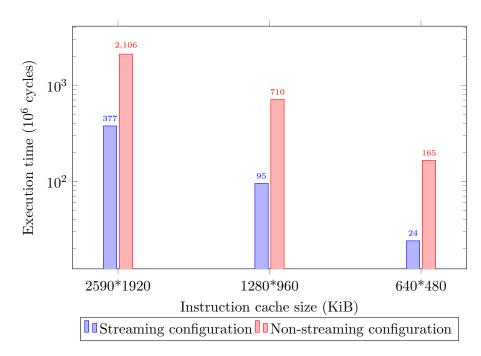

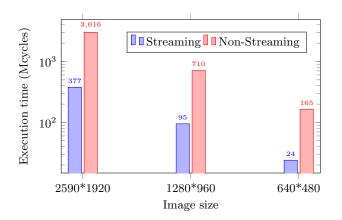

|          |     | 6.2.2            | Streaming versus non-streaming 54                                                                                                 |

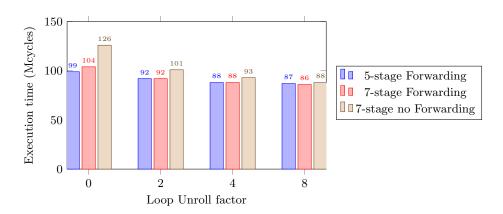

|          |     | 6.2.3            | Processor architecture considerations                                                                                             |

|          |     | 6.2.4            | Image processing performance                                                                                                      |

|          |     | 6.2.5            | ML605                                                                                                                             |

|          |     | 626              | VC707 58                                                                                                                          |

| <b>7</b>     | Con   | clusion and recommendations                  | <b>59</b> |

|--------------|-------|----------------------------------------------|-----------|

|              | 7.1   | Conclusions                                  | 59        |

|              |       | 7.1.1 Summary                                | 59        |

|              |       | 7.1.2 Main accomplishments and contributions | 59        |

|              | 7.2   | Recommendations for future work              | 60        |

| Bi           | bliog | graphy                                       | 65        |

| $\mathbf{A}$ | Pub   | olication                                    | 67        |

# List of Figures

| 2.1          | Graphical overview of computation platform exploration for                                                                                   | 8  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2          | Computer system with an Intel Central Processing Unit (CPU), adapted                                                                         |    |

|              | from $[1]$                                                                                                                                   | 13 |

| $2.3 \\ 2.4$ | Basic GPU architecture, adapted from [1]                                                                                                     | 14 |

|              | layer $[1]$                                                                                                                                  | 17 |

| 3.1          | Visual impression of two consecutive steps of a frame-based algorithm                                                                        |    |

|              | that uses a sliding window.                                                                                                                  | 29 |

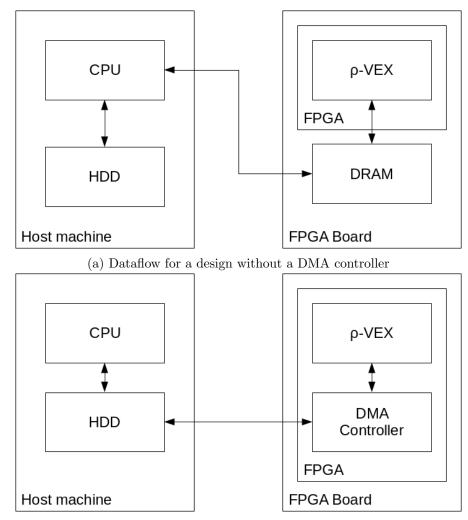

| 4.1          | Schematic representations dataflow in two possible designs                                                                                   | 41 |

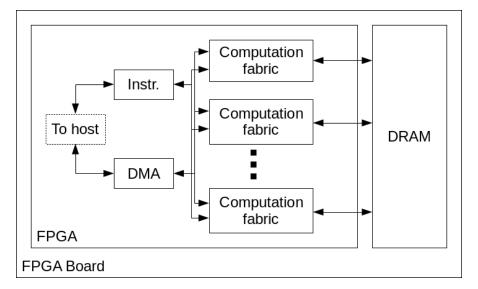

| 4.2          | The final design for the computation fabric                                                                                                  | 42 |

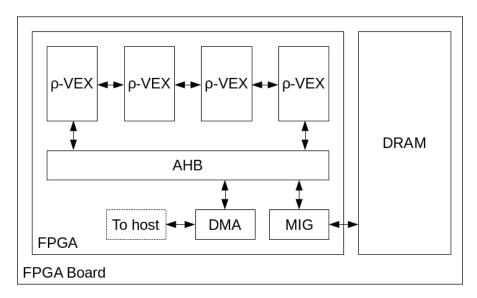

| 4.3          | The final design for a system with multiple instances of the computation fabric                                                              | 42 |

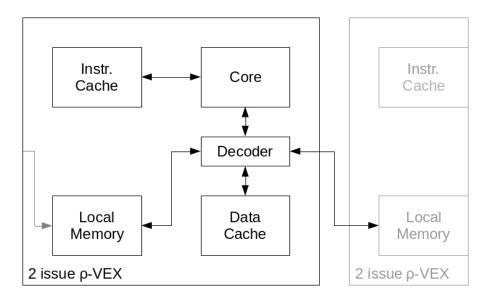

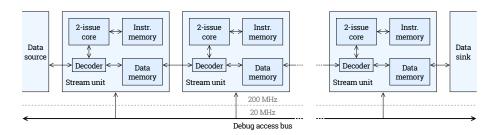

| 5.1          | Overview of the implemented processor for the computation fabric. The<br>gray shapes show how a processor pipeline can be formed by chaining |    |

|              | multiple processors.                                                                                                                         | 47 |

| 5.2          | Overview of the implemented computation fabric                                                                                               | 48 |

| 6.1          | Execution times for configurations featuring a 32 KiB local memory $~$                                                                       | 54 |

| 6.2          | Execution times for streaming and non-streaming configurations with 32                                                                       |    |

|              | KiB local memories and 8 KiB instruction caches                                                                                              | 55 |

# List of Tables

| $2.1 \\ 2.2$ | Overview of computation platform exploration                                                                                               | 7  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------|----|

|              | - Part 1                                                                                                                                   | 20 |

| 2.3          | VEX and PTX overview - Part 2                                                                                                              | 21 |

| 3.1          | Relevant selection of operators from Bachmann-Landau family                                                                                | 24 |

| 3.2          | Complexity analysis of the selected algorithms                                                                                             | 32 |

| 3.3          | Profiling of created algorithm workload                                                                                                    | 32 |

| 4.1          | Overview of FPGA specifications                                                                                                            | 36 |

| 4.2          | Simulation results for streaming and non-streaming implementation of the computation fabric                                                | 43 |

| 6.1          | Processor configurations used for benchmarking                                                                                             | 52 |

| 6.2          | Execution times for configurations with varying memory sizes                                                                               | 53 |

| 6.3          | Execution times for streaming and non-streaming configurations. The values indicated in red are produced through interpolation, because of |    |

|              | limitations in the simulation environment.                                                                                                 | 55 |

| 6.4          | Speedup for streaming and non-streaming configurations.                                                                                    | 56 |

| 6.5          | Resource utilization comparison standard rVEX and new design                                                                               | 56 |

| 6.6          | Resource utilization for varying pipeline depths                                                                                           | 58 |

| 6.7          | Resource utilization per core and of peripherals                                                                                           | 58 |

| 6.8          | Total number of cores and processor pipelines that can be implemented                                                                      |    |

|              | on the Virtex-6 FPGA                                                                                                                       | 58 |

## List of Acronyms

- **AHB** Advanced High-performance Bus

- ALU Arithmetic Logic Unit

- **AMBA** Advanced Microcontroller Bus Architecture

- **ASIC** Applications Specific Integrated Circuit

BRAM Block Random Access Memory

- **CPU** Central Processing Unit

- CUDA Compute Unified Device Architecture

- ${\bf DLP}\,$ Data-level Parallelism

- **DSP** Digital Signal Processing

- **DMA** Direct Memory Access

- **DRAM** Dynamic Random Access Memory

- FPGA Field Programmable Gate Array

- GPU Graphics Processing Unit

- **ILP** Instruction-level Parallelism

- **ISA** Instruction Set Architecture

- LUT Look-Up Table

- MIG Memory Interface Generator

- **OpenCL** Open Computing Language

- NOP No Operation

- **PCIe** Peripheral Component Interconnect Express

- **PTX** Parallel Thread Execution

- **RAM** Random Access Memory

- SFU Special Function Unit

- **SIMD** Single Instruction Multiple Data

- **SIMT** Single Instruction Multiple Threads

- **SM** Streaming Multiprocessor

${\bf SP}$ Streaming Processor

${\bf SRAM}$  Static Random Access Memory

${\bf TLP}\,$  Thread-level Parallelism

$\mathbf{TPC}$  Texture/Processor Cluster

$\mathbf{VEX}\ \mathrm{VLIW}\ \mathrm{Example}$

$\mathbf{VHDL}$  Very High Speed Intergrated Circuit Hardware Description Language

$\mathbf{VLIW}$  Very Long Instruction Word

## Acknowledgements

There are a lot of people that have helped me in the course of my thesis project. I want to express my gratitude to all of you.

First I would like to thank my thesis advisor Zaid, for his endless patience and support. Even at times when the work on my thesis project had seemingly come to a standstill and I was completely drained of motivation, he would be nothing but enthusiastic and encouraging. I would also like to thank Stephan Wong for chairing my committee, and Chris Verhoeven for being part of my committee.

Joost and Jeroen have also been extremely helpful and supportive. Whenever I encountered trouble or issues in my work, I could always count on them to help me sort them out.

I would also like to thank all the marvelous master students that have accompanied me in the MSc Lab of the CE group. Especially Haji and Koray have really helped and motivated me in the final months of my thesis project.

A special thanks goes to my parents, for supporting me in every possible way, in spite of the enormous burden they bear.

Finally I would like to express my gratitude to my wonderful fiancée Sarah. She has shown an incredible amount of patience and support on a daily basis. Words can't describe what she means to me.

Roelof Willem Heij Delft, The Netherlands November 27, 2016

## Introduction

## 1.1 Context

Image processing has become increasingly complex and resource consuming over the years. Traditionally, the computers Central Processing Unit (CPU) took care of all operations in a computer system, including image processing. In 1999, the introduction of a designated piece of hardware suited for image processing on desktop computers, mainly referred to as a Graphics Processing Unit (GPU), marked a new era for image processing [2]. Nowadays there are various forms of processors which are widely used in everyday life. These forms include CPU, GPU, Applications Specific Integrated Circuit (ASIC) and Field Programmable Gate Array (FPGA). There is no single best solution for every image processing task, so for each application one should consider all options in order to acquire optimal performance.

Besides increasingly complex and resource consuming, image processing is also becoming more common and crucial in many sectors. Examples include health care, security and computer vision. Because of the high social, industrial and academic value of image processing, a tremendous amount of research aiming to make image processing faster and more efficient is conducted. An example of this is the Almarvi (Algorithms, Design Methods, and Many-core Execution Platform for Low-Power Massive Data-Rate Video and Image Processing) project. This project is a collaboration between several technical universities and several leading companies, and aims to reduce some of the technical difficulties in this area [3]. The Delft University also takes part in this project. To some extend, the work for this thesis project is conducted as a part of the Almarvi project.

## **1.2** Problem definition

Image processing tasks are considered to be relatively compute intensive, and can consume vast amounts of resources and time when performed in traditional, sequential ways of computation. This is a problem in certain cases, for instance whenever images have to be processed in real time. An example case where real time processing is paramount is in medical imaging. Medical imaging is the technique that aims to visualize the interior of a body. This technique has numerous clinical advantages for both the patient and the surgeon. However, the high computational complexity of medical imaging makes real time processing in a traditional way impossible.

Luckily some medical imaging processing algorithms are suited for parallel execution. By parallelizing the execution of these algorithms, their execution time can be drastically reduced. Using hardware that can provides good conditions for parallel execution, real time processing can be made possible. The goal of this thesis project is to design a computation fabric that is able to make real time image processing for medical imaging applications possible.

One of the requirements for medical image processing hardware (or so-called computation fabrics<sup>1</sup>) stated by Philips in the Almarvi project is that the performance of the computation fabric desired for their commercial medical imaging product has to be ensured over time. Medical imagers have a high expected lifetime of up to twenty years, while that of the computation fabrics that support these products has a lifetime of around five years. This unusually long lifetime requirement poses challenges on the development and maintenance cycle of these computation fabrics. Since performance portability between computing platforms<sup>2</sup> cannot always be ensured and re-designing, re-optimizing and re-testing of computing platforms, it is desirable to have a fixed hardware platform.

Another requirement is that the medical image processing hardware should be able to process images real-time. For this to be possible, a minimum performance of 15 processed frames per second should be achieved. To allow the human eye to optimally interpret the stream of processed images, a performance of 30 frames per second is desired.

Based on this problem definition, the following research questions can be formulated.

- Is it possible to design and implement a fixed hardware image processing computation fabric that meets the requirements to be used in commercial grade medical imaging products?

- Can we create a computation fabric that is general enough to handle changes and updates to the image processing algorithms used in the field?

## **1.3** Design constraints

The starting point of the computation fabric is the  $\rho$ -VEX Very Long Instruction Word (VLIW) softcore processor that is being developed by the Computer Engineering Department of the Delft University of Technology [4] [5]. Choosing the  $\rho$ -VEX processor as a starting point for our fabric mainly serves academic purposes. However, a recent study indicated the remarkable processing power of the  $\rho$ -VEX processor in comparison to other, commercial grade softcore processors [6]. For academic purposes the source code of this processor is made available, enabling us to implement it in our image processing computation fabric [7].

The computation fabric should preferably be implemented on an FPGA. There are two reasons for this. Firstly, Philips has indicated to be interested in FPGA-based solutions. Secondly the  $\rho$ -VEX processor developed by the Delft University of Technology is a softcore processor that is designed and maintained on an FPGA. Because of this, a complete toolchain and development environment are already available and ready for use on an FPGA.

$<sup>^1\</sup>mathrm{We}$  define a computation fabric as a piece of hardware dedicated to a certain task, like processors and accelerators.

<sup>&</sup>lt;sup>2</sup>We define a computing platforms as the physical types of hardware a computing fabric can be implemented on. Examples are ASIC and FPGA.

## 1.4 Related work

Acceleration of image processing tasks is a large field in computing. A prior study on using the  $\rho$ -VEX processor for image processing applications is performed in [6]. This thesis project aims to fulfill parts of the references for future work mentioned in that paper.

There are numerous works on FPGA based image processing. In [8], an FPGAbased compute fabric is proposed using the LE-1 softcore, which is based on the same Instruction Set Architecture (ISA) as the  $\rho$ -VEX, targeting medical image processing applications. This work focuses solely on offering a highly multi-threaded platform without providing a memory hierarchy that can sustain the needed bandwidth through the pipeline. A related study on accelerating workloads without compromising programmability is [9], with one of the design points being a convolution engine as processing element. A well-known prior effort, and one of the inspirations of this work, uses softcore processors to provide adequate acceleration while staying targetable by a high level compiler is the Catapult project [10]. The target domain is ranking documents for the Bing search engine. A related effort that aims to accelerate Convolutional Neural Networks is [11]. However, that project did not aim to conserve programmability but only run-time reconfigurability, as the structure of this application does not change enough to require this.

We are not aware of any other implementation of an independent FPGA based computation fabric that supports streaming medical image processing. None of the related works shows an implementation or a design of an independent FPGA based image processor that uses streaming. Existing implementations and designs related to streaming image processing on FPGAs all function as accelerators or co-processors [12][13][14], while existing implementations and designs of independent (image) processors on FPGAs do not use streaming [15][16][17][18][19].

## 1.5 Thesis outline

Chapter 2 provides background information on the characteristics of the  $\rho$ -VEX softcore processor and on image processing accelerators. A capability analysis based on this information will be used to point out what characteristics the desired computation fabric should implement. Chapter 3 first gives a short introduction to algorithm analysis of both sequential and parallel algorithms. This is followed by a broad overview of image processing algorithms. After this, an algorithm workload for medical imaging purposes is constructed. Chapter 4 describes the design of the computation fabric based on the requirements posed by the constructed algorithm workload that is formulated in the previous chapter. Chapter 5 shows how the design is implemented on an FPGA that is able to communicate with several peripherals and a host machine. Chapter 6 describes the measurement setup for the computation fabric and reports the results of these measurements. Chapter 7 ends this thesis with a conclusion on the achieved results and recommendations for future work. The aim of this thesis project is to design and implement a computation fabric that is capable of fast and efficient execution of image processing algorithms. Preferably it should also meet the desired requirements for a real-life use case, the Interventional X-Ray System by Philips. Preferably the computation fabric should also be suited for executing general purpose tasks. In order to be able to describe a design for this fabric, it might be helpful to look into the designs of other (image) processors. Also looking into other computation platforms might be helpful, even though the computation platform for our computation fabric has already been chosen to be a Field Programmable Gate Array (FPGA). Investigating other computation platforms will help to identify the strong points and weak points of the FPGA compared to the other computation platforms, which will in turn help us with design considerations when creating the computation fabric.

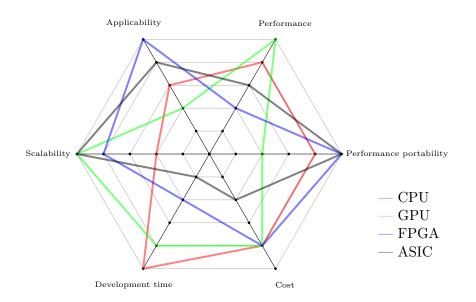

This chapter will start with a computation platform comparison, exploring the pros and cons of four computation platforms, namely the Central Processing Unit (CPU), Graphics Processing Unit (GPU), FPGA and Applications Specific Integrated Circuit (ASIC). This is followed by a study on two processors relevant to our computation fabric. These are the  $\rho$ -VEX processor, that will be used as starting point for our fabric, and the GPU, which is designed with a special focus on image processing. The chapter is concluded by a discussion on the pros and cons of the  $\rho$ -VEX and the GPU in light of our target application, in order to determine what parts and properties are desirable for implementation in our fabric. [36–46]

## 2.1 Computation platform comparison

Both Philips and the TU Delft have indicated that the FPGA is the platform of their preference. However, as stated in Section 1.2, processors and accelerators can be implemented on various types of hardware. There is no single best platform for all applications types, since all of them have very different capabilities and limitations. For this reason, all of the possible platforms will be shortly examined and compared in terms of various characteristics. They are summarized below.

- **Performance** This metrics indicates the capability of processing operations and data in a certain amount of time. Higher is better.

- **Performance portability** This metric indicates how well performance is maintained whenever the code that needs to be executed is ran on another device of the same type. Higher is better.

- Scalability This metric indicates the capability of improving the overall performance by adding more hardware of the same sort. Higher is better.

- **Applicability** This metric indicates how wide the range of applications is that can be executed efficiently. Higher is better.

- **Development time** This metric indicates the time needed for developing an implementing of a processor or accelerator and/or the porting of needed software to this processor or accelerator. Less time is obviously better. However, to avoid confusion in the overview; higher is better.

- **Cost** The metric indicates the cost of the hardware itself and does not take development time or other costly factors into account. Less costs are obviously better. However, to avoid confusion in the overview; higher is better.

**CPU** This platform is probably the most well-known and widespread of all. The ubiquitous CPU is present in every computer, where it functions as the main controller of the system. In order to fulfill this role, the CPU is capable of executing an enormous amount of different operations and tasks. It is able to handle and perform tasks with high complexity in an efficient way. However, the CPU is not able to process vast amounts of data or instructions per second because this is fundamentally in conflict with the support of high complexity tasks. Performance is scalable to a certain extent. CPUs of the same brand are in most cases backwards compatible and will deliver equal or better performance when an application that is written for a certain CPU is ported to a newer CPU. The development time for CPUs is low. They can be targeted using a large range of programming languages. The cost of purchasing a consumer grade CPU is relatively low.

**GPU** The time that GPUs were used for image processing only is long gone. The capability of GPUs to be used as accelerators for all sorts of algorithms and other compute intensive tasks is being exploited widely, especially in academia and the industry. A small range of large problems can be executed orders of magnitude faster on GPUs because of their ability to process huge amounts of data at once. However, portability is a big issue. Equal or better performance can not be guaranteed when porting a program to a newer GPU. In fact, there have even been reports of reduced performance when porting programming code to newer devices. The performance of GPUs is very scalable. The existence of GPUs of over a thousand cores and systems with multiple GPUs support this fact. Development time for GPU is relatively low thanks to the programming languages that allow programmers to target GPUs in an easy and familiar way. The cost is comparable to that of the CPU.

**FPGA** While CPUs and GPUs are fixed pieces of hardware, FPGAs are reprogrammable. Users can design their own desired hardware and upload it to the FPGA, and revise it if necessary. This allows users to create piece of hardware that are tailored to their needs. The FPGA is a large array that contains three types of basic building blocks. These are the flip-flop register (mostly referred to as *Register* or *Reg*),

the Look-Up Table (LUT) and the Block Random Access Memory (BRAM). A synthesis, implementation and routing tool can translate a hardware design to digital logic that can be implemented in this array. The designs can be created in hardware programming languages like Very High Speed Intergrated Circuit Hardware Description Language (VHDL) or Verilog, which have stood the test of time very well. This guarantees the portability of hardware designs on FPGAs. Due to their nature FPGAs do not support high clock frequencies like the other platforms, but compensate for this by being optimized for the specific task that they are designed for. Research shows that acceleration on FPGAs is scalable. Unfortunately development time of custom hardware designs is extremely high, taking up to multiple years for complex designs. The price of FPGA development boards is slightly higher than that of CPUs or GPUs, but is still relatively low.

**ASIC** When implementing a custom VHDL or Verilog hardware design, ASIC is also an option. ASIC are generally faster than FPGAs because they can run at a higher frequency, but are not reconfigurable and generally have an even longer development time. The production costs of producing a single ASIC are extremely high, but become lower when producing larger quantities. ASICs theoretically have the same level of performance portability as FPGAs, but typically outperform FPGAs in terms of scalability.

**Conclusion** Figure 2.1 and Table 2.1 show that FPGA is indeed a viable option given that high performance portability, applicability and scalability are must-haves. For this reason the FPGA based  $\rho$ -VEX processor will be used as a starting point for the design of the accelerator. However, since the GPU is designed especially to support the processing of data in parallel by incorporating massive multithreading, inspecting this platform might provide viable information on architectural design choices when designing the image processing accelerator.

| Platform                | CPU | GPU | FPGA | ASIC |

|-------------------------|-----|-----|------|------|

| Performance             | +   | ++  | -    | +/-  |

| Performance portability | +   | -   | ++   | ++   |

| Scalability             | -   | ++  | +    | ++   |

| Applicability           | +/- | -   | ++   | +    |

| Development time        | ++  | +   | -    | -    |

| Cost                    | +   | +   | +    | -    |

Table 2.1: Overview of computation platform exploration

## 2.2 $\rho$ -VEX analysis

For academic purposes it is desired that the main building block for our fabric is the  $\rho$ -VEX softcore Very Long Instruction Word (VLIW) processor developed by the Computer Engineering department of the Delft University of technology that is based on the VLIW Example (VEX) Instruction Set Architecture (ISA). In order to design an architecture that incorporates this processor, it is important to understand its working, capabilities

Figure 2.1: Graphical overview of computation platform exploration for

and limitations. This section will first explain the concepts of VLIW. This is followed by a description of the architecture and working of the  $\rho$ -VEX processor.

## 2.2.1 VLIW design philosophy

VLIW is not a precisely defined methodology, but rather an architectural design philosophy. The VLIW methodology was introduced by Joseph Fisher et al. [20]. VLIW processors are naturally capable of exploiting Instruction-level Parallelism  $(ILP)^1$ , due to the fact that they are able to issue multiple instructions at the same time. In this way a VLIW processor is able to allow higher performance without adding any complexity to its design while doing so. Exploiting this form of parallelism does require an ILP-oriented compiler that can issue certain combinations of instructions in parallel, and possibly out of order.

Because of its natural support of parallelism, VLIW processors are promising for image processing tasks. One of the parameters that dictate the VLIW's capability of handling parallelism is its issue width. This indicates the width of the input size of the processor, and dictates how much operations can be processed in parallel. Note that the VLIW processor can only execute operations in parallel if the VLIW processor has enough resources available to perform all of them, and if there are no data dependencies between the operations.

## 2.2.2 $\rho$ -VEX design

Along with the VLIW design methodology, Joseph Fisher also introduced an accompanying ISA, called VEX. The Computer Engineering group of the Delft University of

$<sup>^1\</sup>mathrm{ILP}$  aims to increase the speed of a computing fabric by issuing and executing multiple instructions in parallel.

Technology implemented a reconfigurable VLIW processor based on the VEX ISA, and called the  $\rho$ -VEX processor. This section will discuss the architecture and characteristics of the  $\rho$ -VEX. The current design of the  $\rho$ -VEX is intended to be implemented on an FPGA, which is connected to a regular x86 host machine through a USB connection. Note that, even though the FPGA that implements the  $\rho$ -VEX processor is connected to a host machine, the  $\rho$ -VEX is an independent processor. The host machine is only used to program the FPGA and hand the scheduled instructions to the  $\rho$ -VEX.

### 2.2.2.1 Reconfigurability

The spear points of the  $\rho$ -VEX processor are the capabilities of reconfigurability and parameterizability. These allow the  $\rho$ -VEX processor to be tailored for a specific application in order to achieve high performance without having to redesign the processor in any way. The  $\rho$ -VEX is can be dynamically reconfigured and parameterized at design-time, and in same cases even at run-time. In its full form, the  $\rho$ -VEX is an eight-issue VLIW processor, created by combining four two-issue cores. Using this structure, the issue-width of the  $\rho$ -VEX can be parameterized to either two, four or eight. Moreover, the  $\rho$ -VEX supports an number of configurations that emulate multicore behavior. When configured as a multicore processor, all cores in the  $\rho$ -VEX work completely individual and have their own caches and memories. Possible configurations for the  $\rho$ -VEX are listed below.

The  $\rho$ -VEX can be configured as:

- A single eight-issue processor

- A single four-issue processor

- Two four-issue processors

- A single two-issue processor

- Two two-issue processors

- Four two-issue processors

- One four issue-processor and two two-issue processors

### 2.2.2.2 Processor architecture

The architecture of the  $\rho$ -VEX processor cores is an adaptation of the VEX processor, an example implementation of a VLIW processor. It is an ST200 series core based on technology jointly developed by Hewlett-Packard Laboraties and STMicroelectronics [21]. The VEX processor was created by the Joseph Fisher, the inventor of VLIW philosophy and employee of Hewlett-Packard Laboratories, to demonstrate the working of his VLIW ISA, which is simply called the VEX ISA. This ISA is also used by the  $\rho$ -VEX processor. Also the toolchain that was developed and released to accompany the VEX processor is being used as a part of the  $\rho$ -VEX toolchain [22]. In its full form the  $\rho$ -VEX processor features four two-issue  $\rho$ -VEX cores working together as a single eight-issue processor. Each of the two-issue cores implements a seven-stage pipeline that supports instruction forwarding. Each core has its instruction and data memory, implemented in the form of either caches of single-port memories. The following resources are available for implementation in each core:

- Arithmetic Logic Unit (ALU)

- Multiplication unit

- Branch unit

- Load/Store unit

- General Register file (GR) consisting of 64 32-bit registers with 4 write and 8 read ports

- Branch Register file (BR) with 8 1-bit registers

Out of the first four resources, the core can support a maximum of two. The last two are present in every core.

## 2.2.2.3 Communication and peripherals

The  $\rho$ -VEX processor allows internal communication between the cores, and between the  $\rho$ -VEX processor and peripherals. Whenever the processor is operating with an issue-width of four or eight, the collaborating cores can communicate over an all-to-all crossbar, relieving stress on the Advanced High-performance Bus (AHB) bus. Each core is connected to an AHB bus, that allows communication with other  $\rho$ -VEX processors, peripherals and the host machine. AHB is an Advanced Microcontroller Bus Architecture (AMBA)-based, open standard, on-chip bus developed by ARM. A debug bus allows the host machine to keep track of about everything that's going on inside the  $\rho$ -VEX processor.

## 2.2.2.4 Memory hierarchy

As stated in Section 2.2.2.2, each of the  $\rho$ -VEX cores implements a general register file. This register file is the lowest layer in the memory hierarchy, closest to the  $\rho$ -VEX core. It is used for storing intermediate results of operations and other information vital for the working of the core.

The second layer in the memory hierarchy is formed by either cache memories or regular, single-port memories, depending on the preferences of the user. The  $\rho$ -VEX supports cache memory as intrinsic parts of the  $\rho$ -VEX system. The cache consists of a separate data and instruction cache, both of which are reconfigurable in terms of size, associativity and replacement policy. However, the caches are optional components of the system and can be turned off at design-time, in which case they are replaced by a regular, single-port data and instruction memories.

Dynamic Random Access Memory (DRAM) forms the third layer of the memory hierarchy. This memory is located off-chip, but on the FPGA development board. It is significantly slower than the on-chip caches and memories, but accessing it is much faster than accessing memory on the host machine.

The highest layer in the memory hierarchy is the memory located on the host machine, and is in most cases represented by a hard disk drive. Accessing this memory is extremely time consuming and costly, because of three reasons. Firstly, the paths from the  $\rho$ -VEX core to this memory are long, making communication very time consuming. Secondly, the hard disk drive is relatively slow as compared to the others memory types. Thirdly and finally, while data is being fetched from the host machine's hard drive, the  $\rho$ -VEX processor is stalled, resulting in wasted time.

## 2.2.3 Instructions

Instructions for VLIW processors are more complex than instructions for conventional processors. To optimally exploit ILP, the VLIW processor should be able to process multiple operations in parallel. To accommodate this, two layers of abstraction are added to the instruction. A VLIW instruction is a collection of so-called *syllables*. Each syllable contains an *operation*. By using this model, the VLIW processor is capable of parallel processing, even though it can only process one instruction at a time. VEX operations are semantics-based and format-independent, so the same opcode can be used regardless of the type of operands and the results.

## 2.2.3.1 ISA

As explained in Section 2.2.2.2, the  $\rho$ -VEX processor implements the VEX ISA as introduced by Joseph Fisher. The term ISA is somewhat confusing in this sense, since it assumes a single instruction to correspond with a single operation. Since the  $\rho$ -VEX is a VLIW processor, this is not the case. As explained in the previous section, a single instruction can contain a collection of operations. To avoid confusion, the contents of the VEX ISA are referred to as operations rather than instructions. A complete overview of all operations enlisted in the VEX ISA are listed in Table 2.2 and Table 2.3. A discussion on the contents of this ISA can be found in Section 2.4.3, where the VEX ISA and the ISA of the GPU are compared.

## 2.2.3.2 Scheduling and execution

The scheduling of operations on a VLIW platform is relatively complex. The scheduler needs to order the instruction in such a way that the ILP is exploited optimally. To allow for this the scheduler should be able to issue multiple operations simultaneously and issue them out of order if necessary. When multiple operations are scheduled for simultaneous execution, they should be independent of each other. If they do depend on each other, the processor will experience race conditions during execution, which might cripple the working of the processor or corrupt the data that is being processed. If the scheduler can't schedule enough operations to fill the entire width of the  $\rho$ -VEX processor, a remaining slot is filled with a No Operation (NOP).

Because this way of scheduling is complex, it requires a relatively large amount of resources and time. Because of this, scheduling is handled by the host. Performing the scheduling on the FPGA would be a waste of precious resources. When the host machine handles the scheduling, the VLIW processor is able to make optimal use of the FPGA resources. On top of that, it makes sense to let the host machine handle scheduling, since it is being performed during compilation of the source code, which is also performed by the host CPU.

## 2.3 GPU analysis

The GPU is an indispensable component of a modern computer system. GPUs are designed especially to handle all forms of image processing, but have also proven to be extremely powerful hardware accelerators. The core assets of the GPU are its impressive parallel processing capabilities [1]. What also makes GPUs attractive is the fact that they are relatively cheap, easy to program and applicable in a broad application domain that stretches way beyond image processing. This section aims to explain how the GPU works, and what enables it to process massive amounts of data in parallel.

## 2.3.1 Parallelism

The GPU is a parallel processor, that exploits various sorts of parallelism. This section introduces the types of parallelism exploited by the GPU. There are several types of parallelism known in computing, and the GPU exploits nearly all of them. These include ILP, Data-level Parallelism (DLP) and Thread-level Parallelism (TLP). ILP is already introduced in Section 2.2.1. DLP is exploited by performing a single operation to multiple subsets of data. This increases the amount of data that is processed. Also, the scheduling and instruction hardware is not increased in size or complexity. TLP is exploited by performing different operations simultaneously in order to fully utilize the available resources.

## 2.3.2 GPU design

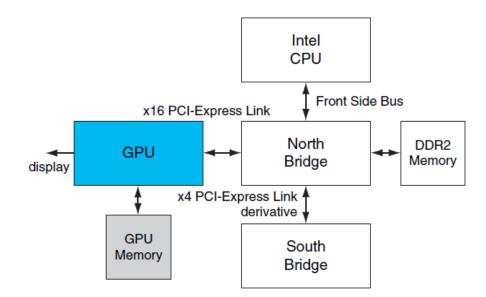

Unlike a VLIW processor, or any other type of CPU, a computation accelerators like the GPU is never used independently, but is always part of a larger computing system. Even though it is used as an extension of a host machine, the GPU is equipped with its own memory and processor. In most cases, the GPU is connected to the other main components of the computing system via a high speed bus, like PCIe. Figure 2.2 illustrates a common configuration of computer system featuring a GPU.

## 2.3.2.1 Processor architecture

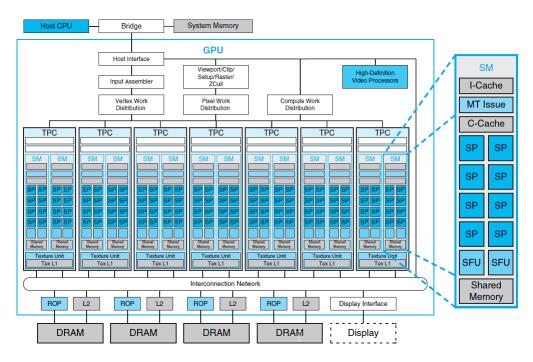

The parallel processor of the GPU is designed to process large quantities of data as fast as possible. To achieve this, GPUs handle data in a stream. This means that new data is transferred from and to the processor in a stream, whenever it's needed. This reduces the requirements for costly data storage on the chip itself. The processor needs to have a high data throughput to process the continuous stream of data. To achieve this the processor consists of a large amount of independent processing elements, called Streaming Processor (SP) cores, that work together to process the vast amounts of data that are fed

Figure 2.2: Computer system with an Intel CPU, adapted from [1]

to the processor. An SP core is a 32-bit floating point processor. These SP cores need to be structured efficiently so they can be targeted easily. A tree-like structure allows communication between the highest and lowest architectural layers in just a few steps, making it effective in exploiting parallelism. A structure like this can be implemented by introducing layers of abstraction to the architecture. A typical modern hierarchy entails several hundred SP cores, divided over a few dozen groups, known as Streaming Multiprocessor (SM) cores. If the leaves of the tree-like structure are represented by the SP core, the branches are represented by these SM cores. The SM cores are able to operate in an Single Instruction Multiple Data (SIMD)<sup>2</sup>-like mode. This mode, called Single Instruction Multiple Threads (SIMT) in GPUs, allows control over multiple SP cores by a single instruction source. This diminishes scheduling and operating overhead, and makes parallel execution less complex. Besides approximately eight SP cores, each SM core also contains two dedicated Special Function Unit (SFU) cores and two double precision units, that aid the SP cores with performing complex operations. To allow the SP cores to work the most effectively, each SM core is divided into two so-called SP lanes, each of which has control over half of the resources of the SM core. Sometimes two or four SM cores are entailed within a so-called Texture/Processor Cluster (TPC), which provides an additional layer in the hierarchy to further increase the parallel processing capabilities of the structure.

A graphical representation of a typical modern architecture is shown in Figure 2.3.

#### 2.3.2.2 Memory architecture

Thanks to its architecture, the parallel processor is able to process incredible amounts of data in parallel. However, in order to able to benefit from this processing power the

<sup>&</sup>lt;sup>2</sup>SIMD is a method for exploiting DLP, by applying a single instruction to multiple pieces of data.

Figure 2.3: Basic GPU architecture, adapted from [1]

processor needs to have a way to provide all of its cores with data to work on. This requires a hierarchical and parallel memory structure much like the processor hierarchy. To this end, the GPU memory architecture has a few important characteristics. First of all the memory banks used in the GPU are very wide, providing high data bandwidth. The memory is fast, thanks to aggressive signaling techniques that improve the transfer speed of the data. Also data compression techniques are used, to minimize the amount of data that has to be transfered. Finally structures like caches and scratch-pad memories are used to reduce the need for fetching data from outside the chip. Fundamentally, high throughput is in conflict with low latency, and thus the GPU has to deal with relatively long waiting times whenever off-chip data needs to be fetched. Luckily this does not have to be a problem. The massive parallelism of the GPU can hide this latency, by executing other tasks from other cores whenever some core is waiting for data.

**Memory types** The GPU uses several types of memory in the layered structure, each with its own properties and purposes.

The highest level is the *global memory*, which is shared by the entire GPU and can be accessed by all cores. It can even be accessed by the CPU of the computer system. It is meant for communications among the cores and for storage of larger amounts of data. It is implemented in off-chip DRAM. Transferring data from and to this DRAM is relatively the most time consuming on-chip memory operation for the GPU.

The level below the global memory is the *shared memory*, which is exclusive to an SM core. This shared memory is instantiated whenever it is needed and deleted when it is no longer needed. This dynamic behavior ensures that the shared memory does not need

to be large, allowing it to reside in the on-chip Static Random Access Memory (SRAM) cells. Fetching from this type of memory takes significantly less time, due to the location and the nature of the Random Access Memory (RAM) blocks in which it is implemented. It is mainly used for communication among the SP cores that are working on the same task.

The level below the shared memory is the *private memory*, which is specific to a single SP core. Each of these is a assigned a specific section of off-chip DRAM on the GPU. This memory is used for large portions of temporary data, such as private variables that are too large for the registers of the SP core. Since accessing the off-chip DRAM is very time consuming, modern GPU systems tend to cache portions of the private memory on-chip.

The lowest level are the *registers* of the SP core. These are located in the SP core itself. While the amount of data that can be stored in the registers is extremely small as compared to the other memory types, they are vital to the working of the SP core.

**Constant memory spaces** Besides the three aforementioned memory spaces there are two special read-only memory spaces. The first is called the *constant memory*. This memory is located in off-chip DRAM and can be filled at compile time to the liking of the programmer. Filling the constant memory with data that is needed during execution, ensures that the GPU will have less need to fetch data from the host machine's memory, thus improving the performance of the GPU. The second constant memory space is the *texture memory*, which holds large arrays of data and it also located in off-chip DRAM. This memory can be used in the same way as the constant memory, but it is optimized for spatial locality. This means that whenever data is placed in the texture memory efficiently (e.g. with unit stride), subsequent pieces of data can be transferred to the processor efficiently. Data from both the constant and the texture memory can be cached on-chip.

## 2.3.3 Instructions

The GPU has it's own dedicated ISA that is able to exploit the parallel capabilities of processor. This section will discuss the contents of one particular GPU ISA and the instruction scheduling procedure of the GPU.

#### 2.3.3.1 ISA

Like every other processor, the GPU features a certain set of instructions that it can executed. Commercial ISAs are often proprietary, because in disclosing these their respective owners might give away vital information that could distort market competition. For this reason, GPU manufacturers add an abstraction layer on top of their ISAs to hide their proprietary information, while allowing the programmer to interface with the GPU. NVIDIA, one of the largest GPU manufacturing companies calls the abstraction layer of their ISA Parallel Thread Execution (PTX). NVIDIA supplies thorough documentation of PTX, giving us a good impression of the GPUs ISA [23]. PTX is also covered in detail in a widely used computer architecture book by Patterson and Hennessy [1]. A detailed overview of the instructions included in the PTX ISA can be found in Section 2.4.3, where it is compared to the VEX ISA.

### 2.3.3.2 Scheduling and execution

With the processor and memory architecture fine-tuned for high speed parallel processing and the instructions available for doing so, the final challenge is in scheduling these instruction in the best way possible. The scheduler does not target individual cores, but targets the layers of the parallel processor. It uses multiple schedulers to do this. This section aims to explain why and how the GPU does this.

**Targeting the GPU** As mentioned in the beginning of Section 2.3, the GPU always functions as an accelerator and never in a stand-alone environment. To use the GPU, it must be targeted via a host machine. To make targeting the GPU easier, multiple programming frameworks have been introduced. Best known is Compute Unified Device Architecture (CUDA), which is introduced by GPU manufacturer NVIDIA itself [24]. Another widely used framework that can be used to target GPUs is Open Computing Language (OpenCL) [25]. Frameworks like these allow programmers to easily run workloads in parallel on a GPU. Obviously the programmer has to bear in mind how the instructions will be scheduled on the GPU and how data is addressed by the GPU while writing a parallel program, to gain optimal performance.

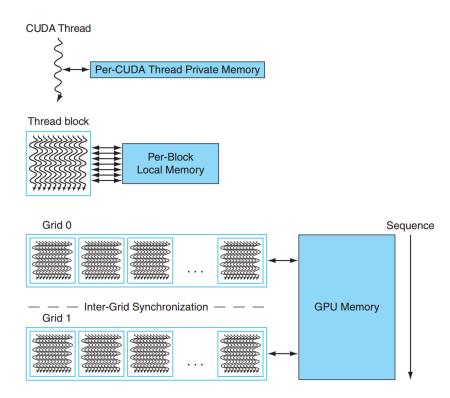

**Scheduling hierarchy** Scheduling of individual instructions to individual cores is not a feasible option for the GPU. The large amount of individual cores would make this option very time consuming. For this reason, instructions are scheduled in a hierarchy that maps precisely to the architecture of the parallel processor.

The highest layer in this hierarchy is the so-called *Grid*. This is a vectorizable loop that contains several smaller *Thread Blocks*, which form the second layer in this hierarchy. The main idea is that a Grid is mapped to a TPC or SM core and the Thread Block is mapped to an SP lane. The lowest level in the hierarchy is located inside the Thread Block and is called a *Thread*. A Thread is mapped to an SP core, and is simply a sequence of PTX instructions. Using a SIMT based approach, it is also possible to target multiple SP cores with a single instruction. This structure enables the parallel processor to easily issue a vast amount of instructions with minimal scheduling overhead.

Figure 2.4 shows the scheduling hierarchy along with the various types of memory that are accessible by each layer, as introduced in Section 2.3.2.2.

Drawbacks However, there are obviously some downsides to this way of scheduling.

For instance a Thread is not independent, since it is only able to perform the same task as every other Thread in the same Thread Block. It is for this reason that GPUs only perform well for data-level parallel problems. Since our target application entails these kind of problems, this is of no concern.

Also scalar execution cannot be done efficiently given this scheduling hierarchy. In a worse case scenario the GPU has to disable all but one SP cores in a lane to execute

Figure 2.4: Scheduling hierarchy in GPU system, with the accessible memory per layer [1]

instructions on scalar data. Even though this is a solution that causes enormous performance loss, it is the best way to handle this kind of problems. The only other solution would be to outsource such problems to the CPU of the host system, but the overhead of the data transfer makes this option even less attractive.

Obviously the best performance is achieved when all threads follow the same path. Whenever a branch occurs for some of the threads, the performance is decreased immediately. To cope with this, the processor has a special branch synchronization stack that manages threads that diverge and converge. Even so, branching is still the cause of a lot of performance decrease in all sorts of processors, both parallel and others.

## 2.4 Capability analysis

The design presented in this thesis will aim to combine the benefits of both the GPU design philosophy and the  $\rho$ -VEX VLIW processor in a single computation fabric, using the  $\rho$ -VEX as a starting point. To create an effective design the useless parts of the  $\rho$ -VEX will have to be identified and removed, and the useful parts and properties of the GPU will have to be ported to the FPGA based setting, and implemented in the computation fabric.

#### 2.4.1 Architecture

The structure of the GPU is created specifically for image processing applications much like our target application, while the  $\rho$ -VEX processor is created for more general purpose tasks. Thus it makes sense to adapt the architecture of the GPU. An architecture that consists of multiple individual processor cores, that are able to handle data in a stream. However, the number of processor cores that can be fit on an FPGA is significantly smaller than the number of cores available on a GPU. Where the GPU can contain over a thousand individual cores, the FPGA only has the capacity for about a hundred at maximum. This means that massive multithreading on a single FPGA is not a realistic option. However, other techniques to exploit parallelism can be implemented on FPGAs. Pipelining is one of these techniques. Several cores can be connected to each other, and form a processor pipeline. When each processor in this pipeline is dedicated to a task, multiple operations can be performed on data that is being processed by this pipeline. This increases the throughput of the processor, at the cost of latency.

#### 2.4.2 Memory architecture

The memory hierarchy of our fabric should be able to support the high throughput of the processor pipeline. This does not require many different memories in terms of size and speed, but it requires fast and well-placed memories width a high bandwidth. Caching techniques are not required, since data is never being reused in image processing tasks. Each pixels is only being handled once. Placing the memories efficiently and ensuring single-cycle access will minimize their impact on the critical path of the fabric. The critical path is defined as the longest possible path through the design. In order to be able to meet the timing requirements, the design must be able to traverse this path within a single clock cycle. The longer this path, the longer a clock cycle needs to take, causing a lower operating frequency of the overall design. By structuring the memory hierarchy in the same way as the processor pipeline, the data can be streamed through the processor pipeline. This memory architecture effectively removes the latencies related to fetching data from off-chip memories that would occur in a pipeline-less design. The latencies can be hidden entirely by implementing a technique like Direct Memory Access (DMA), that enables a system to interface with external memories without the interference of a processor. This can also be done in a streaming fashion, effectively making the fabric a low-latency streaming multiprocessor.

#### 2.4.3 Instruction Set Architecture

The operations and instructions from the VEX and PTX ISAs are listed in Table 2.2 and Table 2.3. The two ISAs are shortly examined and compared in terms of usefulness and applicability in our fabric. The instructions of both ISAs can be categorized in five groups.

**Arithmetic instruction** The VEX ISA has fewer traditional arithmetic instructions that the PTX ISA, but implements some exotic functions, like shift-and-add and sign operation.

**Multiplication instructions** While the PTX ISA provides a single instruction for multiplications, the VEX ISA has a rich set of dedicated operations for this. These are needed to be able to handle data that varies in terms of size and signedness, and are implemented to support Digital Signal Processing (DSP) tasks.

What also stands out is the *multiply-add* instruction in the PTX ISA, which combines a multiplication and an addition in a single instruction. In image processing, which is the core task of a GPU, a multiplication and an addition in sequence are quite common. When trying to gain maximal speed and performance, it is important to make the common case tasks fast. The multiply-add instructions aims to do just this.

The VEX ISA only supports division steps as an operation. This means that dividing larger numbers using the VEX ISA will require a lot of these operations, making it quite costly.

**Special functions instructions** This group only holds instructions of the PTX ISA, which are executed by the aforementioned SFU core of the GPU. Among these are functions like the sine, the cosine, the logarithm and the square root. Again, these functions are implemented to make the common case fast. The VEX ISA does not support any special functions.

**Logical functions instructions** This group contains all logical and binary operations, like AND, OR, XOR and bit-shift operations. The VEX ISA supports binary and conditional implementations of most of these operations, while the PTX ISA only supports conditional operations.

**Memory access instructions** This group lists all memory related instructions, like load and store. These instructions provide communication between the processor and memory. Again the PTX ISA implements just the needed basic operations, and the VEX ISA has multiple operations to support different data sizes and signedness.

**Control flow instructions** Among these are regular instructions like instruction calls and branches, and the PTX ISA also has an atomic instruction. This instruction makes sure that the parallel tasks can be synchronized. Thanks to instructions like these, parallel execution op GPUs can be kept uncluttered. The control flow instructions of the VEX ISA are again rather large in number and allow for flexibility in the execution of programs on the  $\rho$ -VEX system. Since atomic execution of operations embedded in an instruction is an intrinsic part of the VLIW design philosophy there is no dedicated atomic operation in the VEX ISA.

**Conclusion** There is a large overlap between the two, so they are theoretically both suitable. However, since the desired starting point is the  $\rho$ -VEX, it makes sense to start out with the VEX ISA. There are two major differences between the two ISAs. Firstly, the VEX ISA only supports signed and unsigned integers as data type, while PTX supports 8-, 16-, 32- and 64-bit signed and unsigned integers, untyped bits and floating point signals. This makes PTX intrinsically more powerful, but also more exhaustive

in terms of scheduling and resources. Secondly, the VEX ISA lacks support for special functions, like square root or sine operations. These are beneficial when hard mathematical workloads are executed. Also the multiply-add instruction from the PTX ISA might be beneficial when it comes to performing image processing algorithms.

| Instruction class | VEX Instruction | PTX Instruction | Instruction description                  |

|-------------------|-----------------|-----------------|------------------------------------------|

| Arithmetic        | ADD             | ADD             | Add                                      |

|                   | ADDCG           |                 | Add with carry and generate carry        |

|                   | SUB             | SUB             | Subtract                                 |

|                   |                 | REM             | Remainder                                |

|                   |                 | ABS             | Absolute value                           |

|                   |                 | NEG             | Negative value                           |

|                   | MIN             | MIN             | Minimum                                  |

|                   | MINU            |                 | Minimum unsigned                         |

|                   | MAX             | MAX             | Maximum                                  |

|                   | MAXU            |                 | Maximum unsigned                         |

|                   | SH1ADD          |                 | Shift left one and add                   |

|                   | SH2ADD          |                 | Shift left two and add                   |

|                   | SH3ADD          |                 | Shift left three and add                 |

|                   | SH4ADD          |                 | Shift left four and add                  |

|                   | SXTB            |                 | Sign extend byte                         |

|                   | SXTH            |                 | Sign extend half                         |

|                   | ZXTB            |                 | Zero extend byte                         |

|                   | ZXTH            |                 | Zero extend half                         |

|                   |                 | MOV             | Move                                     |

|                   |                 | CVT.DTYPE       | Type conversion                          |

| Multiplication    |                 | MUL             | Multiply                                 |

|                   | MPYLL           |                 | Multiply signed low 16 x low 16 bits     |

|                   | MPYLLU          |                 | Multiply unsigned low 16 x low 16 bits   |

|                   | MPYLH           |                 | Multiply signed low 16 x high 16 bits    |

|                   | MPYLHU          |                 | Multiply unsigned low 16 x high 16 bits  |

|                   | MPYHH           |                 | Multiply signed high 16 x high 16 bits   |

|                   | MPYHHU          |                 | Multiply unsigned high 16 x high 16 bits |

|                   | MPYL            |                 | Multiply signed low 16 x 32 bits         |

|                   | MPYLU           |                 | Multiply unsigned low 16 x 32 bits       |

|                   | MPYH            |                 | Multiply signed high 16 x 32 bits        |

|                   | MPYHU           |                 | Multiply unsigned high 16 x 32 bits      |

|                   | MPYHS           |                 | Multiply signed high 16 x 32 bits        |

|                   |                 |                 | and shift left 16 bits                   |

|                   |                 | MADD            | Multply and add                          |

|                   |                 | DIV             | Divide                                   |

|                   | DIVS            |                 | Divide step                              |

|                   |                 |                 |                                          |

| Special functions |                 | RCP             | Reciprocal                               |

|                   |                 | SQRT            | Square root                              |

|                   |                 | RSQRT           | Reciprocal square root                   |

|                   |                 | SIN             | Sine                                     |

|                   |                 | COS             | Cosine                                   |

|                   |                 | LG2             | Binary logarithm                         |

|                   |                 | EX2             | Binary exponentional                     |

Table 2.2: VEX and PTX overview - Part 1

| Instruction class                       | VEX Instruction | PTX Instruction  | Instruction description              |

|-----------------------------------------|-----------------|------------------|--------------------------------------|

| Logic                                   | AND             |                  | Bitwise AND                          |

|                                         | ANDC            |                  | Bitwise Complement and ADD           |

|                                         | OR              |                  | Bitwise OR                           |

|                                         | ORC             |                  | Bitwise Complement and OR            |

|                                         | XOR             |                  | Bitwise exclusive OR                 |

|                                         |                 | AND              | Conditional AND                      |

|                                         | ORL             | OR               | Conditional OR                       |