# Implementable Building Blocks for Fluctuation Based Calculation in Single Electron Tunneling Technology

Innocent Agbo, Saleh Safiruddin and Sorin Cotofana, Senior Member IEEE

Computer Engineering Laboratory

Delft University of Technology, Delft, The Netherlands

Abstract—Generally speaking, fluctuations and noise are unwanted factors interfering with the operation of devices and circuits, and their effect is becoming stronger as the fabrication technology feature size is decreasing. Recently, Single Electron Tunneling (SET) circuit implementations were proposed for two building blocks that were designed for Brownian motion circuits, i.e., circuits which instead of trying to suppress fluctuations (noise) are taking advantage of it. These are the so-called Hub and Conservative Join. The Hub provides its output to other building blocks by repeatedly offering its state at its output terminals, and taking it back when it cannot be delivered. Based on a random scheme of signaling, the Hub requires fluctuations to drive its operation. The other building block, the Conservative Join, is designed to work in cooperation with the Hub, though it does not require fluctuations. Those two building blocks constitute a universal set thus any logic function can be implemented only with such blocks. However, the proposed implementations require topologies and circuit parameters that are not realizable for the state of the art fabrication technology. This paper presents Single Electron Tunneling (SET) circuit implementations for the two building blocks which are taking into account realizability constraints. We propose novel SET circuit topologies for both blocks that satisfy topology and circuit parameters constraints and analyze their behavior at a temperature of 1K by computer simulations with SIMON 2.0. We demonstrate that the two different modes of operation in the blocks, fluctuation vs. nonfluctuating, can be accommodated by appropriately tuning circuit parameters. Utilizing these proposed topologies we then present an example of a half adder circuit constructed using the two building blocks and demonstrate that it functions correctly by means of simulations.

### I. INTRODUCTION

The expectation that current semiconductor technologies (CMOS) cannot be pushed beyond certain limits has motivated intensive research into a wide variety of alternatives. Single Electron Tunneling (SET) technology has attracted interest in this context due to its potential for extremely low power consumption. Based on the tunneling of electrons through junctions, SET differs fundamentally from CMOS, thus it is opening up avenues for novel computational paradigms.

In the last few years there has been considerable interest in researching methods to effectively utilize the basic SET properties. Such efforts include [1], [2], [3], [4], [5], which are essentially based on Single Electron Encoded Logic and Electron Counting concepts. Theoretical results on the area and delay complexity of arithmetic operations using those new paradigms indicate great potential. However, one of the

most important challenges for implementing circuits based on quantum tunneling thus far has been the stochastic nature of the tunneling process. Tunneling through a junction becomes possible when the junction's actual voltage  $V_i$  exceeds the junction's critical voltage  $V_c = \frac{q_e}{2(C_i + C_e)}$ , where  $q_e = 1.602 \cdot 10^{-19} C$ , the capacitance of the junction is  $\overline{C}_i$ , and the capacitance of the remainder of the circuit as seen from the junction is  $C_e$ . The delay of such circuits cannot be analyzed in the traditional sense. Instead, for each transported electron one can describe the switching delay as  $t_d = \frac{-\log P_{\rm Error} R_t}{|V_j| - V_c}$ , where  $R_t$  is the junction resistance and  $P_{\text{Error}}$  is the probability that the desired charge transport has not occurred after  $t_d$  seconds. This probabilistic delay precludes the direct utilization of SET-based computation in building synchronously timed arithmetic units and since the exact tunnel time of an electron is not known, extensive error correcting schemes are required and switching times have to be lengthy. This has motivated research for SET architectures and circuits based on delay-insensitive computations so that the problems arising from unknown delays can be eliminated altogether [6].

Another proposal has attempted to turn one of the weak points of SET technology, the sensitivity to noise and fluctuations into an asset, by employing it actively in a simulated annealing scheme in Boltzman machines [7]. SET technology is especially suited for implementing the token-based nature of this architecture, with tokens representing electrons or vacancies of electrons. Being focused on implementations of neural networks, however, this effort has found no follow-up in the context of traditional arithmetic circuits.

In [8] the potential use of fluctuations in the operation of arithmetic circuits implemented by SET technology was investigated. Two building blocks for SET circuits were presented that were designed with fluctuations in mind: the *Hub* and the *Conservative Join*.

These building blocks were proposed in the context of the so-called Brownian circuits [9], [10]. They have been shown to form a computationally universal set from which any desired functionality can be constructed.

Though the designs function as required in simulations, circuits based on these designs are not industrially implementable. This is due to the *Conservative Join* circuit pa-

rameters and wire routing not meeting the manufacturing constraints. The *Hub* design on the other hand, does meet the constraints.

In this paper we first discuss the problems associated with the previous work on the *Conservative Join*. We then propose a new *Conservative Join* design with circuit parameters and circuit element placements that do meet the industrial requirements for manufacturing. The newly proposed design functions identical to the previous design, and can coexist with the *Hub* at the same temperature. The behavior of the new design is verified by means of computer simulations at a temperature of 1K with SIMON 2.0 [11]. Furthermore we present a half adder circuit constructed using the two building blocks and demonstrate that it functions correctly by means of simulations.

### II. BROWNIAN BUILDING BLOCKS

The two building blocks used in this paper have been proposed in the context of so-called *Brownian circuits* [10], [9]. The idea of Brownian circuits is to use fluctuations to guide signals through a circuit. That is, fluctuations drive a search process through a Brownian maze formed by the topology of the circuit [9].

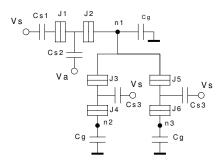

The first building block is the *Hub*, which contains three wires that are bidirectional (Fig. 1 [8]). In principle there is at most one signal at a time on any of the Hub's wires, and this signal can move to any of the wires due to its fluctuations.

The second building block is the *Conservative Join (CJoin)*, which has two input wires and two output wires. The CJoin can be interpreted as a synchronizer of two signals passing through it. Signals may fluctuate on the input wires of a CJoin, but once processed by the CJoin, they re placed on the output wires and there is no way back, even though fluctuations on the output wires are still allowed. Note that when connecting CJoins to each other, one should make sure that input terminals face output terminals. Hubs, having bi-directional wires, may be connected in any way to CJoins or other Hubs.

Fig. 1. Hub circuit implemenation

### III. CJoin Building Block Limitations

The *Conservative Join* implementation of [8] has some characteristics which limit its practical realization though its functionality is as required. First, its unrealistic nature is based on the long diagonal wires that appear literally on the design,

hence resulting in a routing problem during implementation. Second, it falls short of the industrial standard of the parameters of the tunnel junction capacitances. It has tunnel junction capacitance of 0.01aF for C2, C4, C6, C8, C10, C12, and C13 and this value is too small to be industrially realized utilizing current manufacturing methods.

### IV. REDESIGNED CONSERVATIVE JOIN BUILDING BLOCKS

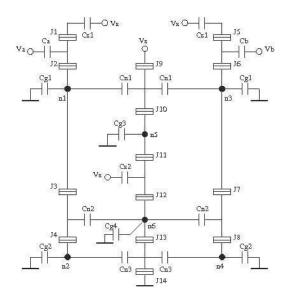

Fig. 2. Redesign Conservative Join circuit implemenation

In view of the previously mentioned aspects a new topology is proposed for the *Conservative Join*, depicted in Figure 2. In the figure one can observe that the diagonal wires running in the previous design of the *Conservative Join* have been eliminated.

As it was the case in the original design, signals may fluctuate on the input wires of a ReDesCJoin, but once processed by the ReDesCJoin, they are placed on the output wires and there is no way back, even though fluctuations on the output wires are still allowed. When connecting ReDesCJoins to each other, it should be ensured that input terminals face output terminals.

# V. IMPLEMENTATIONS

To calculate circuit parameters for each proposed circuit topology, which would lead to the desired functionality, we start with the general conditions which have to be met to enable single electron manipulations. There are two major effects which have to be considered, namely quantum fluctuations and thermal energy. If either of those two effects is dominant then the electrons are not localized on islands and the desired functionality cannot be achieved.

Since electron tunneling is a quantum mechanical process, an electron's wave function extends through potential barriers, and the electron is spread over the islands in a SET circuit. If this effect is to prevail there would be no localized charges and computations using electrons would not be possible. To ensure that the charge of an electron is quantized on each specific island the tunnel junctions must have a sufficiently high tunneling resistance, so that the charging energy, also called the Coulomb energy, dominates over the quantum charge fluctuations. This can be expressed as:

$$\frac{q_e^2}{2 \cdot C_j} \cdot R_j \cdot C_j >> h => R_j >> h/q_e^2 = 25.8k\Omega$$

, where h is Planck's constant,  $C_j$  is the tunnel capacitance, and  $R_j$  is the tunneling resistance. Therefore, the resistance of all the tunneling junctions in the following implementations is chosen as  $100 \mathrm{k}\Omega$ , which has also been used in previous studies [1], [2], [3], [4], [5].

The second effect that has to be considered is that of thermal energy. If the thermal energy dominates over the charging energy,  $E_c$ , the quantization effects become again non-observable. The condition is then  $E_c = \frac{q_e^2}{2 \cdot C} > k_B \cdot T$ , where  $k_B$  is Boltzmann's constant and T is the absolute temperature. The capacitance of an island should therefore not exceed 926aF for a temperature of 1K.

The temperature of 1K was chosen to demonstrate the coexistence of fluctations of quantized electron charges and deterministic behaviour in a circuit. As it was previously mentioned, the thermal energy should not dominate the circuit elements, however, to achieve the desired Hub functionality, there should be enough thermal energy flucutations to enable electrons to tunnel from one island to another. This was achieved by bringing the voltages over certain tunneling junctions close enough to their critical voltages such that an increase in the energy of an electron at the junction due to the extra thermal energy would, at random moments, cause the electron to tunnel forward, and when the thermal energy decreases to tunnel back again. The thermal energy is thus effectively used as a random control voltage. However the CJoin has to have a deterministic response thus it has to be designed in such a way that the thermal energy has little or no effect on its behavior. The design of the CJoin is based on the buffering techniques introduced in [2].

In the following, all tunneling junctions have a resistance of 0.1MOhms. When a tunnel junction appears in the figure it is designated with a "J" and a number, and when the circuit parameters are described the capacitance of the tunnel junction is referred to with a "C" and the same number. The source voltage Vs is set at 16 mV. All simulations were done using SIMON 2.0 software [11].

The CJoin circuit operates as follows. When inputs Va and Vb go high, an electron tunnel through the junctions J1-J2 and J5-J6 leaving positve charges on nodes n1 and n3, respectively. When n1 and n3 simultaneously have a charge that is +ve charge this case, an electron tunnels from n5 into the source through junction J9 and J10. Subsequently, an electron tunnels from n6 to n5 due to the SET transistor J11-J12, which acts as a buffer and separates the influences of the input Cn1 gate capacitors and Cn2 driving gate capacitors. At this point, the charge on node n6, +ve charge causes the charge on node 1, n1, positive charge to be transferred into node 2, n2 through

J3 and J4, and the charge on node 3, n3, positive charge to be transferred into node 4, n4 through J7 and J8. Nodes n2 and n4 are the output nodes, n2 and n4 simultaneously. To restore the circuit back to a reusable state, the charge remaining on node 6, n6 has to be removed. This is realized by connecting node 6, n6 to ground through a reversed transistor structure, J14-J13. However, this is done if there is a positive charge residing on node 6, n6 and the output charges on nodes n2 and n4 are set to one (1), then an electron tunnels from the ground into node 6, n6, resetting the circuit. Hence, the circuit is ready to accept new input tokens when the output charges have been consumed. Figure 2 presents a SET circuit topology that implements the Redesigned Conservative Join. The circuit was simulated at 1 Kelvin. The new circuit parameters are as follows: Cs1 = Cg1 = C1 = C3 = C5 = C7 = C11 = 10aF; Cs2 = 0.5aF; Ca = Cb = 1aF; Cn1 = Cn3 = Cn2 = 0.3aF; Cg2= Cg3 = 10.5aF; Cg4 = 11aF; C9 = C14 = 5aF; C2 = C4 =C6 = C8 = C10 = C12 = C13 = 0.1aF.

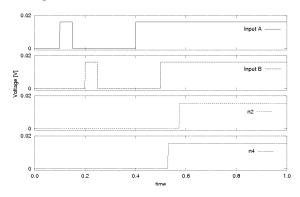

The results of the simulation are presented in Figure 3. When only Va or Vb goes high no charge appears on the output nodes. When both Va and Vb go high charges appear on the output nodes n2 and n4.

Fig. 3. Redesigned Conservative Join circuit simulation results

# VI. NETWORKS OF FLUCTUATION BASED CIRCUITS

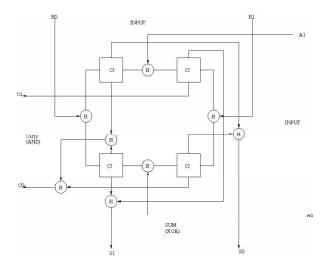

To demonstrate that these new building blocks can be combined into one functional circuit we use as an example the Brownian based implementation of a Half-Adder, the most fundamental basic building block in computer arithmetic. The construction of the Half-Adder using Hubs and CJoins is depicted in Fig. 5. Four CJoin elements and eight Hub elements are required and the Half-Adder circuit is constructed using 88 tunneling junctions and 84 capacitances.

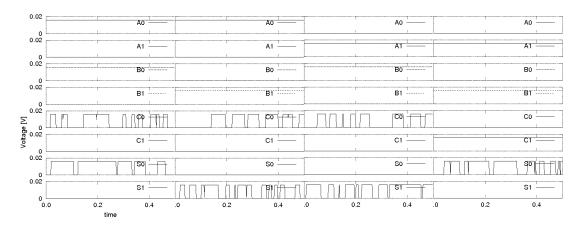

To verify the presented design we applied various input patterns to the circuit and evaluated its response by means of SIMON simulations. The results of the input combinations are depicted in Fig. 4. Due to the tokens generated at the outputs not being consumed, each input combination was simulated separately and the circuit was reset between each new simulation. The results are placed side by side for illustrative purposes.

The output behaves as expected, for example one can observe that can the carry output, C, is '1'  $[C_0 = 0, C_1 = 1]$ as

Fig. 4. Half Adder simulation results

it should. The sum output, S, should be '0'  $[S_0 = 1, S_1 = 0]$ . In the simulation the output for  $S_1 = 0$ . However,  $S_0$  is fluctuating around '1' instead of being a clear '1'. This is due to the fact that the output is provided by a Hub, which by its very nature provides fluctuating signals. We note here that to make the implementation usable in a larger circuit token 'traps' have to be added to the fluctuating outputs. This 'trap' would await any charges arriving on a node and ensure that the charges travel to the output and do not return. These augmentations would act in effect as buffers and they may or may not be required depending on the nature of the circuit utilizing the half adder output.

Fig. 5. Half Adder circuit using Brownian Building Blocks

# VII. CONCLUSION

In this paper we have presented a re-design of a previously proposed SET implementation of a *Conservative Join* such that

any circuits using this design and the *Hub* as two fluctuation based building blocks can be industrially realized in a physical structure. By considering a half adder implementation as a discussion vehicle we demonstrated that this new design can coexist with the *Hub* at the same temperature while maintaining it's desired behavior.

#### REFERENCES

- S. Cotofana, C. Lageweg, and S. Vassiliadis, "Addition Related Arithmetic Operations via Controlled Transport of Charge," *IEEE Transactions of Computers*, vol. 54, no. 3, pp. 243–256, March 2005.

- [2] C. Lageweg, S. Cotofana, and S. Vassiliadis, "Static Buffered set Based Logic Gates," in *Proceedings of the 2nd IEEE International Conference* on Nanotechnology (IEEE Nano), Arlington, USA, 2002, pp. 491–494.

- [3] —, "A Linear Threshold Gate Implementation in Single Electron Technology," in *Proceedings of the IEEE Computer Society Workshop on VLSI*, Orlando, USA, 2001, pp. 93–98.

- [4] N. Asahi, M. Akazawa, and Y. Amemiya, "Single-Electron Logic Systems Based on the Binary Decision Diagram," *IEICE Transactions on Electronics*, vol. E81-C, no. 1, pp. 49–56, January 1998.

[5] C. Meenderinck and S. Cotofana, "Computing Division Using Single-

- [5] C. Meenderinck and S. Cotofana, "Computing Division Using Single-Electron Tunneling Technology," *IEEE TRANSACTIONS ON NAN-*OTECHNOLOGY, vol. 6, no. 4, pp. 451–457, July 2007.

- [6] S. Safiruddin and S. Cotofana, "Building Blocks for Delay-Insensitive Circuits using Single Electron Tunneling Devices," in *Proceeding of 7th IEEE International Conference on Nanotechnology (IEEE Nano)*, 2007, pp. 704–708.

- [7] T. Yamada, M. Akazawa, T. Asai, and Y. Amemiya, "Boltzmann Machine Neural Network Devices using Single-Electron Tunneling," *Nanotechnology*, vol. 12, no. 1, pp. 60–67, 2001.

- [8] S. Safiruddin, S. D. Cotofana, F. Peper, and J. Lee, "Building blocks for fluctuation based calculation in single electron tunneling technology," in Procedeengs of the 8th IEEE Conference on Nanothechnology, August 2008.

- [9] F. Peper and et. al., "Brownian Circuits Part I: Concept and Basic Designs," *In preparation*, 2008.

- [10] J. Lee and et. al., "Brownian Circuits Part II: Efficient Designs and Brownian Cellular Automata," In preparation, 2008.

- [11] C. Wasshuber, H. Kosina, and S. Selberherr, "SIMON A Simulator for Single-Electron Tunnel Devices and Circuits," *IEEE Transactions on Computer-Aided Design*, vol. 16, no. 9, pp. 937–944, September 1997.