# Efficient Execution of Video Applications

on Heterogeneous Multi- and Many-Core Processors

# Efficient Execution of Video Applications

on Heterogeneous Multi- and Many-Core Processors

#### **PROEFSCHRIFT**

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus Prof.ir. K.C.A.M Luyben, voorzitter van het College voor Promoties, in het openbaar te verdedigen op maandag 6 juni 2011 om 15:00 uur door

> Arnaldo PEREIRA DE AZEVEDO FILHO Master in Computer Science Universidade Federal do Rio Grande do Sul geboren te Natal, Rio Grande do Norte, Brazil.

Dit proefschrift is goedgekeurd door de promotor:

Prof.dr. B.H.H. Juurlink

Copromotor:

Dr. K.L.M. Bertels

#### Samenstelling promotiecommissie:

Rector Magnificus, voorzitter

Prof.dr. B.H.H. Juurlink, Technische Universität Berlin, promotor Dr. K.L.M. Bertels, Technische Universiteit Delft, copromotor

Prof.dr. J. van Leeuwen, U-Utrecht

Prof.dr. L.A. Sousa, U. Tecnica de Lisboa

Prof.dr. H.A.G. Wijshoff, U-Leiden

Prof.dr.ir. H.J. Sips, Technische Universiteit Delft Prof.dr.ir. R.L. Langendijk, Technische Universiteit Delft

Prof.dr. C. Witteveen, Technische Universiteit Delft, reservelid

ISBN: 978-90-72298-17-1

Copyright © 2011 A. Pereira de Azevedo Filho

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without permission of the author.

Printed in the Netherlands

# Efficient Execution of Video Applications

on Heterogeneous Multi- and Many-Core Processors

## **Abstract**

In this dissertation we present methodologies and evaluations aiming at increasing the efficiency of video coding applications for heterogeneous many-core processors composed of SIMD-only, scratchpad memory based cores. Our contributions are spread in three different fronts: thread-level parallelism strategies for many-cores, identification of bottlenecks for SIMD-only cores, and software cache for scratchpad memory based cores.

First, we present the 3D-Wave parallelization strategy for video decoding that scales for many-core processors. It is based on the observation that dependencies between frames are related with the motion compensation kernel and motion vectors are usually within a small range. The 3D-Wave strategy combines macroblock-level parallelism with frame- and slice-level parallelism by overlapping the decoding of frames while dynamically managing macroblock dependencies. The 3D-Wave was implemented and evaluated in a simulated many-core embedded processor consisting of 64 cores. Policies for reducing memory footprint and latency are presented. The effects of memory latency, cache size, and synchronization latency are studied.

The assessment of SIMD-only cores for the increasing complexity of current multimedia kernels is our second contribution. We evaluate the suitability of SIMD-only cores for the increasing divergent branching in video processing algorithms. The H.264 Deblocking Filter is used as test case. Also, the overhead imposed by the lack of a scalar processing unit for SIMD-only cores is measured using two methodologies. Low area overhead solutions are proposed to add scalar support to SIMD-only cores.

Finally, we focus on the memory hierarchy and we propose a new soft-ware cache organization to increase the efficiency and efficacy of scratchpad memories for unpredictable and indirect memory accesses. The proposed Multidimensional Software Cache reduces software cache overhead by allowing the programmer to exploit known access behavior in order to reduce the number of accesses to the software cache and by grouping memory requests. An instruction to accelerate MDSC lookup is also presented and analyzed.

# Acknowledgments

This thesis is a result of an effort performed with several direct and indirect collaborators that I would like to thank. First, I thank God for the gift of life and for constantly being watching over me. I want to thank my family: my father for this example and my mother for her support and understanding; my wife, Ozana, for her love and for being at my side in this process; and my son, Alex, that knows, like no one else, how to bring a smile to my face. I also thank my extended "family", my friends, which from far away or close by always had time to share with me the ups and downs.

I would like to thank my supervisor, Ben Juurlink, for his guidance and patience throughout the PhD. process. I also would like to thank my former master and undergrad advisors Sergio Bampi and Ivan Saraiva, which paved my initial scientific career. I thank also Cor Meenderinck, Mauricio Alvarez, Alex Ramirez, Andrei Terechko, Jan Hoogerbrugge, Zdravko Popovic and Roberto Giorgi for their collaboration on the development of this work.

I thank also the support staff of our faculty, Lidwina Tromp, Monique Tromp, Eef Hartman, and Erik de Vries, for their effort to keeps things working properly so we can concentrate on our work.

During the years in the group, some people arrived and others left and many of them I can consider friends, not just colleagues. I will not name them to avoid injustices, but I thank each of you for the time we spent together. I also thank my other colleagues that, for a reason or another, did not share more time together, but also offered great input with their presence.

For all of you, please keep in mind that my gratitude is not directly proportional with the length of this acknowledgments.

A. Pereira de Azevedo Filho

Delft, The Netherlands, 2011

# Contents

| A  | bstrac  | et            |             |                              | i    |

|----|---------|---------------|-------------|------------------------------|------|

| A  | cknov   | vledgme       | ents        |                              | iii  |

| Li | st of l | Figures       |             |                              | xiv  |

| Li | st of ' | <b>Tables</b> |             |                              | XV   |

| Al | bbrev   | iations       |             |                              | xvii |

| 1  | Intr    | oductio       | n           |                              | 1    |

|    | 1.1     | SARC          | Architect   | ure                          | 3    |

|    | 1.2     | Object        | tives       |                              | 5    |

|    | 1.3     | Organ         | ization and | d Contributions              | 6    |

| 2  | A So    | calable       | Parallel A  | Algorithm for H.264 Decoding | 11   |

|    | 2.1     | Introd        | uction      |                              | 12   |

|    | 2.2     | Overv         | iew of the  | H.264 standard               | 13   |

|    | 2.3     | Paralle       | elizing H.2 | 264                          | 17   |

|    |         | 2.3.1         | Task-Le     | vel Decomposition            | 18   |

|    |         | 2.3.2         | Data-Le     | vel Decomposition            | 18   |

|    |         |               | 2.3.2.1     | GOP-Level Parallelism        | 18   |

|    |         |               | 2.3.2.2     | Frame-Level Parallelism      | 19   |

|    |         |               | 2.3.2.3     | Slice-Level Parallelism      | 20   |

|    |         |               | 2.3.2.4     | Macroblock-Level Parallelism | 21   |

|   |      |                   | 2.3.2.5 Block-Level Parallelism               | 23         |

|---|------|-------------------|-----------------------------------------------|------------|

|   | 2.4  | 3D-Wa             | ave Strategy                                  | 23         |

|   |      | 2.4.1             | Parallelization Strategy                      | 24         |

|   |      | 2.4.2             | 3D-Wave Static Evaluation                     | 24         |

|   |      |                   | 2.4.2.1 Maximum Parallelism 2                 | 28         |

|   | 2.5  | Limite            | ed Resources                                  | 30         |

|   | 2.6  | Dynan             | nic 3D-Wave                                   | 33         |

|   | 2.7  | Conclu            | usions                                        | 35         |

| 3 | 3D-  | Wave Ir           | mplementation 3                               | 37         |

|   | 3.1  |                   |                                               | 38         |

|   | 3.2  |                   |                                               | 39         |

|   | 3.3  |                   | C7                                            | 10         |

|   |      | 3.3.1             |                                               | <b>‡</b> 1 |

|   |      | 3.3.2             | •                                             | 13         |

|   |      | 3.3.3             | -                                             | 16         |

|   |      | 3.3.4             |                                               | 16         |

|   |      | 3.3.5             |                                               | <b>1</b> 7 |

|   | 3.4  | Experi            | imental Results                               | 18         |

|   |      | 3.4.1             | Scalability                                   | 18         |

|   |      | 3.4.2             | Frame Scheduling and Priority                 | 51         |

|   |      | 3.4.3             | Bandwidth Requirements                        | 53         |

|   |      | 3.4.4             |                                               | 57         |

|   |      | 3.4.5             | Impact of the L1 Cache Size                   | 57         |

|   |      | 3.4.6             | Impact of the Parallelization Overhead 5      | 59         |

|   |      | 3.4.7             | CABAC Accelerator Requirements 6              | 52         |

|   | 3.5  | Conclu            | usions                                        | 53         |

| 4 | Suit | ahility           | of SIMD-Only Cores for Kernels with Divergent |            |

| • |      | ability<br>nching |                                               | 67         |

|   | 4.1  | Introdu           | uction                                        | 68         |

|   | 4.2  | Related           | d Work .  |                                          | 69 |

|---|------|-------------------|-----------|------------------------------------------|----|

|   | 4.3  | Cell Pı           | ocessor A | rchitecture                              | 70 |

|   | 4.4  | Deblocking Filter |           |                                          | 73 |

|   | 4.5  | Implen            | nentation |                                          | 76 |

|   | 4.6  | Experi            | mental Re | sults                                    | 78 |

|   | 4.7  | Conclu            | isions    |                                          | 81 |

| 5 | Scal | ar Proc           | essing on | SIMD-Only Architectures                  | 83 |

|   | 5.1  | Introdu           | iction    |                                          | 83 |

|   | 5.2  | Experi            | mental Me | ethodologies                             | 84 |

|   |      | 5.2.1             | Large-Da  | nta-Type Methodology                     | 85 |

|   |      | 5.2.2             | SPE-vs-F  | PPE                                      | 86 |

|   | 5.3  | Kernel            | s         |                                          | 88 |

|   |      | 5.3.1             | Small Ke  | ernels                                   | 88 |

|   |      |                   | 5.3.1.1   | Kernels that Access Unaligned Data       | 89 |

|   |      |                   | S         | ахру                                     | 89 |

|   |      |                   | F         | IR                                       | 89 |

|   |      |                   | 5.3.1.2   | Kernels that Process Scattered Data      | 90 |

|   |      |                   | Q         | QuickSort                                | 90 |

|   |      |                   | N         | Merge Sort                               | 90 |

|   |      |                   | 5.3.1.3   | Kernels that Require Indirect Addressing | 91 |

|   |      |                   | Ir        | mage Histogram                           | 91 |

|   |      |                   | G         | Gray-Level Co-occurrence Matrices        | 92 |

|   |      | 5.3.2             | Large Ke  | ernels                                   | 92 |

|   |      |                   | 5.3.2.1   | Deblocking Filter                        | 93 |

|   |      |                   | 5.3.2.2   | Viterbi Decoder                          | 93 |

|   | 5.4  | Experi            | mental Re | sults                                    | 94 |

|   |      | 5.4.1             | Large-Da  | ata-Type                                 | 94 |

|   |      | 5.4.2             | SPE-vs-F  | PPE                                      | 96 |

|   |      |                   | 5.4.2.1   | Deblocking Filter                        | 96 |

|   |      |                   | 5422      | Viterbi Decoder                          | 97 |

|   | 5.5 | Instruc | ctions for Scalar Processing on SIMD-only Cores | 98  |

|---|-----|---------|-------------------------------------------------|-----|

|   | 5.6 | Conclu  | usions                                          | 98  |

| 6 | The | Multid  | imensional Software Cache                       | 101 |

|   | 6.1 | Introd  | uction                                          | 102 |

|   | 6.2 | Relate  | d Work                                          | 103 |

|   | 6.3 | Cell D  | MA Latency                                      | 104 |

|   | 6.4 | Multic  | limensional Software Cache                      | 106 |

|   | 6.5 | Studie  | d Kernels and MDSC Enhancements                 | 113 |

|   |     | 6.5.1   | GLCM Kernel                                     | 113 |

|   |     | 6.5.2   | H.264 Motion Compensation                       | 115 |

|   |     | 6.5.3   | Data Locality in MC                             | 117 |

|   |     | 6.5.4   | The MC Enhancements                             | 119 |

|   |     |         | 6.5.4.1 Extended_Line                           | 120 |

|   |     |         | 6.5.4.2 Extended_XY                             | 120 |

|   |     |         | 6.5.4.3 SIMD                                    | 121 |

|   |     |         | 6.5.4.4 Static                                  | 122 |

|   | 6.6 | Experi  | imental Methodology                             | 122 |

|   | 6.7 | Experi  | imental Results                                 | 123 |

|   |     | 6.7.1   | GLCM Results                                    | 123 |

|   |     | 6.7.2   | MC Results                                      | 125 |

|   | 6.8 | Conclu  | usions                                          | 130 |

| 7 | Har | dware S | Support for Software Caches                     | 133 |

|   | 7.1 | Introd  | uction                                          | 133 |

|   | 7.2 | The Lo  | ookUp_SC Instruction                            | 134 |

|   |     | 7.2.1   | Dedicated Register File                         | 136 |

|   |     | 7.2.2   | General Purpose Register File                   | 137 |

|   |     | 7.2.3   | Local Store                                     | 137 |

|   | 7.3 | Experi  | imental Methodology                             | 140 |

|   | 7 4 | Experi  | mental Results                                  | 142 |

|     |         | 7.4.1 GLCM Results                | .43        |

|-----|---------|-----------------------------------|------------|

|     |         | 7.4.2 MC Results                  | .44        |

|     | 7.5     | Conclusions                       | .46        |

| 8   | Con     | lusions 1                         | <b>47</b>  |

|     | 8.1     | Summary and Contributions         | .47        |

|     | 8.2     | Open Issues and Future Directions | .50        |

| Bil | bliogr  | aphy 1                            | 153        |

| Lis | st of I | ublications 1                     | 165        |

| Sa  | menv    | atting 1                          | 169        |

| Cu  | ırricu  | um Vitae 1                        | <b>171</b> |

# List of Figures

| 1.1  | Block diagram of a generic SARC instance                                                                            | 4  |

|------|---------------------------------------------------------------------------------------------------------------------|----|

| 2.1  | Block diagram of the decoding process                                                                               | 14 |

| 2.2  | Block diagram of the encoding process                                                                               | 14 |

| 2.3  | H.264 data structure                                                                                                | 16 |

| 2.4  | A typical slice/frame sequence and its dependencies                                                                 | 16 |

| 2.5  | 2D-Wave approach for exploiting MB parallelism. The arrows indicate dependencies                                    | 21 |

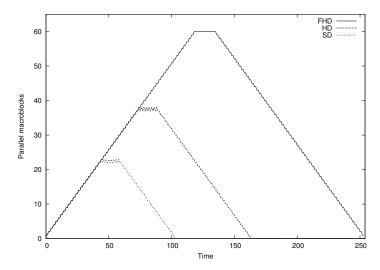

| 2.6  | MB parallelism for a single SD, HD, and FHD frame using the 2D-Wave approach                                        | 22 |

| 2.7  | 3D-Wave strategy: Frames can be decoded partially in parallel because inter-frame dependencies have a limited range | 25 |

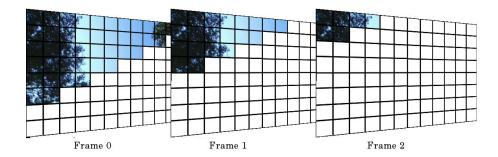

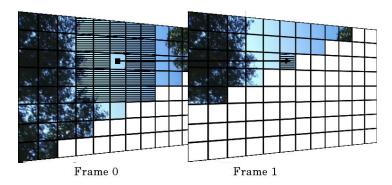

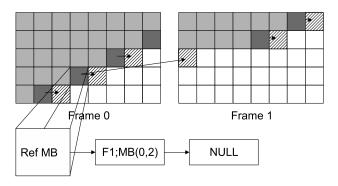

| 2.8  | Reference range example: The hashed area in Frame 0 is the reference range of the hashed MB in Frame 1              | 25 |

| 2.9  | Stacking of frames of a FHD sequence with a 128 pixels maximum MV length                                            | 27 |

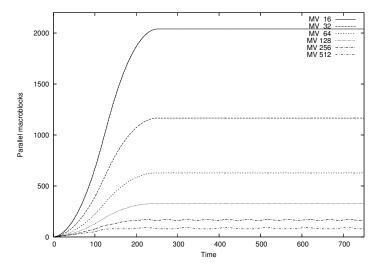

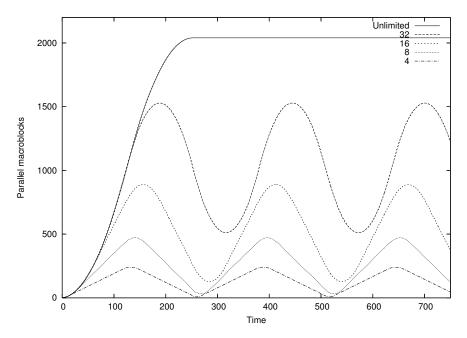

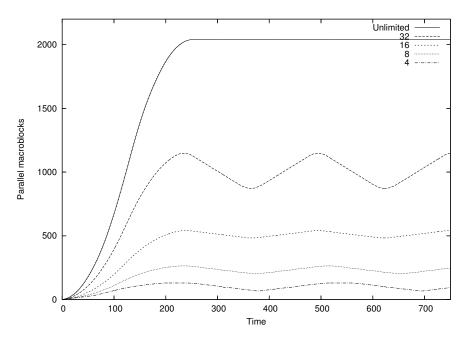

| 2.10 | Number of parallel MBs in the 3D-Wave for FHD frames with different MV ranges                                       | 29 |

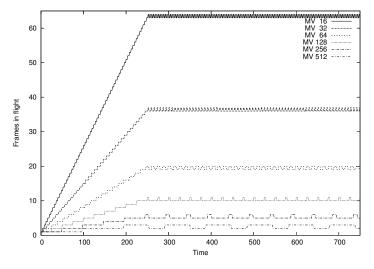

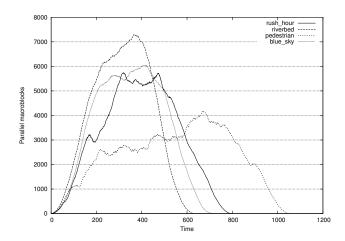

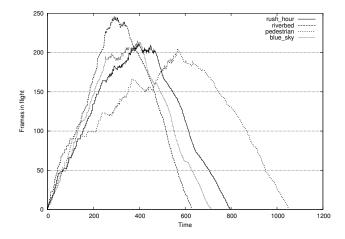

| 2.11 | Frames in flight for FHD frames with different MV ranges                                                            | 29 |

| 2.12 | Macroblock parallelism with limited frames in flight                                                                | 31 |

| 2.13 | Scheduled macroblock parallelism with limited frames in flight.                                                     | 32 |

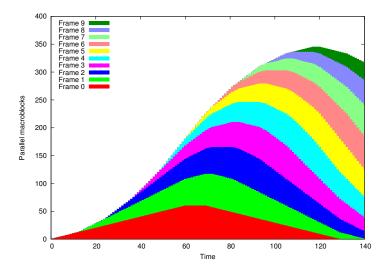

| 2.14 | Dynamic 3D-Wave: number of parallel MBs                                                                             | 34 |

| 2.15 | Dynamic 3D-Wave: number of frames in flight                                                                         | 35 |

| 3.1  | Pseudo-code for deblocking a frame and a MB                                                                         | 42 |

| 3.2  | Tail submit.                                                                                                                                                                                                                                                                                                                                         | 43 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.3  | Pseudo-code for the decode_mb function of the 3D-Wave                                                                                                                                                                                                                                                                                                | 44 |

| 3.4  | Illustration of the 3D-Wave and the subscription mechanism. $$ .                                                                                                                                                                                                                                                                                     | 46 |

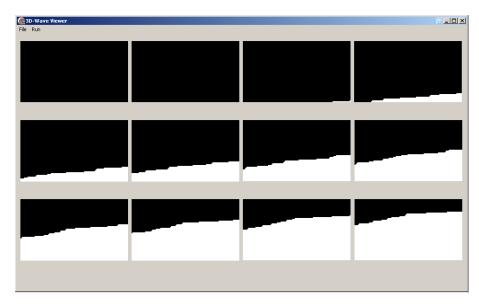

| 3.5  | Screenshot of the 3D-Wave Viewer                                                                                                                                                                                                                                                                                                                     | 48 |

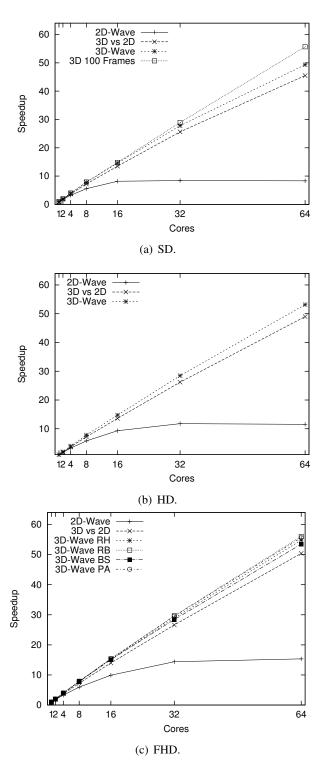

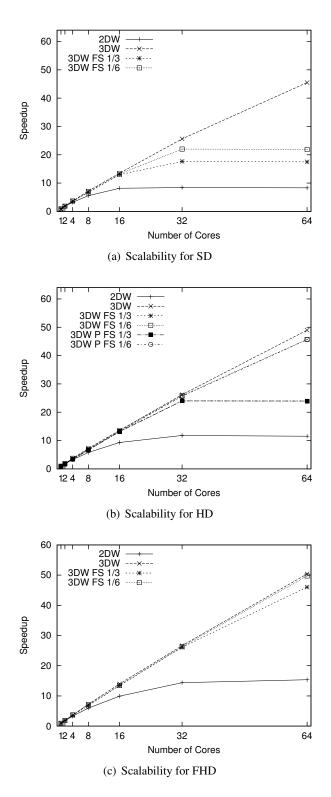

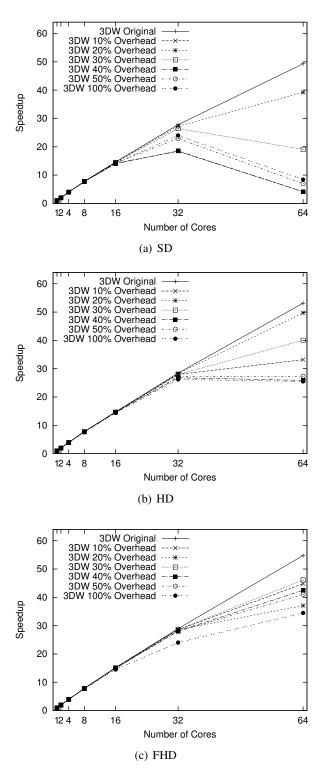

| 3.6  | 2D-Wave and 3D-Wave speedups for the 25-frame sequence Rush Hour for different resolutions                                                                                                                                                                                                                                                           | 50 |

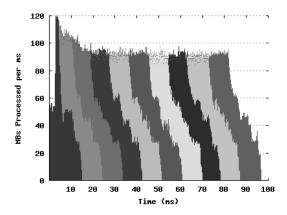

| 3.7  | Number of MBs processed per ms using frame scheduling for FHD Rush Hour on a 16-core processor. Different gray scales represent different frames.                                                                                                                                                                                                    | 52 |

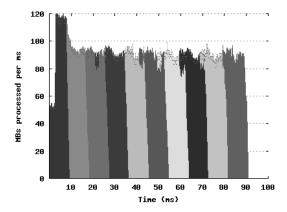

| 3.8  | Number of MBs processed per ms using frame scheduling and priority policy for FHD Rush Hour on a 16-core processor. Different gray scales represent different frames                                                                                                                                                                                 | 53 |

| 3.9  | Frame scheduling and priority scalability results of the Rush                                                                                                                                                                                                                                                                                        | 33 |

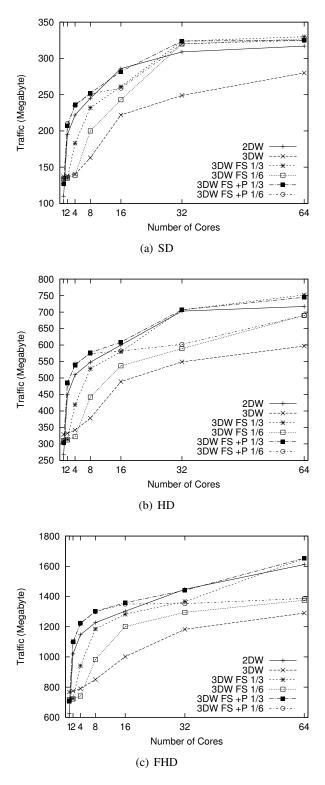

| J.)  | Hour 25-frame sequence                                                                                                                                                                                                                                                                                                                               | 54 |

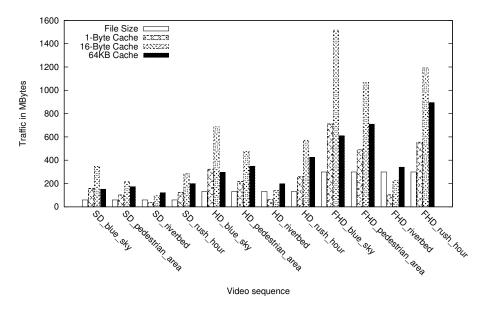

| 3.10 | Frame scheduling and priority data traffic results for Rush                                                                                                                                                                                                                                                                                          |    |

|      | Hour sequence                                                                                                                                                                                                                                                                                                                                        | 56 |

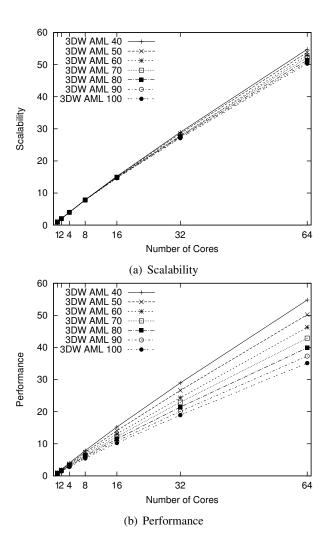

| 3.11 | Scalability and performance for different Average Memory Latency (AML) values, using the 25-frame Rush Hour FHD sequence. In the scalability graph the performance is relative to the execution on a single core, but with the same AML. In the performance graph all values are relative to the execution on a single core with an AML of 40 cycles | 58 |

| 3.12 | Impact of the L1 cache size on performance and L1-L2 traffic for the 25-frame Rush Hour FHD sequence                                                                                                                                                                                                                                                 | 60 |

| 3.13 | TP overhead effects on scalability for Rush Hour frames                                                                                                                                                                                                                                                                                              | 61 |

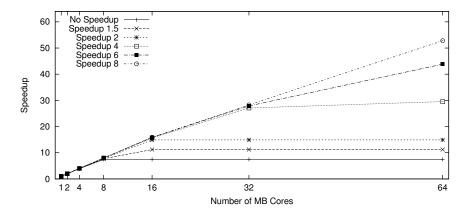

|      | Maximum scalability per CABAC processor and accelerators .                                                                                                                                                                                                                                                                                           | 63 |

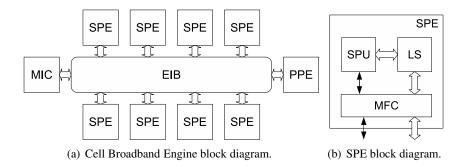

| 4.1  | Cell and SPE block diagrams.                                                                                                                                                                                                                                                                                                                         | 71 |

| 4.2  | Example of compiler managed scalar operation in the SPE                                                                                                                                                                                                                                                                                              | 72 |

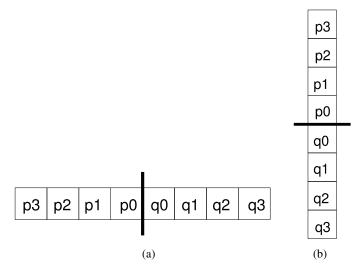

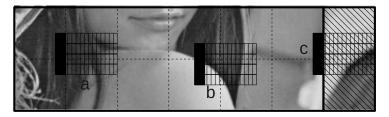

| 4.3  | Line of pixels used for the vertical (a) and the horizontal (b) edges                                                                                                                                                                                                                                                                                | 73 |

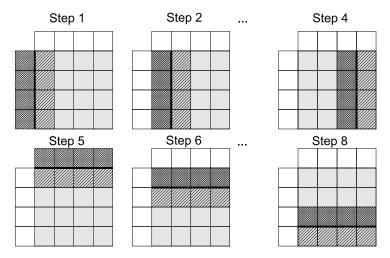

| 4.4  | The filtering process of one macroblock                                                                                                                                                                                                                                                                                                              | 74 |

| 4.5  | Filtering function for Intra MB boundaries                                                                                                                                                                                                                                                                                                           | 75 |

| 4.6  | Filtering function for other MB boundaries                                                                                                                                                                                                                                                                                                           | 75 |

| 4.7  | Double buffering of MB lines                                                                                            | 77  |

|------|-------------------------------------------------------------------------------------------------------------------------|-----|

| 4.8  | Deblocking Filter processing diagram                                                                                    | 77  |

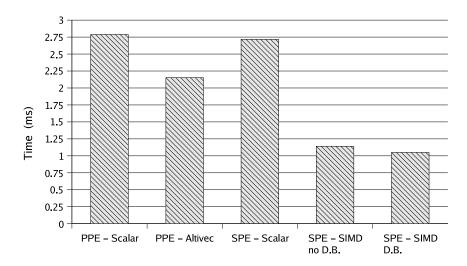

| 4.9  | Average execution time of the deblocking filter implementations for one QVGA frame                                      | 80  |

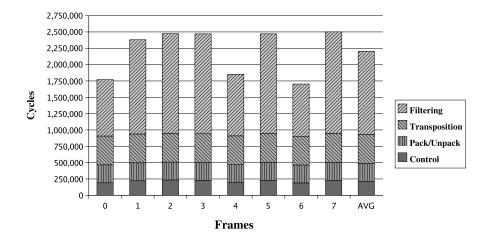

| 4.10 | Execution breakdown of the SPE DF implementation for 8 QVGA frames                                                      | 81  |

| 5.1  | Example of function requiring scalar operations                                                                         | 86  |

| 5.2  | C code of the example kernel after the Large-Data-Type methodology has been applied                                     | 86  |

| 5.3  | Assembly generated from the example function                                                                            | 87  |

| 5.4  | Assembly generated after the Large-Data-Type methodology has been applied to the example function                       | 87  |

| 5.5  | Pseudocode for SAXPY                                                                                                    | 89  |

| 5.6  | Pseudocode for the FIR filter                                                                                           | 89  |

| 5.7  | Pseudocode for Quick Sort                                                                                               | 90  |

| 5.8  | Pseudocode for Merge Sort.                                                                                              | 91  |

| 5.9  | Pseudocode for Image Histogram                                                                                          | 91  |

| 5.10 | Pseudocode for GLCM                                                                                                     | 92  |

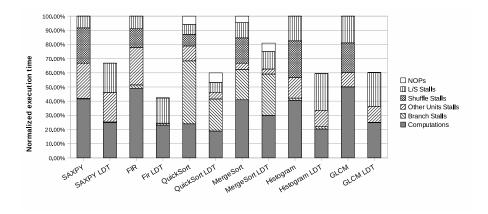

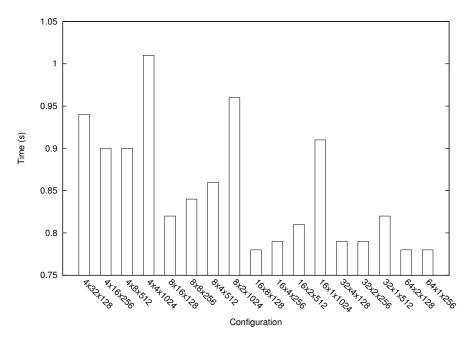

| 5.11 | Execution times of the LDT-emulated kernels normalized to the execution times of the original kernels                   | 95  |

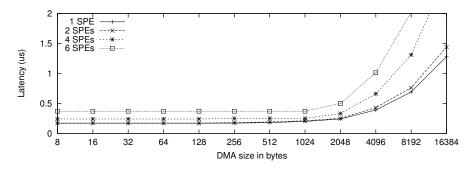

| 6.1  | DMA latency as a function of the transfer size, for several simultaneously communicating SPEs                           | 105 |

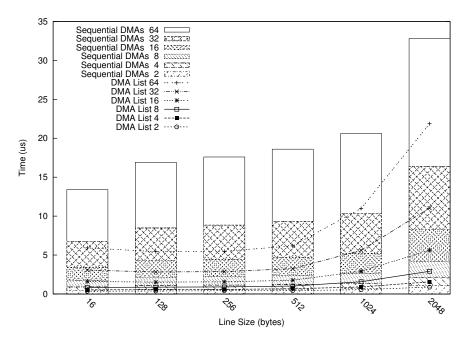

| 6.2  | Latency of DMA list operation compared with a sequence of individual DMAs requests for the same 2D block configuration. | 106 |

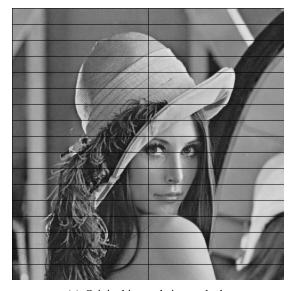

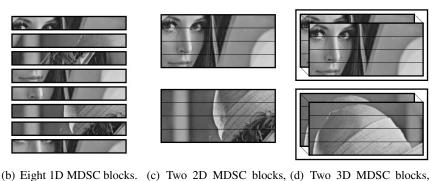

| 6.3  | Examples of 1D, 2D, and 3D MDSC blocks                                                                                  | 108 |

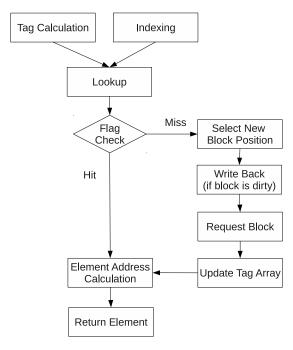

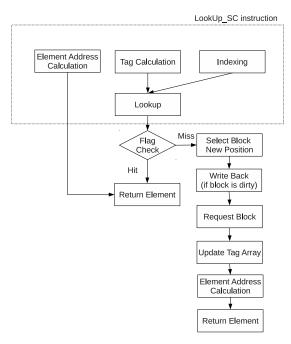

| 6.4  | Flow chart for accessing an element from the MDSC                                                                       | 110 |

| 6.5  | The MDSC configuration interface                                                                                        | 112 |

| 6.6  | Matrix multiplication using 2D MDSC                                                                                     | 114 |

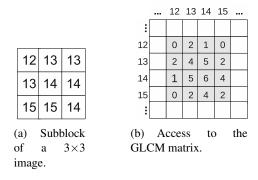

| 6.7  | Second order GLCM of a 3×3 image                                                                                        | 115 |

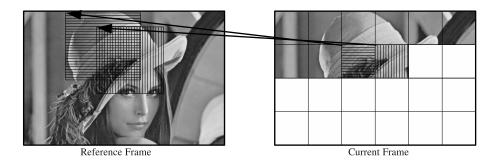

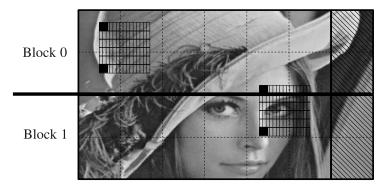

| 6.8  | Motion Compensation of two macroblocks with respective                                                                  | 116 |

| 6.9  | Data locality in MC                                                                                                                                                                                                                                                  | 118 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.10 | A bi-dimensional cache block with the Extended_Line enhancement.                                                                                                                                                                                                     | 121 |

| 6.11 | Example of use of the Extended_XY enhancement                                                                                                                                                                                                                        | 121 |

|      | Time taken by the GLCM kernel for several MDSC configura-                                                                                                                                                                                                            |     |

| 0.12 | tions                                                                                                                                                                                                                                                                | 123 |

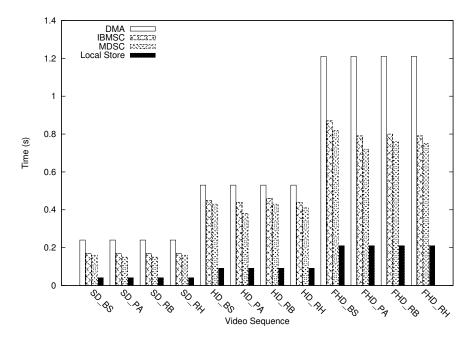

| 6.13 | Time taken by the GLCM kernel for several video sequences when using DMA transfers (DMA), when the optimal IBM SC configuration is employed (IBM SC), when the optimal MDSC configuration is employed (MDSC), and when the GLCM matrix would fit in the Local Store. | 124 |

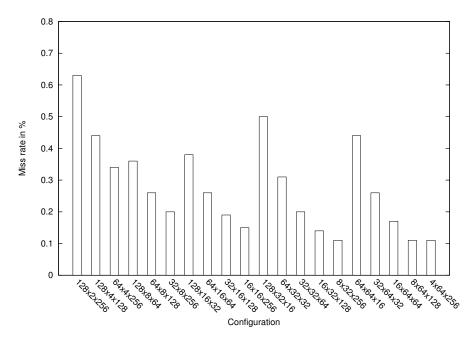

| 6.14 | Miss rate incurred by the MC kernel for different configurations of a 96KB MDSC                                                                                                                                                                                      | 126 |

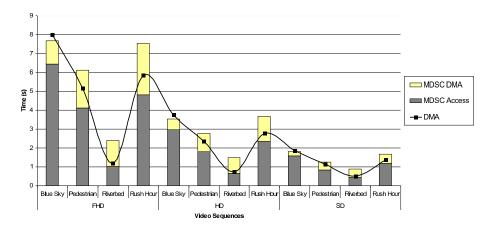

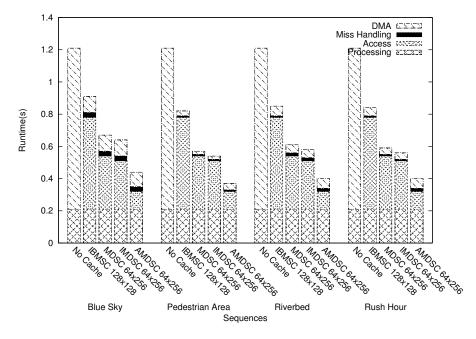

| 6.15 | Breakdown of the time taken by the MC kernel for different input sequences when the baseline MDSC is employed and the time taken when explicit, hand-programmed DMA transfers are used                                                                               | 128 |

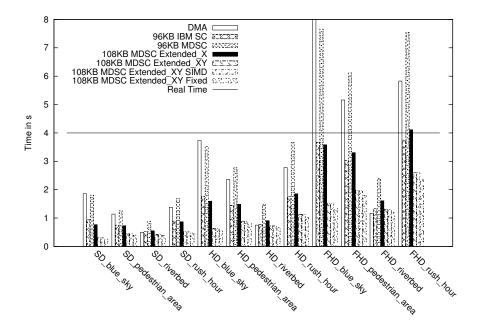

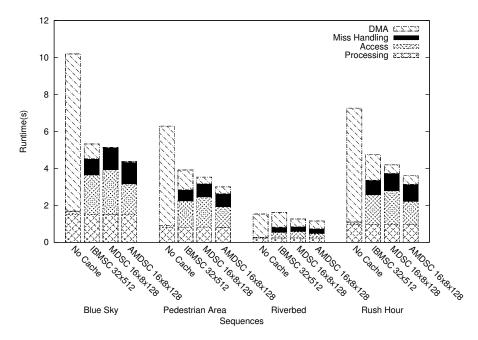

| 6.16 | Time taken by MC for the direct DMA version, the IBM SC, the MDSC, and the various MDSC enhancements                                                                                                                                                                 | 128 |

| 7.1  | LookUp_SC instruction operations and its placement in the read_MDSC function                                                                                                                                                                                         | 135 |

| 7.2  | Pseudo C-code of the LookUp_SC instruction                                                                                                                                                                                                                           | 139 |

| 7.3  | Resulting C code for the read_MDSC function integrated with the LookUp_SC instruction                                                                                                                                                                                | 140 |

| 7.4  | GLCM runtime of FHD sequences for No_Cache, IBMSC, MDSC, inlined MDSC, and AMDSC                                                                                                                                                                                     | 143 |

| 7.5  | MC runtime of FHD sequences for No_Cache, IBMSC, MDSC and AMDSC                                                                                                                                                                                                      | 145 |

# List of Tables

| 2.1 | Static 3D-Wave results of available parallel MBs and number of frames in flight |  |  |

|-----|---------------------------------------------------------------------------------|--|--|

| 2.2 | Number of available parallel MBs with and without the pro-                      |  |  |

|     | posed scheduling technique, for FHD                                             |  |  |

## **Abbreviations**

2DW 2D-Wave 3DW 3D-Wave

Adaptive Block size Transform **ABT**

**AMDSC** Accelerated Multidimensional Software Cache

Average Memory Latency **AML**

**Application Programming Interface** API

**AVC** Advanced Video Coding

Basic Linear Algebra Subprograms **BLAS**

BP **Baseline Profile** BS **Boundary Strength**

Context Adaptive Binary Arithmetic Coding **CABAC CAVLC** Context Adaptive Variable Length Coding CIF

Common Intermediate Format (352×288 pixels)

Discrete Cosine Transform DCT

DΙ Deblocking Info DF **Deblocking Filter** DLP Data Level Parallelism **DMA Direct Memory Access** ED **Entropy Decoding**

**FHD** Full High Definition (1920×1080 pixels)

First-In-First-Out **FIFO**

FIR Finite Impulse Response Flexible Macroblock Ordering **FMO GLCM** Gray-Level Co-occurrence Matrix

**GOP** Group of Pictures

High Definition (1280×720 pixels) HD High Definition Digital Video Disc HD-DVD

HiP High Profile

Intra predicted frame, slice, or macroblock

IDCT Inverse Discrete Cosine Transform

**IEC** International Electrotechnical Commission ILP Instruction Level Parallelism

IQ Inverse Quantization

ISO International Organization for Standardization

KoL Kick-off List

LDT Large-Data-Type

LRU Least Recently Used

LS Local Store

MAP Maximum A Posteriori

MB MacroBlock

MC Motion Compensation

MDSC Multidimensional Software Cache

ME Motion Estimation

MFC Memory Flow Controller

MIC Memory Interface Controller

MIMD Multiple Instruction Multiple Data

MP Main Profile

MPEG Moving Picture Experts Group

MV Motion Vector

MVP Motion Vector Prediction

NoC Network on Chip

P Predicted frame, slice, or macroblock

POC Picture Order Count PP Picture Prediction

PPE Power Processing Element PPU Power Processing Unit

PS3 PlayStation 3

PSNR Peak Signal-to-Noise Ratio

QCIF Quarter Common Intermediate Format (176×144 pixels)

QVGA Quarter Video Graphics Array (320×240 pixels)

RISC Reduced Instruction Set Computer

RMB reference MB

SARC Scalable computer Architecture

SC Software Cache

SD Standard Definition (720×576 pixels)

SIMD Single Instruction Multiple Data

SMT Simultaneous Multi-Threading

SPE Synergistic Processing Element

SPMD Single Program Multiple Data

SPU Synergistic Processing Unit

SSE Streaming SIMD Extensions

STI Sony-Toshiba-IBM

TAGP Tag Array in General Purpose

TARF Tag Array Register File

TLP Thread Level Parallelism

TP Task Pool

UHD Ultra High Definition

UVLC Universal Variable Length Coding

VA Viterbi Algorithm

VCEG Video Coding Experts Group

VLC Variable Length Coding

VLIW Very Large Instruction Word

VP vector prediction XP Extended Profile

ZT Zero-Tail

# Introduction

In the past, increasing computational demand was mainly satisfied by increasing the clock frequency and by exploiting more instruction-level parallelism (ILP). Due to the inability to increase the clock frequency much further because of thermal constraints and because it is difficult to exploit more ILP, multi-core architectures have appeared on the market. As the number of transistors in a die keep increasing as the fabrication technology continuously evolve, it is expected that the number of cores on a chip will double every three years [91]. Current Intel processor Westmere features 6 high performance cores in a single die [54]. AMD also produces a 6 core processor, the Phenom II [30]. The power budget for the processor, however, does not increase, as heat releasing capacity does not have changed. This limits the number of computations that can be performed simultaneously on the processor.

On the other hand, the consumer market pushes higher quality and feature rich media experience. Audio is shifting from lossy (such as MP3) to lossless compression (FLAC [23], DTS-HD Master Audio [31], Dolby TrueHD [28]), even in multichannel formats. High Definition video playback and recording are already present in mobile devices [70] and the next devices capable of decoding 4K (4096×3072) video resolution [73] are being developed [27]. 4K resolution video is even already supported by the internet streaming video service YouTube [84].

Another feature being pushed by the market is the 3D video in stereoscopic (at the time of writing) and soon in freeview (glasses free 3D) formats. Stereoscopic 3D requires 2 different images, one for each eye, to be displayed simultaneously. It relies on glasses that filter the correct image to each eye. Freeview experience, however, is already being advertised [69] and requires up to 9 frames to be displayed simultaneously. These features are covered with amendments in the H.264 standard [92], called Multiview Video Coding (MVC) [19]. In order to decrease the bitstream size, the extra frames depend on the simultaneous and previous ones. This results in an even higher computational complexity than running several independent H.264 streams.

To enable the processing of this new media contents within the limits of the power budget, an increase in power efficiency is needed. One option to increase power efficiency is to parallelize the application on a heterogeneous multi-/many-core processor composed of power efficient cores in tune with the target applications characteristics [53, 52]. This, however, requires thread-level parallelism (TLP) in applications. TPL is the case when different threads or processes can execute simultaneously, either on the same or different data. Moreover, the amount of thread-level parallelism should be sufficient to scale the processing to a large number of cores to provide the required computational power by increasing the number of cores. Fortunately, multimedia processing usually exhibits TLP but current approaches do not scales to large number of cores [66].

Multimedia applications typically also exhibit significant amounts of data-level parallelism (DLP). DLP is the case when the same operation or task can be applied simultaneously on different pieces of data. DLP can be exploited in a power-efficient manner by means of Single-Instruction Multiple-Data (SIMD) operations. SIMD units have been widely used by high-end processors to accelerate multimedia applications. The Sony-Toshiba-IBM (STI) Cell processor [50] brought this concept further. The Cell processor is an heterogeneous multi-core processor that features a general purpose core and 8 SIMD-only cores. SIMD-only cores are cores which instructions operate exclusively on a SIMD fashion, i.e., on all elements of the input vectors simultaneously. Its design has been driven by power efficiency [45].

The shift towards multi-core architectures also brings new challenges for the memory hierarchy. One of these challenges is the design of the memory hierarchy tuned for power efficiency. Scratchpad memories reappeared as a solution because they can be very efficient in terms of power and performance for applications with predictable memory access patterns [12]. Furthermore,

multimedia applications feature mostly predictable data sets and access patterns making it possible to transfer the necessary data before the computation. These data transfers usually need to be explicitly exposed by the programmer. This structure also makes possible to overlap computation and data transfers by means of double buffering techniques. Scratchpad memories also have predictable latencies. However, some multimedia applications do not feature predictable data sets and access patterns. These applications present two significant problems for scratchpad memory based processors. The first problem is that the data transfer cannot be overlapped with the computation. The process has to wait for the data to be transferred to the scratchpad memory. The second problem is that data locality cannot easily be exploited. It is difficult to keep track of the memory area present in the scratchpad memory and new data must be requested for each access.

The remainder of this chapter is organized as follows. Section 1.1 presents the processor architecture template that will be used as the baseline for improvements. The objectives of this thesis are detailed in Section 1.2. The organization and contributions of this thesis are presented in Section 1.3.

#### 1.1 SARC Architecture

This thesis is part of the collaborative Scalable computer ARChitecture (SARC) project [83, 78]. The SARC project aimed at designing a scalable many-core architecture for a wide range of applications. The SARC architecture is a heterogeneous many-core architecture template that is based on a master-worker programming model. It targets a new class of task-based data-flow programming models that includes StarSs [77], Cilk [14, 39], Rapid-Mind [65], Sequoia [36], and OpenMP 3.0 [74, 25]. These programming models allow programmers to write efficient parallel programs by identifying candidate functions to be off-loaded to processing cores.

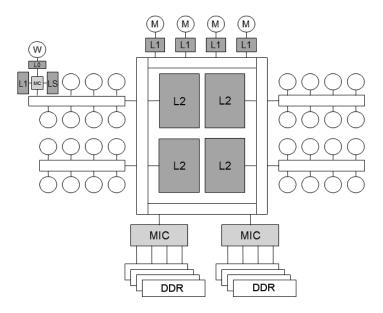

A SARC processor instance consists of Master cores, target applications or application domain accelerators, Network on Chip (NoC), a banked level-2 (L2) cache, and Memory Interface Controllers (MICs). Figure 1.1 depicts the block diagram of a general SARC processor instance. The type and number of the application accelerators as well as the number of master cores, L2 banks, and MICs are implementation dependent. A brief description of each architectural component is given below.

The Master cores are responsible for executing the master threads. The Master cores start the applications and create the threads that will be executed

Figure 1.1: Block diagram of a generic SARC instance.

by the Worker cores. It runs the runtime system, which manages data and task scheduling. A Master core can also create threads for other Master cores that will also spawn Worker threads. Because the system performance depends on the tasks being sequentially spawned by the master core, their single-thread performance is critical. Therefore, they are high-performance out-of-order cores. Master cores rely on data and instruction caches to exploit locality as their working set is not predictable.

Application accelerators consist of a set of locally connected Worker cores. The Worker cores are specialized application or application domain cores. They execute the tasks offloaded from the Master cores. A common feature of the Worker cores is the presence of a scratchpad memory. The scratchpad memory is mapped in the logical address space, so Workers can access scratchpad memories of other Workers. Workers feature a DMA controller to transfer data from/to their scratchpad memories to/from main memory while processing. In this thesis, we will focus on the development of the SARC multimedia instance, including the microarchitecture of the Worker cores.

The SARC NoC consists of a hierarchy of K-buses. A K-bus is a collection of buses. For instance, a 4-bus allows for up to 4 simultaneous data transfers, given the fact that the destination ports are mutually exclusive.

1.2. OBJECTIVES 5

A banked L2 cache is implemented to eliminate the need for maintaining cache coherence. This is possible because data is mapped to a cache bank based on its physical address. The L2 cache in the SARC architecture template captures both misses from L1 caches and DMA transfers. The L2 cache accesses the external memory via the MICs. Each MIC supports several Dynamic Random-Access Memory (DRAM) channels.

The above description of the SARC architecture template is the result of the research realized through the period of the project, from 2006 to 2010, and were not finalized during the development of the work described in this thesis. Because of this, the used architecture template in this thesis is slightly different. The differences are mainly restricted to the memory hierarchy. While in the described architecture template the Worker cores features a cache hierarchy, the version used in this thesis features only a scratchpad memory. Also, the described L2 cache is not featured on the experiments and, therefore, the DMA unit accesses the external memory directly.

Thought this thesis, we use the STI Cell processor and its Synergistic Processing Elements (SPEs) [43] as an architectural emulator for the SARC media instance and the Worker core, respectively. The Cell was chosen because it was, at the beginning of our work, an already available heterogeneous multi-core multimedia accelerator that shares several characteristics with the SARC accelerators. The Cell processor uses a ring buses to connect the SPEs, similarly to the SARC K-buses local connection, and the SPEs are scratchpad memory based cores that transfer data via DMA requests. The Cell processor and the SPE cores are described in detail in Section 4.3.

## 1.2 Objectives

In the design of the SARC multimedia instance, we focus on three topics to achieve efficient execution of video coding applications on many-cores processors. TLP, DLP, and memory hierarchy need to be efficiently exploited in order to scale the computational throughput with the number of cores. Improvements on each of these topics correspond to the main objectives of this thesis.

Current parallelization techniques for high definition (from  $1280 \times 720$  to  $1920 \times 1080$  pixels) video processing do not properly scale over 8 cores [66, 22]. Therefore, the first objective of this thesis is to leverage video coding applications to the forthcoming many-core era. This is key for the development of many-core processors because if there is not sufficient parallelism, most of the

cores will be idle or under utilized. The solution should exhibit high scalability with increasing number of cores in order to be able to provide the required performance for future applications. The solution should also be feasible in terms of processing latency and memory requirements, among others.

Identifying and eliminating bottlenecks in the execution on SIMD-only cores is the second objective of this thesis. SIMD processing has well documented processing overheads [80, 89, 8], such as data transpositions, data (un)packing, and alignment. Transposition is the operation of writing the columns of a matrix A as the rows of a matrix  $A^T$ . This operation is required when data store in row-wise form (in single memory word) need to be computed in a column-wise fashion (in separated memory words). Data packing is the selection of data scattered over memory words into a SIMD word while unpacking is the merging of the contents of the SIMD word back with the original content of the memory words. Alignment issues happen when the data to be processed are split in two consecutive SIMD words, as they need to be combined in one single word to be processed. SIMD-only cores introduces new aspects, in contrast with cores with SIMD units, that lead to overheads. These specific SIMD-only overheads and how they could be eliminated are still an open topic.

Finally, the third objective of this thesis is to increase the effectiveness and efficiency of scratchpad memories for unpredictable memory accesses. In general, scratchpad memories are power efficient and fit well with the characteristics of video coding applications, as well as other multimedia applications. Some multimedia kernels, however, present access behaviors that do not allow the request of required data in advance. In this case, the core will have to stall while waiting for the data. One solution for such kernels with irregular and indirect data accesses is to use software caches. Software caches, however, incur significant overhead with the cache access being the dominant overhead, as will be demonstrated later in this thesis. Software and hardware alternatives should be analyzed in order to reduce software cache overhead.

### 1.3 Organization and Contributions

As mentioned in the previous section, we focus in three topics: TLP, DLP, and memory hierarchy. Each of these topics is addressed in a set of two chapters as follows. Chapters 2 and 3 deals with the exploitation of TLP in video processing for many-core architectures. It is followed, in Chapters 4 and 5, by the evaluation of SIMD-only cores for divergent branching kernels and scalar pro-

cessing. Solutions for increasing efficiency and efficacy of scratchpad memories for unpredictable and indirect memory accesses are presented in Chapters 6 and 7. The contributions of this thesis and the contents of each chapter are presented below.

The first main contribution of this thesis is the 3D-Wave video (de)coding parallelization strategy that scales to a large number of cores. This strategy breaks frame dependencies in a novel way by overlapping the (de)coding of several inter-dependent frames and stressing the MB parallelism that can be exploited. We choose the H.264 as our target video decoding standard due to its high computational demands and wide utilization. In order to evaluate the potential of the 3D-Wave strategy, the Static 3D-Wave evaluation methodology is introduced in Chapter 2. The Static 3D-Wave calculates the number of macroblocks (MBs) that can be processed in parallel given a maximum motion vector length, where each MB has a fixed decoding time. A second evaluation methodology, called Dynamic 3D-Wave, is also presented. It computes the number of MBs that can be processed in parallel by evaluating the MB dependencies chain in a given video sequence. A fixed MB decoding time is also assumed. Chapter 2 also briefly presents the H.264 standard and review previous parallelization techniques for video (de)coding.

Implementing the 3D-Wave in a simulated many-core processor turned out to be quite challenging and led to several contributions. A mechanism that guarantees that MBs are not processed before their intra and inter frame dependencies are satisfied is presented. Furthermore, a decoding policy is introduced to reduce the latency of the technique given the number of frames decoded simultaneously. In addition, in order to control the size of the working memory, a frame scheduling policy is introduced to control the number of frames in flight. Memory latency, impact of L1 cache size, impact of task management latency, and entropy decoding acceleration are also evaluated. The implementation of the 3D-Wave and the above contributions and evaluations are described in Chapter 3.

The second main contribution of this thesis is the assessment of SIMD-only cores for divergent branching multimedia kernels. As a case study, the highly adaptive H.264 Deblocking Filter (DF) kernel is vectorized with SIMD instructions on the Worker core. The vectorized DF execution is analyzed and its overheads are classified into SIMD and divergent branching related. For comparison, the DF is also vectorized with SIMD instructions in a similar general purpose core with a SIMD processing unit. The described assessment is presented in Chapter 4. Chapter 4 also presents a brief description of the

DF kernel, a literature review on SIMD overhead, and a description of the Cell processor with focus on the SPE (used to emulate the Worker core).

The quantification of the scalar processing overhead on SIMD-only cores is the third main contribution of this thesis. The scalar processing in current SIMD-only cores is handled by the compiler. The compiler introduces a number of operations to guarantee the correct program semantic. These operations, however, introduce overhead in terms of extra instructions to be executed and pipeline stalls. Two evaluation methodologies are developed in order to quantify the overhead. The first methodology, called Large-Data-Type, eliminates the sources of scalar processing overhead in SIMD-only cores by increasing the size of the scalar word to 128 bits. Without the sources of overhead, the program execution in the SIMD-only core is equal to a program execution in a core with scalar support. The second methodology compares the execution times of kernels in the SIMD-only core with a similar core with scalar support. Additionally, special load and store instructions that minimize the scalar overhead are presented. The scalar overhead evaluation and the proposed instructions are presented in Chapter 5.

In Chapter 6, we contribute by presenting a novel Multidimensional Software Cache (MDSC) organization for scratchpad memory based cores that reduces software cache overhead. The MDSC reduces the software cache overhead on two fronts. First, it allows the exploitation of known access behavior to minimize the number of cache accesses. This exploitation is enabled by the use of matrix indices instead of linear addresses combined with the multi-dimensional cache blocks. For instance, if the programmer (or the compiler) identifies access patterns in the program that are restricted to a small number of cache blocks, the first access to the cache block is kept while the subsequent accesses can be replaced by pointer arithmetic. Second, the MDSC groups multiple external memory requests, which reduces latency when compared with the sum of individual transfers.

The last main contribution of this thesis is an instruction to accelerate the MDSC. The proposed instruction, called LookUp\_SC, performs the tag formation, cache look-up, and address calculation. These steps are the main body of the MDSC access functions that are the predominant overhead of the MDSC, as will be presented on Chapter 6. Nevertheless, these steps consist of operations that are sufficiently simple to be implemented in hardware and many steps can be performed in parallel. The LookUp\_SC instruction resulted in speedups ranging from 1.28 to 2.1 in the evaluated kernels. The description and evaluation of the LookUp\_SC instruction is presented in Chapter 7.

Chapter 8 concludes this dissertation. A summary of the presented content and contributions are given. Chapter 8 also includes directions on how the work can be extended in the future, based on the acquired results.

Because the contributions of this thesis relate to different topics, there is no separated related work chapter. Instead, the related work will be presented per chapter or per group of chapters, in order to provide easiness of reference and to obtain a more consistent structure of the thesis.

# 2

# A Scalable Parallel Algorithm for H.264 Decoding

s argued in Chapter 1, an important question is whether emerging and future applications exhibit sufficient parallelism, in particular thread-level parallelism (TLP), to exploit the large numbers of cores future many-core processors are expected to contain. In this chapter, we investigate the amount of TLP available in video coders/decoders (codecs), an important application domain now and in the future. Specifically, we analyze and present a method to enhance the parallel scalability of the H.264 [92] decoding process.

This chapter is organized as follows. Section 2.1 briefly introduces the need and applicability of scaling video processing to many-core architectures. Section 2.2 presents a short overview of the H.264 standard. Possible parallelization techniques for H.264 and related work are reviewed in the Section 2.3. In Section 2.4, we present a novel parallelization strategy called 3D-Wave and analyze the amount of TLP it exhibits using a static approach. Section 2.5 discusses the effects of limiting resources available to the 3D-Wave strategy. A dynamic 3D-Wave evaluation that takes real macroblock (MB) dependencies into account is briefly presented in Section 2.6. Section 2.7 concludes this chapter.

#### 2.1 Introduction

The demand for computational power increases continuously in the consumer market as new applications such as Ultra High Definition (UHD) video [73], 3D TV [29], and real-time High Definition (HD) video encoding are forecasted. In the past this demand was mainly satisfied by increasing the clock frequency and by exploiting more instruction-level parallelism (ILP). As noted in Chapter 1, however, due to the inability to increase the clock frequency much further because of thermal constraints and because it is difficult to exploit more ILP, multi-core architectures have appeared on the market.

This new paradigm relies on the existence of sufficient thread-level parallelism (TLP) to exploit large number of cores. Techniques to extract TLP from applications will be crucial to the success of multi-cores. This chapter investigates the exploitation of the TLP available in an H.264 video decoder on an multi-core processor H.264 was chosen due to its high computational demands, wide utilization, and development maturity. Furthermore, even more demanding applications such as 3D TV are based on current video coding methods [68]. Although a 64-core processor is not required to decode a Full High Definition (FHD) video in real-time, real-time encoding remains a problem, and decoding, furthermore, is part of encoding.

In this chapter we propose a novel parallelization strategy, called 3D-Wave, for H.264 decoding which is scalable to a large number of cores. It is mainly based on the observation that inter-frame dependencies have a limited spatial range. Because of this, certain MBs of consecutive frames can be decoded in parallel. In this chapter, we analyze the available MB-level parallelism using a static approach, called Static 3D-Wave. In this static approach, the decoding of the next frame is started as soon as the reference window of the upper-left MB is decoded, given an arbitrary maximum motion vector (MV) length. We use arbitrary MV lengths because the actual MV lengths on real sequences are much smaller than the maximum MV length allowed by the H.264 standard, as we will present in Section 2.6. In Section 2.6 we also consider the actual MV length and analyze how this affects the scalability. This will be used as basis for the implementation described in Chapter 3.

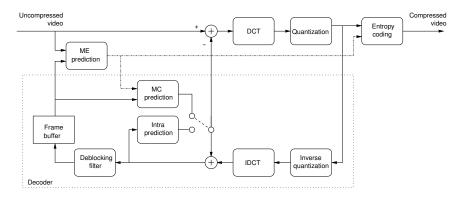

Although our focus in this chapter is on the decoder, the proposed technique is also suitable for parallelizing the encoder. Because in the encoder the dependencies are known a priori, however, it is easier to apply the 3D-Wave to the encoder than to the decoder. Due to the restrictions and challenges in the decoder, it was chosen as the target of this study.

This chapter is the result of a close collaboration effort with two other PhD students, Cor Meenderinck and Mauricio Alvarez. Their work is presented mainly in the introductory sections of this chapter. Credit will be given where it is due. Broadly, we made the observation which forms the basis of the 3D-Wave strategy and performed an initial evaluation using the static approach, while Cor Meenderinck performed the dynamic analysis, and Mauricio Alvarez reviewed the related literature.

#### 2.2 Overview of the H.264 Standard \*

Currently, one of the leading video coding standard, in terms of compression and quality is H.264 [2, 72]. It is used in Blu-Ray Disc, internet streaming, and many countries are using or will use it for terrestrial television broadcast, satellite broadcast, and mobile television services. It has a compression improvement of over two times compared to previous standards such as MPEG-4 ASP and H.262/MPEG-2 [98]. The H.264 standard was designed to serve a broad range of application domains ranging from low to high bitrates, from low to high resolutions, and a variety of networks and systems, e.g., internet streams, mobile streams, disc storage, and broadcast. The H.264 standard was jointly developed by ITU-T Video Coding Experts Group (VCEG) and ISO/IEC Moving Picture Experts Group (MPEG). It is also called MPEG-4 part 10 or AVC (Advanced Video Coding).

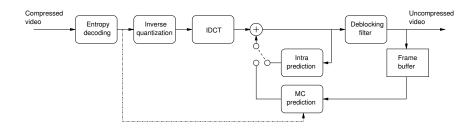

Figures 2.1 and 2.2 depict block diagrams of the decoding and the encoding process of H.264, respectively. The main kernels are Prediction (intra prediction, Motion Estimation (ME), and Motion Compensation (MC)), Discrete Cosine Transform (DCT), Quantization, Deblocking filter, and Entropy Coding. They operate on macroblocks (MBs), which are blocks of  $16 \times 16$  pixels, although the standard allows some kernels to operate on smaller blocks, down to  $4 \times 4$ . H.264 uses the YCbCr color space with a 4:2:0 subsampling.

Advances in ME/MC is one of the major contributors to the compression improvement of H.264. The standard allows variable block sizes ranging from  $16 \times 16$  down to  $4 \times 4$ , and each block has its own MV(s). The MV is quarter sample accurate. Furthermore, multiple reference frames can be used in a weighted fashion. This significantly improves coding occlusion areas where an accurate prediction can only be made from a frame further in the past. The MC kernel will be further detailed in Chapter 6.

<sup>\*</sup>This section is based on text written mainly by Cor Meenderinck.

Figure 2.1: Block diagram of the decoding process.

Figure 2.2: Block diagram of the encoding process.

Two types of intra coding are supported, which are denoted as In $tra_4 \times 4$  and  $Intra_16 \times 16$ . The first type uses spatial prediction on each  $4 \times 4$ luminance block. Eight modes of directional prediction are available, among them horizontal, vertical, and diagonal. This mode is well suited for MBs with small details. For smooth image areas the Intra\_16×16 type is more suitable, for which four prediction modes are available. Chroma components are estimated for whole MBs using one specialized prediction mode.

MPEG-2 and MPEG-4 part 2 employed an 8 × 8 floating point transform. However, due to the decreased granularity of the motion estimation, there is less spatial correlation in the residual signal. Thus, a standard  $4 \times 4$ (that means  $2 \times 2$  for chrominance) transform is used, which is as efficient as a larger transform [63]. Moreover, a smaller block size reduces artifacts known as ringing and blocking. An optional feature of H.264 is Adaptive Block size Transform (ABT), which adapts the block size used for DCT to the size used in motion estimation [100]. Furthermore, to prevent rounding errors that occur in floating point implementations, an integer transform was chosen.

Processing a frame in MBs can produce blocking artifacts, generally considered the most visible artifact in prior standards. This effect can be resolved by applying a deblocking filter around the edges of a block. The strength of the filter is adaptable through several syntax elements [59]. While in H.263+ this feature was optional, in H.264 it is standard and it is placed within the motion compensated prediction loop (see Figure 2.1) to improve the motion estimation. The Deblocking Filter will be further detailed in Chapter 4.

There are two classes of entropy coding available in H.264: Variable Length Coding (VLC) and Context Adaptive Binary Arithmetic Coding (CABAC). The latter achieves up to 10% better compression but at the cost of large computational complexity [64]. The VLC class consists of Context Adaptive VLC (CAVLC) for the transform coefficients, and Universal VLC (UVLC) for the small remaining part. CAVLC achieves large improvements over simple VLC, used in prior standards, without the full computational cost of CABAC.

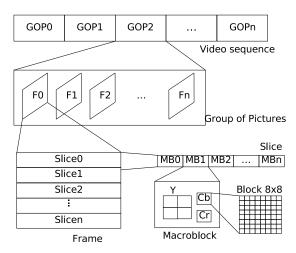

Figure 2.3 depicts how the video data is structured in H.264. A video sequence is composed out of Group of Pictures (GOPs) which are independent sections of the video sequence. GOPs are used for synchronization purposes because there are no temporal dependencies between them. Each GOP is composed by a set of frames, which can have temporal dependencies when motion prediction is used. Each frame can be composed of one or more slices. The slice is the basic unit for encoding and decoding. Each slice is a set of MBs and there are no temporal or spatial dependencies between slices. Further, there are MBs, which are the basic units of prediction. MBs are composed of luma and chroma blocks of variable size. Finally each block is composed of picture samples. Data-level parallelism can be exploited at each level of the data structure, each one having different constraints and requiring different parallelization methodologies.

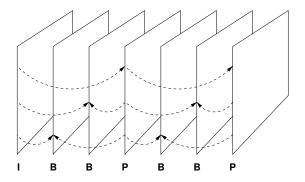

H.264 defines three main types of slices and macroblocks: I, P, and B. An I-slice uses intra prediction MBs (I MBs) and is independent of other slices. In intra prediction a MB is predicted based on adjacent blocks. A P-slice is composed of I and P MBs. A P-MB uses motion estimation and depends on one or more previous slices, either I or P. Motion estimation is used to exploit temporal correlation between slices. Finally, B-slices are composed of I, P and B MBs. A B-MB uses bidirectional motion estimation and depends on slices from past and future [38]. Figure 2.4 depicts a typical slice order and the dependencies, assuming each frame consists of one slice only. The standard

Figure 2.3: H.264 data structure.

Figure 2.4: A typical slice/frame sequence and its dependencies.

also defines SI and SP slices that are slightly different from the ones mentioned before and which are targeted at mobile and internet streaming applications.

The standard was designed to suite a broad range of video application domains. Each domain, however, is expected to use only a subset of the available options. For this reason profiles and levels were specified to mark conformance points. Encoders and decoders that conform to the same profile are guaranteed to inter-operate correctly. Profiles define sets of coding tools and algorithms that can be used while levels place constraints on the parameters of the bitstream.

The standard initially defined three profiles, but has since then been extended to a total of 11 profiles, including three main profiles, four high profiles,

and four all-intra profiles. The three main profiles and the most important high profile are:

- Baseline Profile (BP): the simplest profile mainly used for video conferencing and mobile video.

- Main Profile (MP): intended to be used for consumer broadcast and storage applications, has been overtaken by the high profile.

- Extended Profile (XP): intended for streaming video and includes special capabilities to improve robustness.

- High Profile (HiP) intended for high definition broadcast and disc storage, and is used in HD DVD and Blu-ray.

Besides HiP there are three other high profiles that support up to 14 bits per sample, 4:2:2 and 4:4:4 sampling, and other features [92]. The all-intra profiles are similar to the high profiles and are mainly used in professional camera and editing systems.

In addition 16 levels are currently defined which are used for all profiles. A level specifies, for example, the upper limit for the picture size, the decoder processing rate, the size of the multi-picture buffers, and the video bitrate. Levels have profile independent parameters as well as profile specific ones. The H.264 standard has many options. For more details the interested reader is referred to [99, 93].

# 2.3 Parallelizing H.264 <sup>†</sup>

The coding efficiency gains of advanced video codecs such as H.264 come at the price of increased computational requirements. The demands for computing power increases also with the shift towards high definition resolutions. As a result, current high performance uniprocessor architectures are not capable of providing the required performance for real-time processing [5, 76, 55, 47].

In order to obtain the required performance for real-time operation at high definition, it is necessary to exploit parallelism. The H.264 codec can be parallelized either by a task-level or a data-level decomposition. Each technique has advantages and disadvantages. In this section we examine both and compare them in terms of communication and synchronization requirements, load balancing, and scalability.

<sup>&</sup>lt;sup>†</sup>This section is based on text written mainly by Mauricio Alvarez.

#### 2.3.1 Task-Level Decomposition

In a task-level decomposition the functional partitions of the algorithm are assigned to different processors. As depicted in Figure 2.1, the process of decoding H.264 consists of performing a series of operations on the coded input bitstream. Some of these tasks can be done in parallel and the processing can be pipelined where the results of one task are streamed as input to the next.

Because of this streaming behavior, task-level decomposition requires a significant amount of communication between the different tasks in order to send the data from one processing stage to the other, and this may become a bottleneck. Additionally, synchronization between the modules is required.

The main drawbacks, however, of task-level decomposition are poor load balancing and limited scalability. Balancing the load is difficult because the time to execute each task is not known before hand and depends on the data being processed. Scalability is also difficult to achieve because increasing the number of processors requires to redistribute the tasks and a new load balancing of the pipeline. Finally, from the software optimization perspective, the task-level decomposition requires that each task/processor implements a specific software optimization strategy.

Gulati et al. [44] describe a system for encoding and decoding H.264 on a multiprocessor architecture using a task-level decomposition approach. The employed multiprocessor includes eight DSPs and four control processors. This system achieves real-time operation for low resolution video inputs, using the baseline profile which is a limited set of the H.264 standard features (e.g., no CABAC, no B-frames).

#### 2.3.2 Data-Level Decomposition

In a data-level decomposition the work (data) is divided into smaller parts and each of the parts is assigned to a different processor. Each processor runs the same program but on different (multiple) data elements (SPMD). In H.264 data decomposition can be applied at different levels of the data structure.

#### 2.3.2.1 GOP-Level Parallelism

The coarsest grained parallelism is at the GOP-level (see Figure 2.3.2). H.264 can be parallelized at the GOP-level by defining a GOP size of N frames and assigning each GOP to a different processor. GOP-level parallelism requires

a significant amount of memory for storing all the frames, and therefore this technique maps well to multicomputers in which each processing node has a lot of computational and memory resources. Additionally, parallelization at the GOP-level results in a very high latency that cannot be tolerated in some applications. This scheme is not well suited for multi-core architectures, in which the memory is shared by all the processors, because the working set is likely larger than the last-level of shared cache.

Rodriguez et al. [81] implemented the H.264 *encoder* using GOP- (and slice-) level parallelism on a cluster of workstations using MPI. Although real-time operation can be achieved with such an approach, the latency is very high.

#### 2.3.2.2 Frame-Level Parallelism

The next level after GOP-level is frame-level parallelism. As shown in Figure 2.4, in an I-P-B-B frame sequence inside a GOP, some frames are used as reference frames for other frames (such as I and P frames), while some other frames (B frames) are not used as reference frames. That means that different B frames can be processed in parallel. In this case, a control processor can assign independent frames to different processors. Frame-level parallelism achieves good load balancing but has scalability problems. This is due to the fact that usually there are no more than two or three B frames between P frames. This limits the amount of TLP to a few threads. The main disadvantage of frame-level parallelism, however, is that, unlike previous video standards, in H.264 B frames can be used as reference frames. In that case, the encoder cannot use B frames as reference if the decoder wants to exploit frame-level parallelism. This might increase the bitrate, but more importantly, encoding and decoding are usually completely separated and there is no way for a decoder to enforce its preferences on the encoder.

Frame-level parallelism has been implemented in the open-source encoder x264 [102] and is also described in the work of Chen et al. [20], where a combination of frame-level and slice-level parallelism is proposed. To obtain frame-level parallelism they do not allow to use B-frames as reference in the encoder and use a static I-P-B-B-P-B-B frame sequence. They obtain a  $3.8 \times$  speedup on a machine with 4 cores. Their approach, however, does not scale to more processors.

#### 2.3.2.3 Slice-Level Parallelism

In H.264 as well as in most current hybrid video coding standards, each picture is partitioned into one or more slices. Slices have been included in order to add robustness to the encoded bitstream in the presence of network transmission errors and losses. In order to accomplish this, slices in a frame should be completely independent from each other. That means that no content of a slice is used to predict elements of other slices (in the same frame) [99, 92]. Although support for slices have been designed for error resilience, it can be used for exploiting TLP because slices in a frame can be encoded or decoded in parallel. The main advantage of slices is that they do not have dependency or ordering constraints. This allows exploiting slice-level parallelism without making significant changes to the code.

There are a number of disadvantages associated with exploiting TLP at the slice-level, however. First, in H.264 the number of slices per frame is determined by the encoder. That poses a scalability problem for parallelization at the decoder level as the encoder can produce frames with only one slice. Second, H.264 includes a deblocking filter that can be applied across slice boundaries and thus making them dependent. Finally, the main disadvantage of slices is that an increase of the number of slices per frame increases the bitrate for the same quality level (or, equivalently, it reduces quality for the same bitrate level). Meenderinck et al. [66] report that when the number of slices increases to 32 slices the bitrate increase ranges from 3% to 24%, and when going to 64 slices the increase ranges from 4% to 34%. For some applications this bitrate increase is unacceptable and thus using a large number of slices to obtain high scalability is not feasible.

Several works have proposed to utilize slice-level parallelism in order to exploit TLP in the H.264 encoder and/or decoder. In [21, 20] a combination of frame-level and slice-level parallelism is proposed for IA32 Pentium processors with Simultaneous Multi-Threading (SMT) and CMP multi-threading capabilities. The proposed algorithm first exploits frame-level parallelism and when the limit of independent frames is reached, slice-level parallelism is additionally exploited. This scheme cannot scale to a large number of processors because of the limited frame-level parallelism and the coding efficiency limitations of having a large number of slices. In [82] a scheme is proposed for exploiting slice-level parallelism in the H.264 decoder by modifying the encoder. The main idea is to overcome the load balancing disadvantage by developing an encoder that produces slices that are not balanced in the number of MBs, but in their decoding time. The main disadvantages of this approach

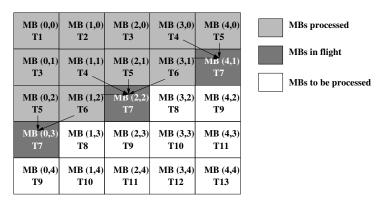

**Figure 2.5:** 2D-Wave approach for exploiting MB parallelism. The arrows indicate dependencies.