Computer Engineering Mekelweg 4, 2628 CD Delft The Netherlands http://ce.et.tudelft.nl/

# MSc THESIS

# Run-Time Partial Reconfiguration on the Virtex-II Pro

Stefan Raaijmakers

#### Abstract

**Delft University of Technology**

Reconfigurable Computing entails the utilization of a generalpurpose processor augmented with a reconfigurable hardware structure (e.g. a field-programmable gate array). Normally, a complete reconfiguration is needed to change the functionality of the FPGA even when the change is only minor. Moreover, the complete chip needs to be halted to perform the reconfiguration. Dynamic partial reconfiguration (DPR) enables the possibility to change parts of the hardware while other parts of the FPGA remain in use.

In this paper, we propose an additional solution to perform dynamic partial reconfiguration by providing a methodology to generate bitstreams for removal of old hardware, and placement and routing of new hardware within an FPGA. This means that functionality can be removed from, and additional functionality can be added to the FPGA at any location. Our solution is able of connecting the additional functionality to the already running parts of the chip. More over, bus macros are no longer necessary and no synthesis is needed to implement the routing. We implemented our solution on a Xilinx Virtex-II Pro series FPGA, specifically the XC2VP30 on the XUP board, and demonstrated that the solution works.

Faculty of Electrical Engineering, Mathematics and Computer Science

# Run-Time Partial Reconfiguration on the Virtex-II Pro Generating bitstreams for adding and removing hardware and signal routing

## THESIS

submitted in partial fulfillment of the requirements for the degree of

#### MASTER OF SCIENCE

in

## COMPUTER ENGINEERING

by

Stefan Raaijmakers born in Haarlem, the Netherlands

Computer Engineering Department of Electrical Engineering Faculty of Electrical Engineering, Mathematics and Computer Science Delft University of Technology

# Run-Time Partial Reconfiguration on the Virtex-II Pro

# by Stefan Raaijmakers

# Abstract

| Laboratory<br>Codenumber | : | Computer I<br>CE-MS-200 | 0 0                                |

|--------------------------|---|-------------------------|------------------------------------|

| Committee Members        | : |                         |                                    |

| Advisor:                 |   |                         | Stephan Wong                       |

| Chairperson:             |   |                         | Stamatis Vassiliadis, CE, TU Delft |

| Member:                  |   |                         | Stephan Wong                       |

| Member:                  |   |                         | Nick van der Meijs                 |

| Member:                  |   |                         | Georgy Gaydadjiev                  |

# Contents

| Li            | st of          | Figures                                 | $\mathbf{v}$ |  |  |  |  |  |  |  |  |  |  |  |

|---------------|----------------|-----------------------------------------|--------------|--|--|--|--|--|--|--|--|--|--|--|

| $\mathbf{Li}$ | bist of Tables |                                         |              |  |  |  |  |  |  |  |  |  |  |  |

| 1             | Intr           | oduction                                | 1            |  |  |  |  |  |  |  |  |  |  |  |

|               | 1.1            | Reconfigurable Computing                | 2            |  |  |  |  |  |  |  |  |  |  |  |

|               | 1.2            | Field-programmable gate arrays          | 3            |  |  |  |  |  |  |  |  |  |  |  |

|               | 1.3            | Problem Statement                       | 5            |  |  |  |  |  |  |  |  |  |  |  |

|               | 1.4            | Goal and Methodology                    | 5            |  |  |  |  |  |  |  |  |  |  |  |

|               | 1.5            | CE Research in Reconfigurable Computing | 6            |  |  |  |  |  |  |  |  |  |  |  |

|               |                | 1.5.1 Delft Workbench                   | 7            |  |  |  |  |  |  |  |  |  |  |  |

|               |                | 1.5.2 Molen                             | 7            |  |  |  |  |  |  |  |  |  |  |  |

|               | 1.6            | Overview                                | 7            |  |  |  |  |  |  |  |  |  |  |  |

| <b>2</b> | Bac                      | ckground                                                   | 9                                                  |

|----------|--------------------------|------------------------------------------------------------|----------------------------------------------------|

|          | 2.1                      | Related Work                                               | 10                                                 |

|          |                          | 2.1.1 1 Dimensional Placement, Mostly circuit switched     | 10                                                 |

|          |                          | 2.1.2 2D Placement, Mostly Network-on-Chip                 | 11                                                 |

|          | 2.2                      | Xilinx Virtex-II Pro                                       | 13                                                 |

|          | 2.3                      | Xilinx Design Flow for static configurations.              | 17                                                 |

|          | 2.4                      | Partial Reconfiguration Using the XAPP290 Design Flow      | 19                                                 |

|          | 2.5                      | Proposed Method for Partial Reconfiguration                | 21                                                 |

|          |                          | 2.5.1 Proposed Design flow, Building the Modules           | 21                                                 |

|          |                          | 2.5.2 Proposed Approach to Runtime Partial Reconfiguration | 21                                                 |

|          |                          | 2.5.3 Advantages and Disadvantages                         | 23                                                 |

|          |                          | 2.5.4 Conclusion                                           | 24                                                 |

|          |                          |                                                            |                                                    |

| 3        | Wo                       | rk                                                         | <b>25</b>                                          |

| 3        | <b>Wo</b><br>3.1         | <b>rk</b><br>Resources in the FPGA                         | <b>25</b><br>25                                    |

| 3        |                          |                                                            |                                                    |

| 3        | 3.1                      | Resources in the FPGA                                      | 25                                                 |

| 3        | $3.1 \\ 3.2$             | Resources in the FPGA                                      | $\frac{25}{26}$                                    |

| 3        | 3.1<br>3.2<br>3.3        | Resources in the FPGA                                      | 25<br>26<br>26                                     |

| 3        | 3.1<br>3.2<br>3.3        | Resources in the FPGA                                      | 25<br>26<br>26<br>27                               |

| 3        | 3.1<br>3.2<br>3.3        | Resources in the FPGA                                      | 25<br>26<br>26<br>27<br>27                         |

| 3        | 3.1<br>3.2<br>3.3        | Resources in the FPGA                                      | 25<br>26<br>26<br>27<br>27<br>27<br>30             |

| 3        | 3.1<br>3.2<br>3.3        | Resources in the FPGA                                      | 25<br>26<br>26<br>27<br>27<br>27<br>30<br>32       |

| 3        | 3.1<br>3.2<br>3.3<br>3.4 | Resources in the FPGA                                      | 25<br>26<br>26<br>27<br>27<br>27<br>30<br>32<br>34 |

|          |                      | 3.6.1 Hardware Core Isolation                                   | 36 |

|----------|----------------------|-----------------------------------------------------------------|----|

|          |                      | 3.6.2 Unrouting                                                 | 37 |

|          |                      | 3.6.3 Hardware Core Placement                                   | 37 |

|          | 3.7                  | Device Composition Description                                  | 37 |

|          | 3.8                  | Partial Reconfiguration                                         | 38 |

|          | 3.9                  | Verification of Data and Methodology                            | 39 |

|          | 3.10                 | Conclusion                                                      | 39 |

| 4        | $\operatorname{Res}$ | ults                                                            | 41 |

|          | 4.1                  | Testing Feasibility                                             | 41 |

|          | 4.2                  | Testing Runtime Reconfiguration for Building Partial Bitstreams | 41 |

|          | 4.3                  | Comparing Bitstreams of Routes with <i>fpga_editor</i>          | 42 |

|          | 4.4                  | Simple Example (3 Input AND) for Verification                   | 43 |

|          | 4.5                  | Partial Reconfiguration, Replacing the AND With An XOR Gate     | 43 |

|          | 4.6                  | Automating the Process, Using a Composition File                | 44 |

|          | 4.7                  | Conclusion                                                      | 47 |

| <b>5</b> | Con                  | clusions and Recommendations                                    | 49 |

|          | 5.1                  | Conclusions                                                     | 49 |

|          | 5.2                  | Main Conclusions                                                | 50 |

|          | 5.3                  | Future Work                                                     | 51 |

|          |                      | 5.3.1 Bitstream Generation in Hardware                          | 51 |

|          |                      | 5.3.2 Reduction of Reconfiguration Time                         | 52 |

|          |                      | 5.3.3 Routing                                                   | 53 |

|          |                      | 5.3.4 Network on Chip                                           | 53 |

|          |                      | 5.3.5 System Integration                                        | 54 |

| Bi       | ibliog               | raphy                                                           | 57 |

#### Bibliography

| 2.1 | XC2VP7 structures scaled to size in bit-stream                             | 14 |

|-----|----------------------------------------------------------------------------|----|

| 2.2 | Virtex-II Pro Slice configuration                                          | 15 |

| 2.3 | CLB as seen in fpga_editor                                                 | 16 |

| 2.4 | Virtex-II Pro wires as taken from the datasheet                            | 17 |

| 2.5 | Virtex-II Pro clock distribution as taken from the user-guide              | 18 |

| 2.6 | ISE design flow                                                            | 18 |

| 2.7 | XAPP290 vertically stretching modules                                      | 20 |

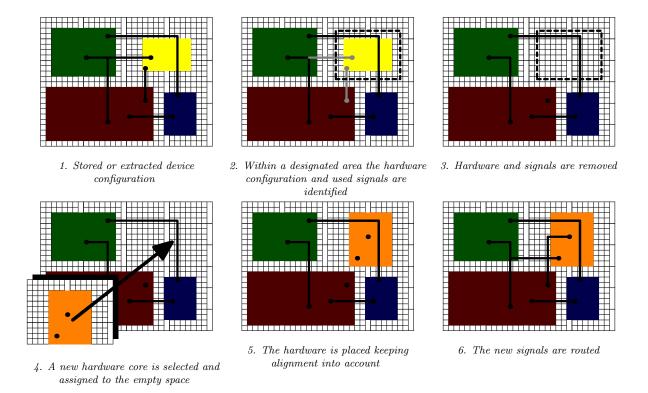

| 2.8 | Exchanging one hardware core for another                                   | 22 |

| 3.1 | Virtex-II Pro wires as shown in fpga_editor                                | 29 |

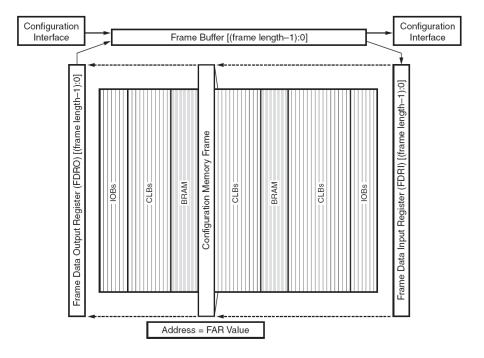

| 3.2 | Virtex frame buffer                                                        | 30 |

| 3.3 | Text representation of a bit file partially reconfiguring the 5th frame of |    |

|     | the first column                                                           | 31 |

| 3.4 | Hexadecimal count of bit occurrence in the frames of a CLB                 | 33 |

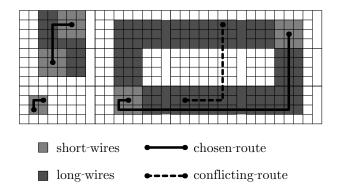

| 3.5 | A simple implementation for routing 2 points                               | 34 |

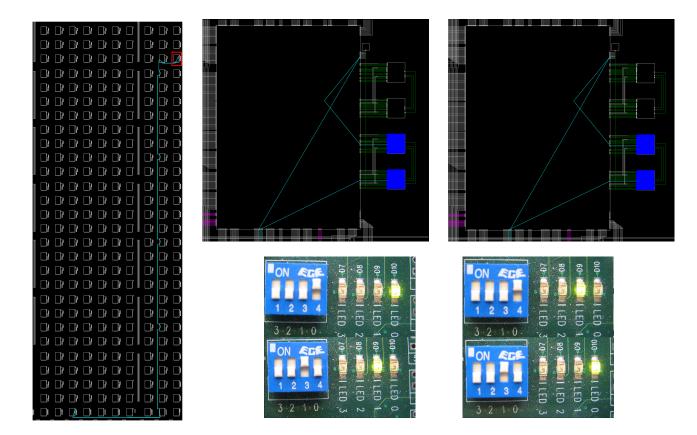

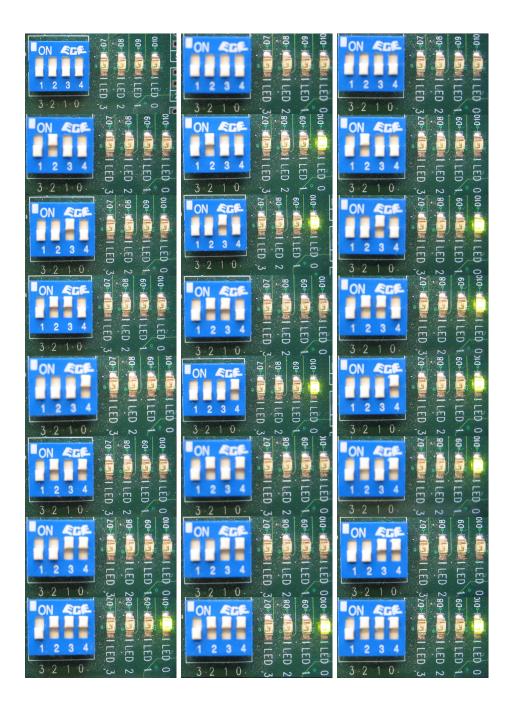

| 4.1 | Routing two switches to two LEDs and reversing the connections             | 42 |

| 4.2 | AND-Routing by ISE (left), our router (middle) and XOR-routing (right)     | 44 |

| 4.3 | Device composition input file                                              | 45 |

| 4.4 | logic functions of 3 input AND, XOR and a combination                      | 46 |

|     |                                                                            |    |

I would like to acknowledge my parents, brother, sister in law, fellow governing board members of O.J.V. de Koornbeurs 2005-2006, everybody at CE and all my friends for their support, and for suffering me as a student for way too long.

1

A modern computer system consists of various separate components with a specific function. Even novice computer users should know that the processor is the most important part that governs almost all the operations within the computer system. Many functionalities are integrated on the main board these days, but it is still possible to choose a vast array of extras, for instance: a fast graphics card, or two of them, network cards of different quality and speeds, or special hardware RAID cards for fast and big storage capacity on multiple disks. When the need arises for a new system to be assembled, there are many of choices to be made. Just for a normal IBM compatible (x86) system there are processors available from several manufacturers. Although they will all run normal software, some will have additional multimedia instructions, or 64-bit support, or multiple cores. Having fixed hardware has its disadvantages:

- Chances are that the main processor will not be replaced during the life time of the computer system, so the user will be locked into the technology picked.

- If a new hardware feature becomes available, it is impossible to reap the benefits of it unless you buy this new hardware for your system.

- By now, we are used to update our software on a regular basis. It would be desirable to have this option for our hardware as well. Of course it is always possible to change the graphics card or the processor, but most of the time the user will have to do without these new features until it is time to purchase a new system.

The ability to update hardware just as easily as software will is quickly becoming a reality. Field-programmable gate arrays (FPGAs) are chips that contain programmable hardware. This means that the off-the-shelf component has no functionality what so ever, but using the hardware description of for instance a microprocessor it can be configured to become that microprocessor. It could just as well be configured to become a video processor or a hard disk controller. Until now, FPGAs are used mainly for prototyping and products with relatively small production numbers. However, more applications for their use are being found. The C-one reconfigurable computer [11] is a project in which the Commodore 64, a popular home computer from the 80's, is emulated by an FPGA. The same board can also be used to emulate a Amstrad/Schneider CPC46. Similar projects exist for a number of different home computers which where popular in that period.

Modern computers are too complex to fit inside an FPGA. An implementation would take up approximately 10 times more space and would be 3 times as slow, as compared to a specifically designed chip (ASIC) [6]. However, there are significant advantages of having a general-purpose processor augmented with an FPGA:

- It is possible to implement common operations on these kinds of chips.

- This can alleviate the main processor of computationally extensive tasks.

- A hardware implementation on an FPGA is usually faster than software because it can make more efficient use of the chip resources and it can make better use of parallelism.

- One of the major advantages is that a new algorithm or new standard does not mean there is a need for new hardware, just a new hardware description.

The Computer Engineering laboratory has implemented several algorithms in hardware. For MPEG4, AES encryption/decryption and VOIP applications we have developed hardware accelerators. Imagine a user watching a film over an encrypted connection. Suddenly, his Internet phone rings. He pauses the film and picks up the phone, which sets up a secured connection for the conversation. As we have a hardware description for AES, the decoding of the film and the VOIP implementation, the computer can perform all operations efficiently. Suppose the FPGA is not large enough to hold all three hardware implementations. As both applications use encryption/decryption, the AES hardware has to remain configured. Luckily the film has been paused. This means the MPEG4 decoder can be temporarily replaced with the VOIP hardware. The FPGA can reconfigure one part of its structure while the rest of the system remains in operation. This is called dynamic partial reconfiguration (DPR). It is, therefore, possible to replace the MPEG4 decoder with the VOIP hardware while the AES encryption/decryption remains in use. The user is of course oblivious to all the processes involved.

The research field of using reconfigurable hardware to augment a computer system is called reconfigurable computing (RC). It can be expected that this technology will first manifest itself in embedded devices. For the user it will not be apparent that an HD-DVD or Blue-Ray player will contain an FPGA. It is not unlikely that future codecs, with which the films are stored onto the disk, will change over time. The advantage for the consumer is that they will not need to replace their hardware as often while they can reap the benefits of new developments. Manufacturers can update their hardware to the new standard when needed. Whether this technology will make it to desktop systems is an open issue.

## 1.1 Reconfigurable Computing

In the early 60's, there was an interest to look beyond the conventional general-purpose machines and to develop new computing paradigms. As a result, reconfigurable computing was conceived [12] as a means to extend the capabilities of general-purpose computing. In reconfigurable computing, parts of a program can be described in hardware, which can result in several hardware implementations for different stages of execution of a single program. Consequently, during program execution the processor has to reconfigure the hardware to the needed functionality. However, technology in the 60's was not mature enough to sufficiently implement the concept of reconfigurable computing. With the introduction of programmable logic devices in 1984 and field-programmable gate arrays (FPGA) in later years, reconfigurable computing became increasingly more accessible.

When using an FPGA for reconfigurable computing, this is referred to as fine-grained reconfigurable computing. This means for instance that the FPGA is made up of small lookup tables which take only a few bits as input to produce single-bit results. All signals are individually routed through the chip. The advantage is that the hardware description can be meticulously tuned to the algorithm, but this comes at a disadvantage. The reconfiguration data is very large, which implies that reconfiguration will take a relatively large amount of time. It also implies that functional densities are low, which adds delay to the signal paths as they have to travel longer distances and can pass through multiple switches. Most FPGAs have additional functional units like multipliers and small RAMs, which are beneficial to many applications to improve their performance. In course-grained reconfigurable computing [14], the smallest structures rarely operate on data pathways with less that 4 bits. Architectures vary extensively, but they have in common that signals are routed through buses instead of individually. Operations on the data can be performed by anything from programmable arithmetic and logic units (ALUs) to small 'processor' cores. This simplifies routing as the number of pathways are greatly reduced, but it means the algorithm has to be mapped onto an existing structure instead of a freely chosen one. It also means that there are a lot less configuration bits, which is advantageous for reconfiguration times. Some architectures are running on specially fabricated chips, others only exist in an emulator. Development for these architectures can therefore be expensive. We will only be targeting fine-grained reconfigurable computing as we primarily have access to this type of technology.

# **1.2** Field-programmable gate arrays

FPGAs are integrated circuits composed of programmable logic interconnected with programmable networks. This allows for the construction of any digital circuit. Compared to ASICs, FPGAs can be a cost effective replacement if used in relatively small quantities (less then approximately a thousand to ten thousand units). FPGAs have found their way into commercial products, often because they ensure a quicker time to market or improved flexibility. With firmware updates, incorporated FPGAs make it possible to correct small design errors in the hardware during or after production. They can take over signal processing functions from DSPs and are bridging the gap between generalpurpose microprocessors or microcontrollers and ASICs. These are all applications in which the FPGA has a fixed function, the configuration of the FPGA is rarely updated during the lifetime of the device.

To most people (including most computer engineers), normal digital chips are composed of standard building blocks, like: logic gates, RAM cells, flip-flops, etc. In a full custom design, these building blocks are freely placeable on the chip. The designers have full flexibility, but this comes at the price of high production costs, as placing the structures on the chip requires many production steps. This technology is only attractive when a large number of the same chip are produced. A cheaper alternative are sea-of-gate chips, which are entirely composed of these standard building blocks, or even just transistors. This reduces the production costs significantly because these gates only need to be connected with a few metal layers. The disadvantage is that the design has to be mapped on to the pre-placed components. As a consequence not all components are being used because it would be impractical, impossible, or too expensive to wire them up. These chips will therefore be larger and slower than a full custom version, but they would be cheaper to design and produce.

Field-programmable gate arrays are composed of standard building blocks, like: flipflops, multipliers or RAMs, and programmable building blocks in the form of lookup tables and multiplexors. Where a designer would use an AND and an XOR gate to make a half adder, in the FPGA lookup tables are set to represent this AND or an XOR gate. It basically means the component is represented by its logic table. The lookup tables take multiple inputs and , therefore, can represent more then a single gate. It would be possible to build an FPGA just out of lookup tables, but by adding a few extra elements like flip-flops, the functional densities and speed greatly improve. These various elements are usually combined in a regular structure, that Xilinx for instance calls slices. To route the signals in the FPGA, switching elements of various composition are used. This mostly depends on the delay they cause. The critical pathways in a design need to have the fastest connections. For this reason, there are special pathways for carry, clock, and global signals. Carry signals use small switches directly connecting to neighboring slices. Clock and global signals are routed through a fixed network from the center of the chip outwards. This is to minimize clock-skew. Normal signals are routed through switch matrices which connect to wires of varying lengths. These can route the signal to neighboring resources, resources in the vicinity or to chip-spanning wires. As the switches are connected to hundreds of wires it would become too complex a structure if it could connect every wire to the other. Usually the pathways a signal can take are limited.

All these switches and lookup tables are combined with RAMs to contain their configuration information. The FPGA is made of regular tiles containing switches, lookup tables, and their configuration memories. In Xilinx terminology, these are called complex logic blocks (CLBs). The manner the configuration memory can be accessed depends on the implementation. Some devices, like the Atmel 94k series [1], allow for byte-sized access to the memory. Others, like the Xilinx Virtex series [34], use frames which can be much larger (+/-500-1500 bits). Sometimes memory can be written directly, or it has to be configured serially by moving the data through a large shift register. The speed and granularity of the device configuration is a major factor in successfully implementing reconfigurable computing. Some devices can only be configured in their entirety. This usually involves shutting down the device, rendering it useless for the time it is being reconfigured. The delay caused by reconfiguring the device can be seconds, which is substantial for a computer systems which can perform several billion operations each second. Some FPGAs facilitate a way to reconfigure only a part of the device. In this way the rest of the device can remain in use while a small portion is set up for the new functionality. This is used for runtime partial reconfiguration in reconfigurable computing. The advantage is that reconfiguration delays can be hidden as long as the new functionality is being set up long before it will be in use. Other functions will remain accessible to the computational process. The reconfiguration time is also reduced as the size of the reconfiguration bitstream is related to the size of the structure which is being reconfigured. As we only reconfigure a small portion of the chip, the bitstream size will be much smaller than for reconfiguring the entire device.

## **1.3** Problem Statement

When reconfiguring an FPGA for a new function, we encounter two problems:

• Changing functionality of the device suffers from lengthy reconfiguration latencies.

Configuring an entire device can take a tenth of a second to several seconds. One solution is to *partially* reconfigure the device, replacing only a small portion of the reconfiguration data to change a functionality or just some parameters. This reduces the reconfiguration time and can increase functional densities for some applications [13]. It can also be used to hide reconfiguration latencies by setting up the next hardware accelerator while the other accelerators are in use.

• For each device within a family and each combination of hardware, a new reconfiguration bitstream has to be synthesized.

Normally, each device type, even within a family, needs a different reconfiguration bit stream. Current methodologies for generating partial reconfiguration bitstreams entail using an ad-hoc manner for generating full device configuration of each device and module combination, and extracting the differences at compile time [16]. It is a cumbersome method to distribute an application, especially when multiple cores are used and interchanged, and comes with considerable restrictions:

- Synthesis of device configuration is done in compile time

- Existing methods use fixed floorplans

- Existing methods use bus macros to affix routing

- Existing methods can not place arbitrarily sized modules

# 1.4 Goal and Methodology

In this thesis, we introduce a solution to overcome these problems. This research is focused on developing a method that enables (semi-)arbitrary removal and placement of hardware implementations, and if needed, perform the necessary routing to disconnect and connect them to other implementations present in the device. It produces full and partial (re)configuration bitstreams for first time setup and subsequent transitions.

Our goal is to show that it is possible to replace a hardware core with another one by manipulating only the bit streams. We perform operations on the bit streams only because we want to avoid lengthy synthesis cycles. To achieve this result we take the following steps:

• We propose a design flow and implementation to replace one hardware module for another

- We limit our work to the resources and wiring which are of most interest

- Simple tools are made for manipulating the bitstream with the information obtained

- Tools for isolation of hardware cores, placement and routing are developed

- A framework is build to automate the removal, placement and routing of various hardware cores.

Our method has several advantages over existing methods:

- It no longer reserves module specific space on FPGA.

- Does not reserve routing paths.

- Does not make prerequisites for the size or shape of the module.

- Does not use bus macros, thereby using less resources.

- Can do free placement as long as the module structure matches the underlying FPGA resources.

- Can route through existing structures.

- Can place modules on top of existing routing if there is no conflicting use of wires.

The advantage of our solution is we no longer reserve a specific area for the modules, nor do we make use of reserved routing paths. This means we can truly arbitrarily place and connect any module to any other module. We do not make use of bus macros, nor do we place any restriction on the size and shape of the modules, although they do have to fit on to the device without causing conflicts with the existing configuration. As long as the router can generate a pathway, routing can go through existing structures. As long as existing pathways do not conflict with the routing within a new module, modules can be placed on top of existing routing. We can do 2d placement, enabling more efficient area usage and routing densities are only limited by the available resources on the FPGA. Although the developed techniques are intended for on-line bitstream generation, the Achilles heel is in the computation required for doing routing.

# 1.5 CE Research in Reconfigurable Computing

Without much doubt, the utilization of reconfigurable hardware adds flexibility and performance, mainly due to the exploitation of parallelism in hardware. This has been proven as the reconfigurable hardware can outperform general-purpose computing for a wide range of algorithms and in some cases by a large margin [29]. It is therefore desirable to exploit this advantage to accelerate general-purpose computing. Currently, this is done in an ad-hoc fashion, where specifically designed hardware cores are implemented for each application. This methodology is very much dependent on the platform it targets and is impractical for most software developers. The computer engineering (CE) laboratory is working on various projects to change this.

#### 1.5.1 Delft Workbench

The Delft workbench project [9] strives to develop a semi-automatic platform for integrated hardware/software co-design, targeting heterogeneous computing systems containing reconfigurable components. We are developing an integrated environment to make it possible for a 'software' developer to implement applications on a reconfigurable platform. The process of designing an application not only involves producing a functional implementation, but also entails the identification of the components which will have the most potential to improve overall execution time, by translating them into hardware. The workbench helps to identify these components and also helps the designer with the translation process, in which a sequential algorithm has to be rewritten to make use of the parallelism (hArtes project). This is inherent to a hardware implementation. It is possible to just use library components to accelerate the application with hardware. In achieving the best results in optimizing an application it is important that the developer has knowledge of hardware design, however the group is developing a compiler that will translate C into a hardware description (MORPHEUS project). This will offer the designer the ability to find the best trade-off between development time and application acceleration, which is done by choosing one of these three methods for the implementation. Because of the close coupling between the general-purpose processor and the FPGA, there are delays caused by reconfiguring the FPGA. A retargetable compiler will have to take care of this issue (RCOSY project), by issuing the reconfiguration process as soon as possible. The target platform of the Delft workbench is the Molen reconfigurable processor.

#### 1.5.2 Molen

The Molen architecture [28] is a combination of a general-purpose processor (GPP) and a reconfigurable processor (RP). This is an architecture in which there is a close relation between software running on the general-purpose processor, and the hardware implementations in the FPGA which are meant to accelerate the application. It extends the instruction set of the GPP with four to seven instructions to add reconfigurable functionality. The instructions encompass the configuration of the RP, the execution of the configured functions, the exchange of data between the GPP and the RP and synchronization between the two.

This research focuses on the replacement of one hardware configuration by another on an FPGA. The platform we focus on is the Virtex-II Pro, which is a common FPGA that has (among other features) two PowerPC processors on chip. For this platform we have an implementation of the MOLEN reconfigurable microcoded processor. We can utilize our results for an implementation of the 'set' instruction, which initializes the RP for a new function.

## 1.6 Overview

This thesis is organized as follows. Chapter 2 describes what runtime reconfiguration is, explains our methods and presents related work. In Chapter 3, we discuss the assump-

tions made and the methodology followed to arrive at our implementation and the tools we developed for this. Chapter 4, we give examples to demonstrate how our methodology evolved and to show that it works. Finally, in Chapter 5 we draw some conclusions and give recommendations on how to proceed from here. In this section we will present related work by others, and compare them with our own. Because the only practical design flow up for partial reconfiguration until now has been XAPP290, and we have developed a new way to do this, we will mainly focus on different forms of connectivity between hardware implementations on an FPGA and the way this can be improved by our methods. The related work will show:

- Connectivity can be split up into direct circuit switched, logically circuit switched and network-on-chip.

- Placement can be 1 Dimensional or 2 Dimensional.

- The area for the placed hardware is fixed, slot based, or has significant restrictions.

- The module sizes are often predetermined and modifications to these require changes to the floor planning at different levels in the design.

- All forms of partial reconfiguration are using bus macros to affix routing to specific locations.

- All implementations use the Xilinx tools to generate the bitstreams and require resynthesizing a project at compile time for each modification.

Although many authors are focused on implementing networks on chip, they need (partial) reconfiguration to produce and modify these. Our methods will present a more dynamic approach to partial reconfiguration. We propose a method that:

- Will perform partial reconfiguration in a way that can be applicable to any form of connectivity and hardware implementation.

- It should do away with bus macros as they are a waste of resources.

- It should pose the minimum amount of restrictions on modules size, shape and the position it can be located at.

- Placement of hardware should be 2 dimensional.

- It should generate partial reconfiguration bitstreams without the use of the Xilinx tools, to enable migration of device reconfiguration to runtime instead of compile time.

- The partial reconfiguration has to be dynamic in order to hide reconfiguration delay.

- The method should be implementable on existing reconfigurable platforms, like the Molen platform.

- The implementation has to be incorporated into a design flows for application on future projects.

In this chapter we will also provide an overview of the normal design flow for partial reconfiguration, we will propose a modified version for our own implementation and we provide an overview of the known information of the targeted FPGA device.

# 2.1 Related Work

The result of the work done for this thesis is a method for placing and connecting modules onto a Virtex-II Pro. If needed old modules are removed to replace one hardware implementation for another. This is done dynamically using partial reconfiguration to hide reconfiguration delay. The normal method for placement is 1 dimensional, but there has been some research on 2 dimensional placement for this family of devices. 1 Dimensional placement, using vertical slots, is the most practical implementation, but it wastes a lot of space. 2 Dimensional placement, as we propose to do, is superior in efficient use of area [27]. The method chosen in this thesis for connecting the modules is a direct connection, also know as direct circuit-switched. Other methods are logical circuit-switched and network on chip. Network-on-chips are packet switched networks. Direct circuit switched networks have the least communication delay, as they are short unbuffered connections, but they can be considered static networks. For pathways that are not static, but do not change frequently, logical circuit switched networks are a good alternative to packet switched networks. In logic circuits-switched networks, pathways are negotiated before use, setting various switch nodes to form a direct link between modules. Networks on chip (NoC) are packet switched networks, which buffer the packets between each router, and can therefore be clocked higher as distances between routers are shorter compared to direct connections. They do however take up a lot of resources due to their complexity. In the next section we present work by others related to these subjects.

#### 2.1.1 1 Dimensional Placement, Mostly circuit switched

In Bieser, *et al* [3] the modules are fixed in dimensions and stretch the height of the device. The modules are proposed to be IP-Cores which have been tested thoroughly and can be used as standard building blocks. The routing problem is overcome by using a shared bus to which the modules attach. This bus makes use of the tri-state drivers that are in the Virtex-II. This means that only one module at a time can make use of the bus. The designer can merge the module bitstream with the configuration bitstream using an application based on JBITS [31]. It is possible to create user defined IPs.

JBITS development has been stopped, there is no support for newer device families like the Virtex-II Pro. Our implementation could isolate the various modules created into separate snippets of bitstreams. As there is a fixed bus to connect to, no routing is necessary. We can produce the bitstreams that dynamically remove and place these modules at runtime. Taking device restrictions into account it can be possible to modify this implementation to do 2 dimensional placement. Although we refrain from exploring the use of the tri-state bus structures, it may be possible to extend our methods to make use of these and reroute them dynamically. Other network topologies are advisable as communication can only be with one module at a time.

Bobda, et al [5] have proposed two methods for exchanging signals between modules, also using partial reconfiguration. One is based on 1 dimensional vertical-slot shaped reconfigurable modules which are connected using a reconfigurable multiple bus (RMB) , similar to the one suggested by ElGindy [10]. This RMB uses logical circuit-switched routing in the form of a standard switch matrix for each module, with a controller added to perform worm-hole routing. The established link can transfer data from source to destination each clock cycle.

This might be the best trade-off between design complexity and the computationally intensive approach we take with respect to routing the signals, though direct circuitswitched networks have a little less delay. The RMB could be substituted by dynamically reconfigured direct circuit switched networks, using our implementation. This can only be successful if connections do not need frequent reconfiguration. As with Bieser, *et al*, our methods could perform device reconfiguration for this implementation because this is also a slot-based implementation, though using a different type of bus. The bus in question can enable multiple modules to communicate to each other. Extending our methods, the interfaces can be dynamically added or removed and could be modified to do 2 dimensional placement. The second approach is discussed later on.

Karsteva, *et al* [20] propose how to relocate part of the bitstream for 2d placement, although this information is easily deduced from the user guide. They have only implemented a 1 dimensional method of placement and have information on the execution time for merging bitstreams and producing the partial bitstream for reconfiguring the device functionality.

This is interesting, as we do not focus on execution time for this research, but it is a major factor limiting practical implementation of our method. The use of perl-scripts and the intermediate steps we take makes it impractical to compare our work with this, as our approach is obviously much slower than an C implementation.

#### 2.1.2 2D Placement, Mostly Network-on-Chip

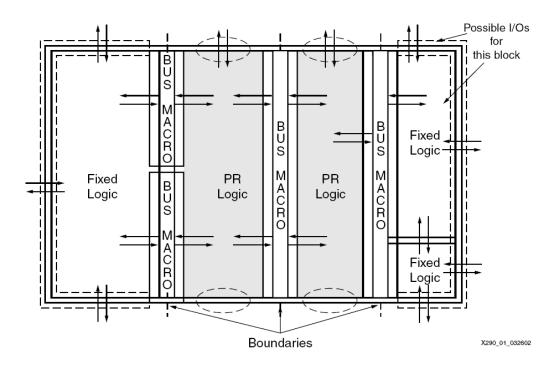

Sedcole, *et al* [25] proposed a method for reconfiguring hardware cores, in the form of modules, that is more flexible than described in the Xilinx application notes [33]. They provided a way to place hardware cores above each other, whereas the Xilinx method dictates that modules stretch the entire height of the device. The positions and size for these hardware cores have been predetermined. The issue with static routes passing through the modules, were resolved by reserving the long lines as pass through regions in the modules. Signals are connected to static routing through bus macros. The operations necessary are performed at a bitstream level with the use of stored configuration data of the modules.

As the bus and connectivity for the modules is static, no routing has to be done. Due to the fixed module size however it is inefficient with the usage of the available space. By reserving signals for pass-through routing this reduces the effective number of available wires within a module. It could therefore result in larger modules, operating with longer wires which have more delay. Our methods will do 2 dimensional placement without reserving space for it, nor will there be any restrictions on the shape and size of the modules as long as they fit.

Hübner, et al [17] implemented online routing using regular routing structures which stretch vertically through the device. A module can be attached to the structure at any location. In this manner, they provide arbitrary 2D placement of modules of any size, as long as they do not conflict with the routing structures, vertically interrupting the FPGA configuration regularly. The routing structures are lookup table based and have to be reconfigured at the the position it attaches to the module. The number of signals that pass through the structure is limited, due to the use of lookup tables. The operations are performed by a C program running on the PowerPC or Microblaze processor using stored configuration data for the routing structures and modules.

The use of lookup tables adds delay to the routing as the signals pass through quite a few lookup tables, which is not the case for our directly connecting method. The routing pathways are configured statically and in advance, hence the length of the pathways is longer. Its implementation appears to have slot-based modules which are slaves to a single master controlling this bus structure, indicating that there is no communication between modules. This is different for their network-on-chip based approach, which is more complex. Their lookup table based method could be considered a reconfigurable logical circuit switched network. The modules have restrictions as they may not conflict with the routing structures. This implementation comes closest to the goals we want to achieve. It does not provide the highest degree of freedom in using the device resources and still poses restrictions on the modules and has restricted communication capabilities.

Möller, et al [23] use a modified Hermes network on chip, named Artemis and bus macro like structures to provide for dynamic reconfiguration of the cores attached to the router. The routers themselves are part of a fixed network. The reconfiguration support is added with custom macros which can block signals going through while the modules are being reconfigured. This stops possible transients caused by the reconfiguration process from entering the network. They resemble the standard lookup table bus macros used in the Xilinx method. The method for positioning the modules is stated to be slow, although it was implemented in C. As we are not focusing on reducing the time to calculate and reconfigure the device our implementation will not be faster. The modules have the appearance to be placed in two dimensions, but it may be a clever way to hide 1 dimensional slot-based placement. Our method can reconfigure both modules and the network implementation freely, although the suppression of transients caused by reconfiguration have to be addressed by the designer, incorporating an extra and-gate to block signals during the reconfiguration phase.

For the second part of their Journal paper, Bobda, *et al* [5] assume an FPGA that is capable of 2d placement, and have build a network on chip that can cope with routing packets, even though the structure of the network is irregular. They avoid creating obstacles by surrounding each module with a network ring. In this way packets can always get around modules, no part of the network gets cut off by placing a module at a certain location. They show that their routing algorithm is probably deadlock-free. They only show how this would work for a static configurations, but are working on an implementation that can handle changing the network configurations. Their use of JBITS means they can only implement this on older FPGAs. Because their implementation is mostly based on placing modules within an existing routing mesh, the routing problem has been transfered to the packet routers. As the interfaces are standardized and connected automatically by placing the modules at the correct position. Using a more dynamic network, it might be possible to reduce the number of routers using our methods, as the networks surrounding the modules can be adapted to the existing structures. This would greatly improve on the available resources for the modules themselves, because the routers takes up a lot of resources.

Hilton and Nelson [15] describe a circuit switched network called a programmable network on chip (PNoC) without going into the specifics of the reconfiguration process, though they have an implementation for the XC2VP30. They propose logical circuit switched routers that can handle dynamically changing networks by performing updates on the routing tables when a change in network occurs. They supply various topologies for the network as an example, which suggest they do 2 dimensional placement, but as they focus on the network and not the reconfiguration they only specify the number of slices and block-rams their router takes up. Because not much information is given on their implementation except for a desire to apply their network to dynamic module replacement as it was designed for this purpose. Their current demonstration application is a static network. Our methods would be well suited as it can deal with varying shapes and sizes of modules, coping with multiple consecutive substitutions without the hindrance of a predetermined floor plan.

# 2.2 Xilinx Virtex-II Pro

Although reconfigurable computing is not a new field, only in the last fifteen years have we had the opportunity to explore its potential. The technology is showing promise, but there are still quite a few hurtles to take. One of the problems is caused by the time it takes to set up the reconfigurable processor (RP) to do a new task. Although a hardware implementation can be much faster than the equivalent in software, this advantage is counteracted by time it takes to reconfigure the device, especially compared to the cycles that the general purpose processor has available in the same interval. Runtime partial reconfiguration is important for reducing and hiding the delay of reconfiguring for a new task before it can be used. First we have to look at the reconfiguration process, taking into account the device we have chosen.

Because reconfiguration bitstream are specific to a device family, we prefer to choose an accessible common FPGA to work on. Therefore, we chose to target the Xilinx Virtex-II Pro family. It is in common use, can do partial reconfiguration and the Xilinx university program board [18] has an attractive price tag. It has an XC2VP30 as its main device, offering 2 power PC cores 30k+ logic cells 136 multipliers and 428kBit of RAM. Most importantly, there is an implementation of the Molen processor for it.

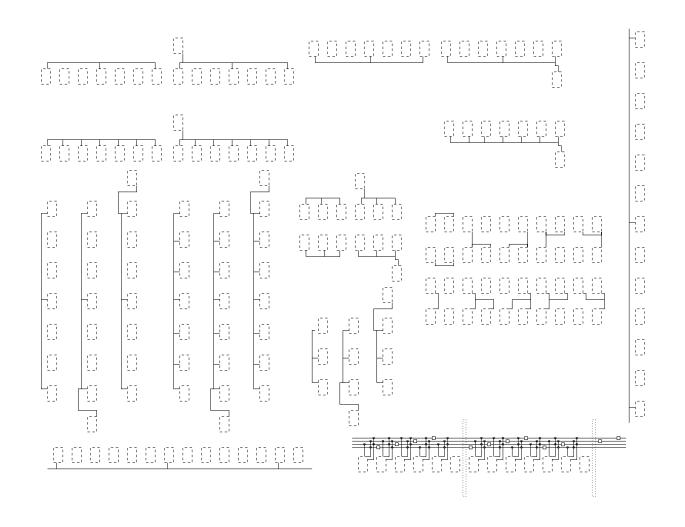

Figure 2.1 depicts the arrangement of resources in the XC2VP7, scaled to the number of bits they use in the bitstream. The most common resource is the complex logic block (CLB). These logic blocks contain a portion of the hardware description and use

| 16<br>80                                       | IOB IOB<br>IOI IOI            | DCM<br>DCMI       |      | IOB<br>IOI | IOB<br>IOI | IOB<br>IOI | IOB<br>IOI | IOB<br>IOI | IOB<br>IOI | RII        |          | IOB<br>IOI | IOB<br>IOI | IOB<br>IOI | IOB<br>IOI | IOB<br>IOI | IOB<br>IOI | RII        |          | IOB<br>IOI | IOB<br>IOI | IOB<br>IOI | IOB<br>IOI | IOB<br>IOI        | IOB<br>IOI | DCM<br>DCMI |      |                   |            | BSCAN<br>TAGFPC    |       |       |

|------------------------------------------------|-------------------------------|-------------------|------|------------|------------|------------|------------|------------|------------|------------|----------|------------|------------|------------|------------|------------|------------|------------|----------|------------|------------|------------|------------|-------------------|------------|-------------|------|-------------------|------------|--------------------|-------|-------|

| 🛱 101                                          | CLB CLB                       | BRI               |      | CLB        | CLB        | CLB        | CLB        | CLB        | CLB        | RII        |          | CLB        | CLB        | CLB        | CLB        | CLB        |            | RII        |          | CLB        | CLB        | CLB        |            | CLB               | CLB        | BRI         |      |                   |            | 101 📱              |       |       |

| б<br>Ю                                         | CLB CLB                       | BRI               | BRAM |            | CLB        | CLB        | CLB        | CLB        | CLB        | CLB        | RII      | RocketIO   | CLB        | CLB        | CLB        | CLB        | CLB        |            | RII      | RocketIO   | CLB        | CLB        | CLB        |                   | CLB        | CLB         | BRI  |                   |            |                    | 101 2 |       |

| ш<br>Ш<br>ог                                   | CLB CLB                       | BRI               |      | CLB        | CLB        | CLB        | CLB        | CLB        | CLB        | RII        |          | CLB        | CLB CLB    | CLB        | CLB        |            | RII        |            | CLB      | CLB        | CLB        | CLB        | CLB        | CLB               | BRI        | BRAM        |      |                   | 101 🖉      |                    |       |       |

| о<br>Э́                                        | CLB CLB                       | BRI               |      | CLB        | CLB        | CLB        | CLB        | CLB        | CLB        | RII        |          | CLB        | CLB        | CLB        | CLB        | CLB        |            | RII        |          | CLB        | CLB        | CLB        | CLB        | CLB               | CLB        | BRI         |      | CLB               | CLB        | 101 📱              |       |       |

| б<br>Ш юі                                      | CLB CLB                       | BRI               |      | CLB        | CLB        | CLB        | CLB        | CLB        | CLB        | BRI        |          | CLB        | CLB        | CLB        | CLB        | CLB        | CLB        | BRI        |          | CLB        | CLB        | CLB        | CLB        | CLB               | CLB        | BRI         |      | CLB               | CLB        | 101 🛱              |       |       |

| б<br>Ш юі                                      | CLB CLB                       | BRI               |      | CLB        | CLB        | CLB        | CLB        | CLB        | CLB        | BRI        |          | CLB        | CLB        | CLB        | CLB        | CLB        | CLB        | BRI        |          | CLB        | CLB        | CLB        | CLB        | CLB               | CLB        | BRI         |      | CLB               | CLB        | 101 🛱              |       |       |

| б<br>ЮІ                                        | CLB CLB                       | BRI               | BRAM | CLB        | CLB        | CLB        | CLB        | CLB        | CLB        | BRI        | BRAM     | CLB        | CLB        | CLB        | CLB        | CLB        | CLB        | BRI        | BRAM     | CLB        | CLB        | CLB        | CLB        | CLB               | CLB        | BRI         | BRAM | CLB               | CLB        | IOI 🖉              |       |       |

| і<br>Б<br>Іоі                                  | CLB CLB                       | BRI               |      | CLB        | CLB        | CLB        | CLB        | CLB        | CLB        | BRI        |          | CLB        | CLB        | CLB        | CLB        | CLB        | CLB        | BRI        |          | CLB        | CLB        | CLB        | CLB        | CLB               | CLB        | BRI         |      | CLB               | CLB        | IOI 🖉              |       |       |

| Б юі                                           | CLB CLB                       | BRI               |      | CLB        | CLB        | CLB        | CLB        | CLB        | CLB        | BRI        |          | CLB        | CLB        | CLB        | CLB        | CLB        | CLB        | BRI        |          | CLB        | CLB        | CLB        | CLB        | CLB               | CLB        | BRI         |      | CLB               | CLB        | IOI 员              |       |       |

| 0 IOI                                          | CLB CLB                       | BRI               |      | CLB        | CLB        | CLB        | CLB        | CLB        | CLB        | BRI        |          | CLB        | CLB        | CLB        | CLB        | CLB        | CLB        | BRI        |          | CLB        | CLB        | CLB        | CLB        | CLB               | CLB        | BRI         |      | CLB               | CLB        | IOI 员              |       |       |

| 0 IOI                                          | CLB CLB                       | BRI               | BRAM | CLB        | CLB        | CLB        | CLB        | CLB        | CLB        | BRI        | BRAM     | CLB        | CLB        | CLB        | CLB        | CLB        | CLB        | BRI        | BRAM     | CLB        | CLB        | CLB        | CLB        | CLB               | CLB        | BRI         | BRAM | CLB               | CLB        | IOI 🛱              |       |       |

| б<br>Ю                                         | CLB CLB                       | BRI               |      | CLB        | CLB        | CLB        | CLB        | CLB        | CLB        | BRI        |          | CLB        | CLB        | CLB        | CLB        | CLB        | CLB        | BRI        |          | CLB        | CLB        | CLB        | CLB        | CLB               | CLB        | BRI         |      | CLB               | CLB        | IOI 🛱              |       |       |

| і<br>Б                                         | CLB CLB                       | BRI               |      | CLB        | CLB        | CLB        | CLB        | CLB        | CLB        | BRI        |          | CLB        | CLB        | CLB        | CLB        | CLB        |            |            |          |            |            |            |            |                   |            |             |      |                   | CLB        | IOI 员              |       |       |

| Б юі                                           | CLB CLB                       | BRI               |      | CLB        | CLB        | CLB        | CLB        | CLB        | CLB        | BRI        |          | CLB        | CLB        | CLB        | CLB        | CLB        | 1          |            |          |            |            |            |            |                   |            |             |      |                   | CLB        | IOI 员              |       |       |

| 0 IOI                                          | CLB CLB                       | BRI               | BRAM | CLB        | CLB        | CLB        | CLB        | CLB        | CLB        | BRI        | BRAM     | CLB        | CLB        | CLB        | CLB        | CLB        |            |            |          |            |            |            |            |                   |            |             |      |                   | CLB        | IOI 员              |       |       |

| Б юі                                           | CLB CLB                       | BRI               |      | CLB        | CLB        | CLB        | CLB        | CLB        | CLB        | BRI        |          | CLB        | CLB        | CLB        | CLB        | CLB        |            |            |          |            |            |            |            |                   |            |             |      |                   | CLB        | IOI 员              |       |       |

| IOI B                                          | CLB CLB                       | BRI               |      | CLB        | CLB        | CLB        | CLB        | CLB        | CLB        | BRI        |          | CLB        | CLB        | CLB        | CLB        | CLB        |            |            |          |            |            |            |            |                   |            |             |      |                   | CLB        | IOI Öğ             |       |       |

| о<br>Ю                                         | CLB CLB                       | BRI               |      | CLB        | CLB        | CLB        | CLB        | CLB        | CLB        | BRI        |          | CLB        | CLB        | CLB        | CLB        | CLB        |            |            |          |            |            |            |            |                   |            |             |      |                   | CLB        | IOI 员              |       |       |

| ЮI ЮI                                          | CLB CLB                       | BRI               | BRAM | CLB        | CLB        | CLB        | CLB        | CLB        | CLB        | BRI        | BRAM     | CLB        | CLB        | CLB        | CLB        | CLB        |            |            |          |            |            |            |            |                   |            |             |      |                   | CLB        | юі 🛱               |       |       |

| 0 IOI                                          | CLB CLB                       | BRI               |      | CLB        | CLB        | CLB        | CLB        | CLB        | CLB        | BRI        |          | CLB        | CLB        | CLB        | CLB        | CLB        |            |            |          |            |            | PPC        | 405        |                   |            |             |      |                   | CLB        | IOI 员              |       |       |

| і<br>Эног                                      | CLB CLB                       | BRI               |      | CLB        | CLB        | CLB        | CLB        | CLB        | CLB        | BRI        |          | CLB        | CLB        | CLB        | CLB        | CLB        |            |            |          |            |            |            |            |                   |            |             |      |                   | CLB        | IOI 🛱              |       |       |

| 0 IOI                                          | CLB CLB                       | BRI               | BRAM | CLB        | CLB        | CLB        | CLB        | CLB        | CLB        | BRI        | DDAM     | CLB        | CLB        | CLB        | CLB        | CLB        |            |            |          |            |            |            |            |                   |            |             |      |                   | CLB        | IOI 员              |       |       |

| IOI B                                          | CLB CLB                       | BRI               | DRAM | CLB        | CLB        | CLB        | CLB        | CLB        | CLB        | BRI        | BRAM     | CLB        |          |            |            |            |            |                   |            |             |      |                   |            |                    | CLB   | IOI 0 |

| ioi 🛱                                          | CLB CLB                       | BRI               |      | CLB        | CLB        | CLB        | CLB        | CLB        | CLB        | BRI        |          | CLB        | CLB        | CLB        | CLB        | CLB        |            |            |          |            |            |            |            |                   |            |             |      |                   | CLB        | IOI 员              |       |       |

| 0 IOI                                          | CLB CLB                       | BRI               |      | CLB        | CLB        | CLB        | CLB        | CLB        | CLB        | BRI        |          | CLB        | CLB        | CLB        | CLB        | CLB        | ļ          |            |          |            |            |            |            |                   |            |             |      |                   | CLB        | IOI 🛱              |       |       |

| 0 IOI                                          | CLB CLB                       | BRI               | BRAM | CLB        | CLB        | CLB        | CLB        | CLB        | CLB        | BRI        | BRAM     | CLB        | CLB        | CLB        | CLB        | CLB        | ļ          |            |          |            |            |            |            |                   |            |             |      |                   | CLB        | IOI 员              |       |       |

| б<br>Ш                                         | CLB CLB                       | BRI               |      | CLB        | CLB        | CLB        | CLB        | CLB        | CLB        | BRI        |          | CLB        | CLB        | CLB        | CLB        | CLB        |            |            |          |            |            |            |            |                   |            |             |      |                   |            | IOI D              |       |       |

| б юі                                           | CLB CLB                       | BRI               |      | CLB        | CLB        | CLB        | CLB        | CLB        | CLB        | BRI        |          | CLB        | CLB        | CLB        | CLB        | CLB        |            |            |          |            |            |            |            | _                 |            |             |      | i                 |            | IOI 0              |       |       |

| іоі<br>Ш                                       | CLB CLB                       | BRI               |      | CLB        | CLB        | CLB        | CLB        | CLB        | CLB        | BRI        |          | CLB        | CLB        | CLB        | CLB        | CLB        |            | BRI        |          | CLB        | CLB        | CLB        |            |                   | CLB        | BRI         |      |                   |            | IOI 员              |       |       |

| ioi g                                          | CLB CLB                       | BRI               | BRAM | CLB        | CLB        | CLB        | CLB        | CLB        | CLB        | BRI        | BRAM     | CLB        | CLB        | CLB        | CLB        | CLB        |            | BRI        | BRAM     | CLB        | CLB        | CLB        |            |                   | CLB        | BRI         | BRAM |                   |            | IOI 0              |       |       |

| ioi 🛱                                          | CLB CLB                       | BRI               |      | CLB        | CLB        | CLB        | CLB        | CLB        | CLB        | BRI        |          | CLB        | CLB        | CLB        | CLB        | CLB        |            | BRI        |          | CLB        | CLB        | CLB        | CLB        | CLB               | CLB        | BRI         |      |                   |            | IOI 0              |       |       |

| іол<br>Б                                       | CLB CLB                       | BRI               |      | CLB        | CLB        | CLB        | CLB        | CLB        | CLB        | BRI        |          | CLB        | CLB        | CLB        | CLB        | CLB        |            | BRI        |          | CLB        | CLB        | CLB        |            |                   | CLB        | BRI         |      |                   |            | 101 IG             |       |       |

| 0 IOI<br>0 IOI                                 | CLB CLB                       | BRI<br>BRI        |      | CLB<br>CLB | CLB<br>CLB | CLB<br>CLB | CLB<br>CLB | CLB<br>CLB | CLB<br>CLB | BRI        |          | CLB<br>CLB | CLB<br>CLB | CLB        | CLB<br>CLB | CLB        |            | BRI<br>BRI |          | CLB<br>CLB | CLB<br>CLB | CLB<br>CLB | CLB<br>CLB | CLB<br>CLB        | CLB<br>CLB | BRI<br>BRI  |      |                   |            | IOI IO             |       |       |

|                                                | CLB CLB                       | BRI               | BRAM | CLB        | CLB        | CLB        | CLB        | CLB        | CLB        |            | BRAM     |            | CLB        | CLB        | CLB        | CLB<br>CLB |            |            | BRAM     | CLB        |            | CLB        |            |                   |            | BRI         | BRAM |                   |            | 101 0              |       |       |

|                                                | CLB CLB                       | BRI               |      | CLB        | CLB        | CLB        | CLB        | CLB        | CLB        | BRI        |          | CLB<br>CLB | CLB        | CLB        | CLB        | CLB        |            | BRI<br>BRI |          | CLB        |            | CLB        |            |                   | CLB<br>CLB | BRI         |      |                   |            |                    |       |       |

|                                                | CLB CLB                       | DKI               |      | CLB        | CLB        | CLB        | CLB        | CLB        | CLB        | RII        |          | CLB        | CLB        | CLB        | CLB        | CLB        |            | BRI        |          | CLB        | CLB        | CLB        |            |                   | CLB        | BRI         |      |                   |            |                    |       |       |

| 0 101                                          | CIB CIP                       | BRI               |      | ULD        | ULD.       | CLD        | CLD        | CLD        | CLD        |            |          | CLB        |            | CLB        | CLB        | CLB        |            | RII        |          | CLB        | CLB        | CLB        |            |                   | CLB        | BRI         |      |                   |            |                    |       |       |

|                                                | CLB CLB                       | BRI               |      | CLB        | CLB        | CLB        | CLB        | CLB        | CLB        | RII        |          |            |            |            | 1          | 1          | 1          |            |          | 1 Cmb      |            |            |            |                   |            |             |      |                   |            |                    |       |       |

| і<br>Эші<br>Пог                                | CLB CLB                       | BRI               | BRAM | CLB<br>CLB | CLB<br>CLB | CLB<br>CLB | CLB<br>CLB | CLB<br>CLB | CLB<br>CLB | RII        |          |            |            |            | CLB        | CLB        | CLB        | RП         |          | CLB        | CLB        | CLB        | CLB        |                   |            | BRI         | BRAM |                   |            |                    |       |       |

| IOI go<br>IOI                                  | CLB CLB<br>CLB CLB            | BRI<br>BRI        | BRAM | CLB        | CLB        | CLB        | CLB        | CLB        | CLB        | RII        | RocketIO | CLB        | CLB        | CLB        | CLB        |            |            | RII        | RocketIO | CLB        | CLB        | CLB        |            | CLB               | CLB        | BRI         | BRAM | CLB               | CLB        | IOI 🛱              |       |       |

| і<br>Эші<br>Пог                                | CLB CLB<br>CLB CLB<br>CLB CLB | BRI<br>BRI<br>BRI | BRAM | CLB<br>CLB | CLB<br>CLB | CLB<br>CLB | CLB<br>CLB | CLB<br>CLB | CLB<br>CLB | RII<br>RII | RocketIO | CLB<br>CLB | CLB<br>CLB | CLB<br>CLB | CLB        | CLB        | CLB        | RII        | RocketIO | CLB        | CLB        | CLB        | CLB        | CLB<br>CLB        | CLB<br>CLB | BRI         | BRAM | CLB<br>CLB        | CLB<br>CLB | IOI IGI<br>IOI IGI |       |       |

| 01 <u>00</u><br>101 <u>00</u><br>101 <u>00</u> | CLB CLB<br>CLB CLB            | BRI<br>BRI        | BRAM | CLB        | CLB        | CLB        | CLB        | CLB        | CLB        | RII        | RocketIO | CLB        | CLB        | CLB        | -          |            | CLB<br>IOI |            | RocketIO |            |            |            | CLB<br>IOI | CLB<br>CLB<br>IOI | CLB<br>CLB |             | BRAM | CLB<br>CLB<br>IOI | CLB<br>CLB | IOI IOB<br>IOI IOB |       |       |

Figure 2.1: XC2VP7 structures scaled to size in bit-stream

Figure 2.2: Virtex-II Pro Slice configuration

a switch matrix for routing signals to other resources. Resources like BlockRAMs and RocketIO interfaces are distributed throughout the matrix column-wise at regular intervals. These are connected by BlockRAM interconnections (BRI) and RocketIO interconnections (RII), which are very similar to the switch matrix of the CLB. BlockRAM interconnections also provide connectivity to the multipliers which do not take any reconfiguration data and so do not show up in the bitstream. Around the edges of the device the connection to the outside world is made through IO interconnections (IOI). It can be seen that there is regularity in the distribution of the resources. The most prominent feature is the PowerPC core. Although it seems to take a lot of reconfiguration data, it is highly unlikely that it uses a large portion of this. This indicates the frames are meant to fit the largest reconfiguration-data structures on the device, and that a lot of information is discarded for the sake of uniformity of the bit-stream. For now, we will limit ourselves to the use of CLBs only, although we do take the problems caused by the heterogeneous character of the device into account.

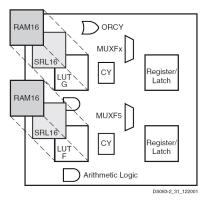

Complex logic blocks (CLBs) are composed out of 4 slices of which a graphic representation is depicted in Figure 2.2 as taken from datasheet [35]. Each slice contains 2 lookup tables, 2 flip-flops, multiplexors and some logic gates. The lookup tables take 4 inputs and produce 1 result, hence taking 16-bits of configuration data. It can represent logic, slice distributed RAM or a shift register. The multiplexors are used to set the slice up to perform specific functions. They can be used to produce larger lookup tables build up out of multiple standard 4-input version. They can also, for instance, be configured to make use of fast carry logic, enabling fast arithmetic functions using incorporated logic gates specifically for these types of functions. As a simple construction element of a larger system, the CLB can perform a great number of tasks.

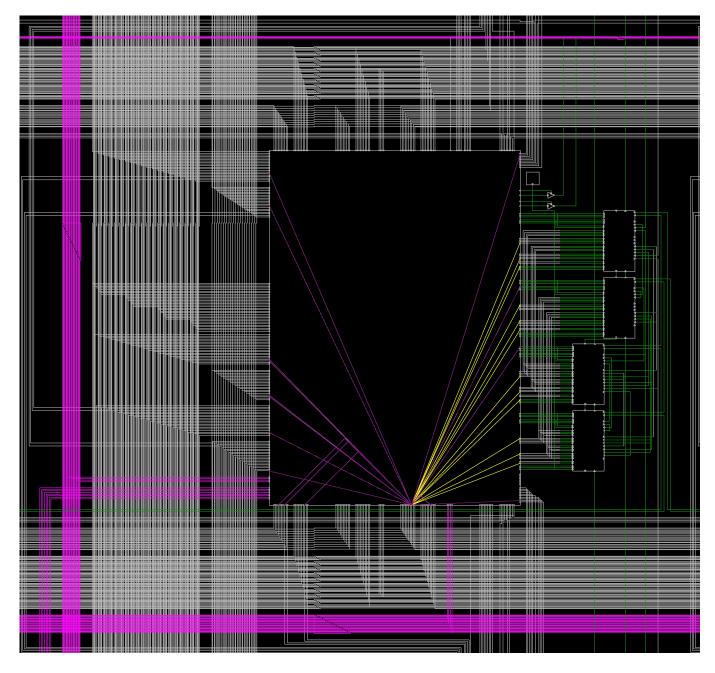

Figure 2.3 depicts a complete CLB as shown by the *fpga\_editor* tool of Xilinx. The 4 smaller squares to the right represent the slices, the large square to the left represents the switch matrix. Most of the wiring for the slices go through the switch matrix, with the exception of the wires forming a carry chain, which are directly liked to neighboring CLB slices. The switches themselves are not fully connected. A single node on the bottom of the switch matrix has been selected. The yellow connections represents possible signal

Figure 2.3: CLB as seen in fpga\_editor

routes leaving the wire. The purple connections represent possible signal routes entering the node. As can be seen, the switch can not connect every node to another, this would become too complex a structure for the large number of nodes that are available.

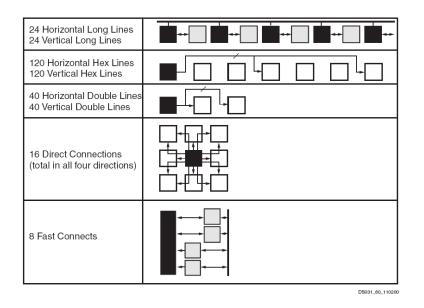

Figure 2.4 depicts the different types of wires connecting the various switch matrices. According to the datasheet, for each switch matrix there are 16 wires connecting to

Figure 2.4: Virtex-II Pro wires as taken from the datasheet

the neighboring resources, 40 wires that connect to the resources which are spaced two and four positions apart and 120 wires that connect to resources spaced six and twelve positions apart. 24 The wires run in horizontal and 24 in vertical directions. These numbers are somewhat polished as they represent the maximum number of wires passing through the CLB, not the number of wires connected to the switch box. In reality, if we only count outgoing signal pathways, they would come to 16 neighboring wires, 40 'double' wires, 40 'hex'-wires, and only 4 vertical and 4 horizontal long lines. This still makes the number of wires available quite formidable.

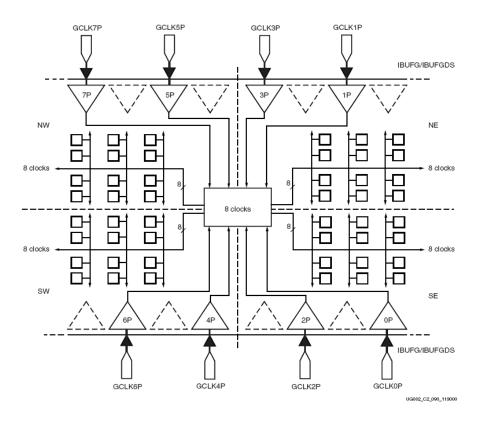

The long lines span the width or height of the entire device. There are also special tristate wires. Most of the wires have only a single driver ensuring signals only travel in one direction, this however is not true for the tristate bus, nor for the long lines. These can be driven from any point, possibly causing damage if a wire is driven from multiple locations. On a device-wide level, there are special wires for distributing clock and global signals throughout the entire device. These run out from the center of the device to the edges, making sure that the delay to each point is approximately the same as is depicted in Figure 2.5, taken from the user-guide. This is to prevent problems with clock skew and to have specific clock regions.

# 2.3 Xilinx Design Flow for static configurations.

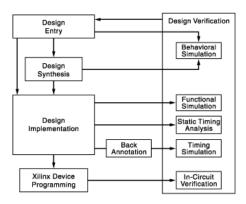

Xilinx provides an integrated development environment (IDE) for programming their devices in various descriptions, including VHDL and Verilog, called ISE. As taken from the ISE help file, Figure 2.6 depicts the normal design flow of the ISE package. This does not include the design flow for partial reconfiguration as explained in application note XAPP290 [33].

Figure 2.5: Virtex-II Pro clock distribution as taken from the user-guide

Figure 2.6: ISE design flow

During the design entry phase, the hardware is described in a high level hardware description language like VHDL or Verilog. It is also possible to design the hardware using a schematic representation, but it is not common. A user constraints file (.ucf) specifies parameters for the entire design process. It allows the user to provide the ISE package with information it can not derive from the high level description. The user can specify constraints on placement, timing and synthesis of the hardware design. Placement

constraints can for instance determine which pins are connected to which signals. Area constraints determine the location to which the hardware implementation is bound. The user can also specify timing constraints to ensure the a critical path meets certain demands for signal delays. Synthesis constraints instruct the synthesis tools to perform specific operations, usually to improve timing or reduce area. If too little information is provided in the constraints file, the software package will try to generate a optimal solution without it. For example, not providing placement constraints on which signals should be connected to which pins, results in the tools assigning a pin by itself. In case the design is only simulated, this may not be a problem. When implementing the hardware description on a device it becomes essential to specify this information.