## **Bachelor of Engineering THESIS**

## **Run-time Partial Re-configuration**

Kees van der Bok

#### Abstract

## **TRIJSWIJK**

Rijswijk Institute of Professional Education Lange Kleiweg 80 2288 GK Rijswijk The Netherlands http://www.thrijswijk.nl/

**FUDDEIFT** Delft University of Technology Faculty of Electrical Engineering, Mathematics and Computer Science Mekelweg 4 2628 CD Delft The Netherlands http://ewi.tudelft.nl/

Computer Engineering Group http://ce.et.tudelft.nl/

MOLEN Research Theme http://ce.et.tudelft.nl/molen/

Run-Time Partial Re-configuration (RPR) enables a FPGA (Field Programable Gate Array) to be partially re-configured during run-time (i.e. part of the array can be over written with another reconfiguration, while the remaining part is active).

An extra ordinary form of RPR is self reconfiguration. In this special case the reconfiguration process is controlled from within the chip. The re-configuration is performed by the static part of the logic, while the dynamic part is reconfigured.

To enable self re-configuration, actually self runtime partial reconfiguration, the target FPGA should feature on-chip access to the re-configuration logic. Furthermore logic has to be designed controlling the re-configuration process (i.e. fetching the re-configuration data and writing it to the reconfiguration logic).

In this thesis a solution enabling self re-configuration is presented. Although the solution is designed for integration in the MOLEN framework it has a broader application range.

The MOLEN framework is a, framework composed of a general purpose processor augmented with a re-configurable processor. The re-configurable processor can be re-configured using the solution presented in this thesis.

Delft, October 9, 2007

## Run-time Partial Re-configuration An Implementation for the MOLEN Framework

#### THESIS

submitted in partial fulfillment of the requirements for the degree of

#### BACHELOR OF ENGINEERING

$\mathrm{in}$

#### ELECTRICAL ENGINEERING

by

Kees van der Bok born in Dirksland, The netherlands

## Acknowledgements

During my thesis work, I received support from many persons. I am thankful towards all those people for there direct help, critical comment on my work and writing, or any other form of support.

There are a few people I want to thank personally. Both my supervisors, Th. Koreneef and A.J. van Genderen. Both gave me practical advice and commented on early versions of this writing. There support and guidance was really helpful. Both supervisors gave me freedom in my design choices, although the did comment on it critically. I have appreciated this professional attitude, which has motivated my during my thesis work.

Beside my official supervisors, some other people showed there interest in my work. I want to thank R.F. Chaves, G.K. Kuzmanov, F. Duarte, B. Donchev and W. van Ooien in no particular order for there support, advice and comment.

Special thanks go to B. Meijs, system administrator of the Computer Engineering Group. I am very thankful for his support during my thesis period, especially for installing the ISE suite twice.

Furthermore I want to thank all other members of the CE group, it was a pleasure to work in this friendly though professional atmosphere.

Lastly I want to thank my relatives and friends. Although they where not directly involved there support, care and love motivated me throughout my study.

Kees van der Bok Delft, The Netherlands October 9, 2007

## Summary

PR (Partial Re-configuration) is a technique that enables changing (i.e. re-configuration) part of a FPGA configuration, on the fly. Usual a re-configurable system is composed out of a fixed and a dynamic part. By means of PR the dynamic part can be re-configured on the fly. Run-time updates is one of the applications of PR. An even more advanced method of PR is Self PR. In this special case the re-configuration is performed by the static part of the design, thus by the system it self.

The MOLEN polymorphic processor framework, from now on referred to as MOLEN framework, is composed of a fixed processor and a re-configurable processor, intends to use the self re-configuration methodology to enable run-time re-configuration of the re-configurable processor.

For efficiency reasons multiple re-configurable processors are proposed. A number of re-configurable areas also referred to as slots are reserved for the re-configurable processors. The current design enables static mapping (i.e. the destination slot is determined at compile time). An additional core, manipulating the re-configuration data needs to be implemented to enable dynamic mapping (i.e. the destination slot is determined at run-time).

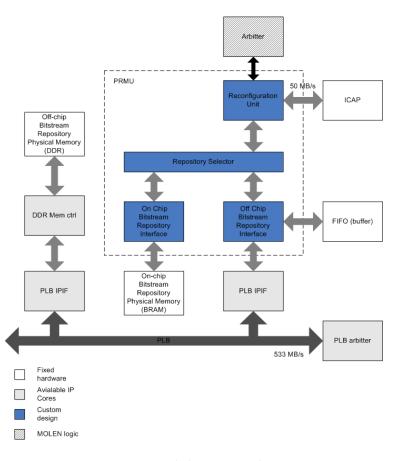

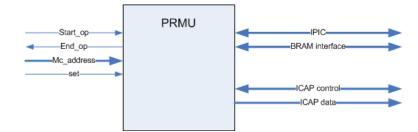

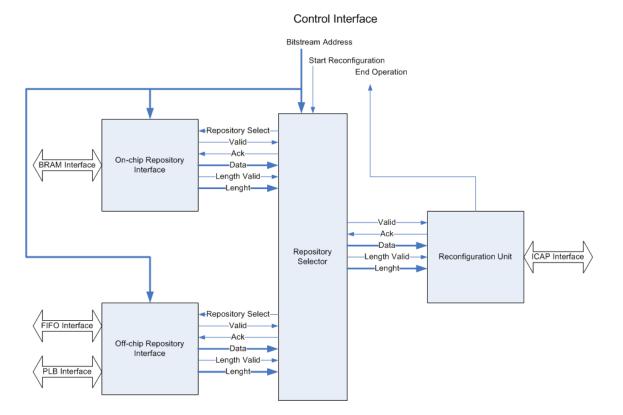

Self re-configuration of a re-configurable processor is realised by the PRMU (Partial Re-configuration Management Unit). The PRMU is an independent core designed for integration in the MOLEN framework. The PRMU is composed of three components the re-configuration unit, the repository selector and one or more repository interfaces.

The re-configuration unit handles the re-configuration process. The re-configuration data is stored in a repository accessible using the repository interface. A repository interface adapts the data transfer protocol of the repository (i.e. memory) to the protocol used within the PRMU. The design supports multiple repositories. The repository selector, an advanced mux, is used to select the proper repository.

The internal data transfer protocol of the PRMU is a handshaking type protocol. This protocol is used for two reasons namely. To simplify the integration of other repositories as currently supported. Furthermore the protocol enables the integration of re-configuration data processing units.

The PRMU is thoroughly verified and tested. By testing and verification processes have proven the proper operation. Furthermore the tests are used to determine the performance parameters of the PRMU. Using the tests we concluded that the PRMU is able of performing a re-configuration at the maximum speed on both the Virtex 2 Pro and Virtex 4 FPGA series.

The current implementation supports only a small repository. This repository is able of storing only a limited amount of re-configuration data. For useful applications support of a larger repository is necessary. Future research is necessary to find a solution for this problem.

To realise dynamic mapping of re-configurable processors a core capable of altering the re-configuration data needs to be implemented. The current design enables rapid integration of such core.

## Contents

# List of Figures ix List of Tables xi 1 Introduction 1 1.1 What is MOLEN ..... 1

|          | 1.2  | The MOLEN Polymorphic Processor Framework                | 2  |

|----------|------|----------------------------------------------------------|----|

|          | 1.3  | The Re-configurable Processor                            | 3  |

|          | 1.4  | The Polymorphic ISA                                      | 3  |

|          | 1.5  | Aims and Context of This Thesis Work                     | 5  |

|          | 1.6  | About Micro-code                                         | 5  |

| <b>2</b> | Stu  | dy into Partial Re-configuration                         | 11 |

|          | 2.1  | Run-time Partial Re-configuration                        | 11 |

|          | 2.2  | RPR Usage in the MOLEN Framework                         | 12 |

|          | 2.3  | Run-time Partial Re-configuration Design Flows           | 13 |

|          |      | 2.3.1 Module Based Partial Re-configuration              | 13 |

|          |      | 2.3.2 Difference Based Partial Re-configuration          | 14 |

|          | 2.4  | Virtex II Pro, Organisation and Re-configuration         | 14 |

|          |      | 2.4.1 Configurable units of the Virtex II pro            | 15 |

|          |      | 2.4.2 Interconnection Infrastructure                     | 16 |

|          |      | 2.4.3 Virtex II pro Architecture                         | 16 |

|          | 2.5  | Re-configuraton Data                                     | 17 |

|          |      | 2.5.1 Bitstream Composition                              | 17 |

|          |      | 2.5.2 Bitstream File                                     | 18 |

|          | 2.6  | Re-location by Bitstream Manipulation                    | 21 |

|          | 2.7  | ICAP                                                     | 22 |

|          | 2.8  | Support of Partial Re-configuration                      | 23 |

|          | 2.9  | Future Developments                                      | 23 |

|          | 2.10 |                                                          | 24 |

|          |      | 2.10.1 Single Re-configurable Module                     | 24 |

|          |      | 2.10.2 Multiple Re-configurable Non re-locatable Modules | 25 |

|          |      | 2.10.3 Multiple Re-configurable Re-locatable modules     | 27 |

|          |      | 2.10.4 Trade Off                                         | 30 |

|          | 2.11 | Functional Design Strategy                               | 31 |

| 3        | Spe  | cifications                                              | 33 |

|          | 3.1  | Functionality                                            | 33 |

|          | 3.2  | Initial Demands                                          | 33 |

|          |      |                                                          |    |

|          | 3.3 | Memory Demands for Bitstream Storage                                       | 35        |

|----------|-----|----------------------------------------------------------------------------|-----------|

|          | 3.4 | Design Considerations                                                      | 35        |

|          | 3.5 | PRMU Definition                                                            | 36        |

|          | 3.6 | Data Rates                                                                 | 37        |

|          | 3.7 | Bitstream Storage                                                          | 38        |

|          | 3.8 | CCU Communication Structure                                                | 38        |

|          |     |                                                                            |           |

| <b>4</b> | Fun | ctional Design                                                             | 39        |

|          | 4.1 | The Top-level                                                              | 39        |

|          |     | 4.1.1 Interfaces of the Top-level                                          | 40        |

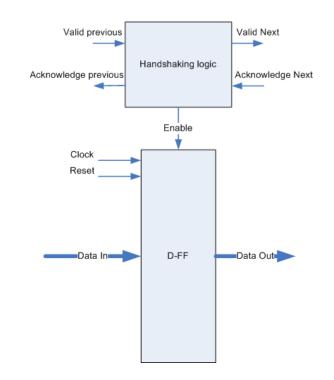

|          | 4.2 | Data Bus Protocol                                                          | 41        |

|          |     | 4.2.1 Data Bus Principle                                                   | 41        |

|          |     | 4.2.2 Data Bus Implementation                                              | 41        |

|          |     | 4.2.3 Justification                                                        | 43        |

|          | 4.3 | Top-level Components                                                       | 44        |

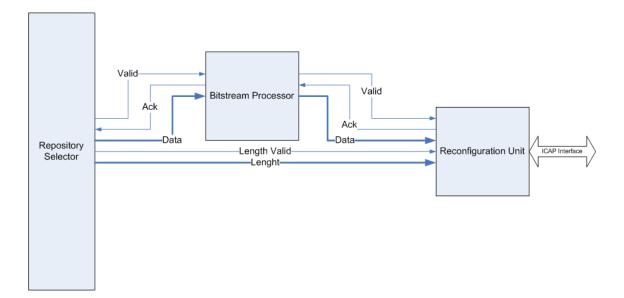

|          |     | 4.3.1 re-configuration unit                                                | 44        |

|          |     | 4.3.2 Repository Selector                                                  | 48        |

|          | 4.4 | Repositories                                                               | 49        |

|          |     | 4.4.1 Repository Interfaces                                                | 50        |

|          |     | 4.4.2 On-chip Repository                                                   | 50        |

|          |     | 4.4.3 Off-chip Repository                                                  | 51        |

|          |     | 4.4.4 Off-chip Data Fetching                                               | 52        |

|          | 4.5 | Memory Initialisation File Tool                                            | 53        |

|          |     |                                                                            |           |

| <b>5</b> | Ver | ification and Testing                                                      | <b>55</b> |

|          | 5.1 | Testbench Driven Verification                                              | 55        |

|          | 5.2 | Testing Using XUP Board                                                    | 56        |

|          | 5.3 | Re-configuration Latency                                                   | 58        |

|          |     | 5.3.1 Measuring Re-configuration Latencies                                 | 59        |

|          |     | 5.3.2 Maximum Data-rate                                                    | 59        |

|          |     | 5.3.3 Relation between the Slot Size and Re-configuration Latency $\ldots$ | 60        |

|          | -   |                                                                            |           |

| 6        | Res |                                                                            | 63        |

|          | 6.1 | Resource Usage                                                             | 63        |

|          | 6.2 | Maximum Clock Frequency                                                    | 63        |

|          | 6.3 | Related Work                                                               | 64        |

| 7        | Cor | clusions and Recommendations                                               | 67        |

| -        | 7.1 | PRMU Conclusions                                                           | 67        |

|          | 7.2 | Recommendations Regarding Design Flow                                      | 68        |

|          | 7.2 | Future Work   Future Sector                                                | 68        |

|          | 1.0 |                                                                            | 00        |

## Bibliography

$\mathbf{71}$

| $\mathbf{A}$ | Plar | ı of Approach                       | <b>73</b> |

|--------------|------|-------------------------------------|-----------|

|              | A.1  | The MOLEN Project                   | 73        |

|              | A.2  | Assignment                          | 73        |

|              | A.3  | Approach                            | 74        |

|              |      | Progress Meetings                   |           |

|              | A.5  | Thesis Support and Supervision      | 75        |

|              | A.6  | Deliverables                        | 75        |

|              | A.7  | Report Layout                       | 76        |

|              | A.8  | Planning                            | 76        |

|              | A.9  | Presence                            | 78        |

| в            | Con  | nmunication structure specification | 81        |

| 1.1  | Schematic representation of the Polymorphic Processor Framework          | 2  |

|------|--------------------------------------------------------------------------|----|

| 1.2  | Schematic representation of the polymorphic processor framework, includ- |    |

|      | ing units for partial re-configuration                                   | 6  |

| 1.3  | Micro-code control logic                                                 | 8  |

| 2.1  | Organization of Virtex II Pro array                                      | 17 |

| 2.2  | Bitswapping of a single byte                                             | 23 |

| 2.3  | Single configurable module concept                                       | 24 |

| 2.4  | Module swapping, conceptual view                                         | 25 |

| 2.5  | Multiple non-relocatable module concept                                  | 25 |

| 2.6  | Multiple non-relocatable module floorplan                                | 26 |

| 2.7  | Communication structure                                                  | 27 |

| 2.8  | Multiple relocatable re-configurable modules                             | 28 |

| 2.9  | Floorplan modification proposal                                          | 29 |

| 2.10 | Inefficient floorplan proposal                                           | 29 |

| 3.1  | Total design simple version                                              | 34 |

| 3.2  | PRMU primitive                                                           | 37 |

| 4.1  | Schematic overview of the Top-level logic                                | 40 |

| 4.2  | Possible implementation of the Handshaking Register                      | 43 |

| 4.3  | Handshaking protocol, start of a burst                                   | 43 |

| 4.4  | Handshaking protocol, end of burst                                       | 43 |

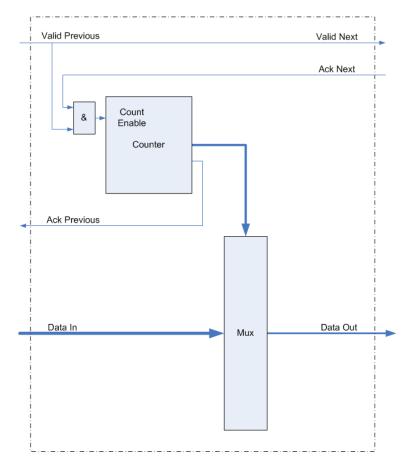

| 4.5  | Insertion of a bitstream processor within the handshaking chain          | 44 |

| 4.6  | Possible implementation of the Width Adapter using standard components   | 45 |

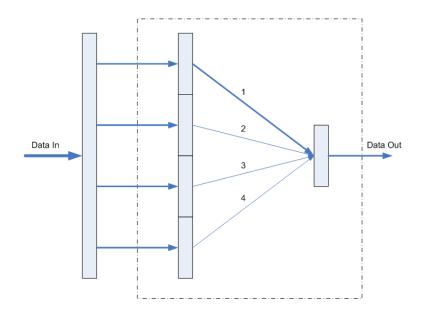

| 4.7  | Abstract principle of the Widthadapter operation                         | 46 |

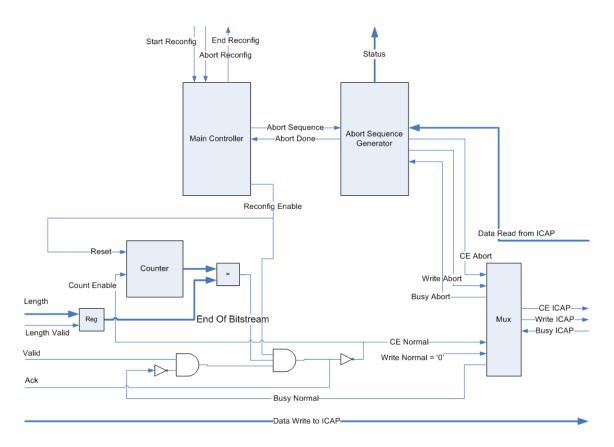

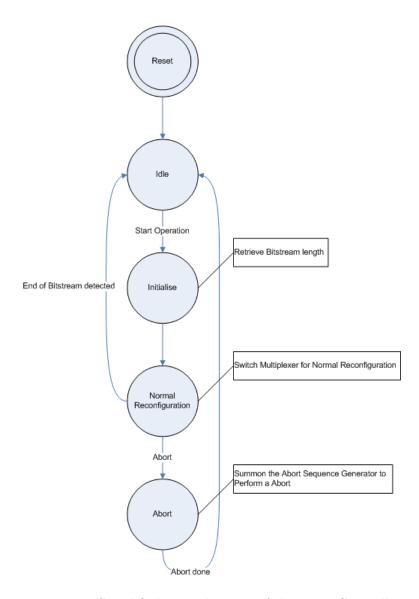

| 4.8  | Schematic representation of the Re-configuration Controller              | 47 |

| 4.9  | Simplified state-diagram of the Main Controller                          | 48 |

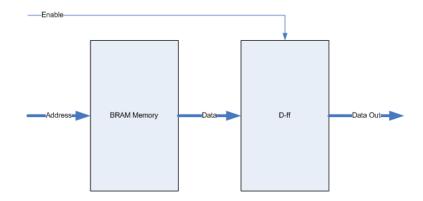

| 4.10 | BRAM implemented single port memory                                      | 51 |

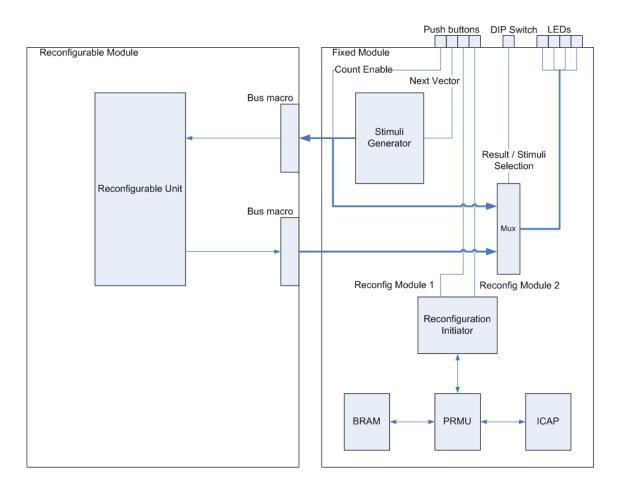

| 5.1  | Schematic of the re-configurable design                                  | 57 |

# List of Tables

| 2.1 | Example Bitstream                  | 9 |

|-----|------------------------------------|---|

| 2.2 | Bit file section composition       | C |

| 2.3 | ICAP pins                          | 2 |

| 2.4 | Score table                        | ) |

| 3.1 | Data rates                         | 7 |

| 3.2 | Bitstream Storage Format           | 3 |

| 5.1 | Truth Table of PRM module 1        | 8 |

| 5.2 | Bitstream size                     | ) |

| 6.1 | Slices and Maximum Clock Frequency | 3 |

| 6.2 | Performance Comparison 64          | 4 |

| A.1 | Time table of thesis period        | 9 |

This chapter gives a brief overview of the MOLEN project. Furthermore the purpose and aims of this thesis work are given. This chapter also describes the context of this thesis work within the MOLEN project.

The next section describes the MOLEN research theme, while section 1.2 describes the MOLEN polymorphic processor framework from now on referred to as MOLEN framework. This framework is one of the main projects of the research theme and is the context of this thesis work. Section 1.4 describes the ISA (Instruction Set Architecture) extension applied to a standard GPP (General Purpose Processor) necessary to realise the polymorphic behavior of the MOLEN Framework. Section 1.5 describes in brief the aims for this thesis work. The last section describes the principle of micro-code. Microcode is a method for implementing control of digital systems. The micro-code principle is discussed because it is a key feature of the MOLEN framework.

### 1.1 What is MOLEN

MOLEN is a research theme of the Computer Engineering group at the Delft University of Technology. The MOLEN theme research is mainly focused on re-configurable computing. A more specific direction of research within this field is adaptable processors. The MOLEN framework described in this section is an example of an adaptable processor.

These adaptable processors also referred to as  $polymorphic^1$ , can be partially adapted. The benefit of a polymorphic processor is that it can dynamically (i.e. run-time) adapt to a specific task. The processor can be adapted either dynamic (i.e. run-time) or static (i.e not run-time).

Adaptable processors can be implemented using re-configurable fabric like FPGAs. Nowadays state of the art FPGAs even offer partial re-configuration. This feature enables the FPGA to re-configured only partial. The PR (Partial Re-configuration) feature enables implementation of fixed en adaptable parts on a single chip. Single chip systems also known as SOCs (System On Chip) have significant advantages over systems distributed on multiple chips. Rapid development and early prototyping are the most relevant of these advantages. Thus RP enables implementation of the MOLEN Framework on a single FPGA.

<sup>&</sup>lt;sup>1</sup>Polymorphic: Composition of poly (many) an morph(form). Meaning: An object capable of occurring in many forms and thus capable of changing form

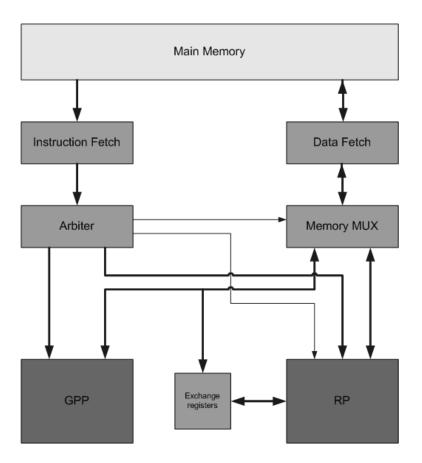

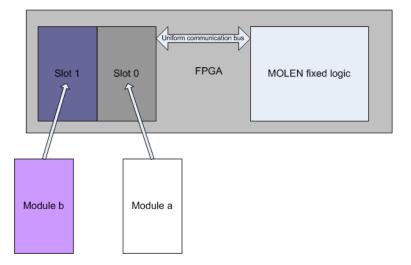

Figure 1.1: Schematic representation of the Polymorphic Processor Framework

The aim of this thesis work is the implementation of RPR applied to the MOLEN framework. The MOLEN framework is a composition of a general purpose processor (GPP) and a re-configurable processor (RP). The framework is discussed in detail in the next section.

#### **1.2** The MOLEN Polymorphic Processor Framework

The MOLEN Framework architecture shown in figure 1.1, contains multiple components which purpose and relations are discussed hereafter.

The GPP (General Purpose Processor) and the RP (Re-configurable Processor) are the main components of the MOLEN framework, these two components are responsible for the actual execution of program code. The GPP executes the ordinary instructions (i.e. instructions which are members of the GGP's instruction set). The RP executes "custom" instructions. These instructions are actually micro-instructions<sup>2</sup> instead of machine-instructions. The re-configurable RP is responsible for the polymorphic

$<sup>^2 \</sup>mathrm{Section}$  1.6 discusses these micro-instructions as well as the general concept of micro-code in more detail

behaviour of the framework.

The other components have a supporting character, one part of the components is responsible for fetching and directing machine-instructions or micro-instructions to the correct processor. Another part is responsible for arbitration of the memory access of both processors, while a third part takes care of the inter-processor communication.

The components managing the instruction fetching and multiplexing are the instruction fetch and the arbiter. The instruction fetch component fetches instructions from the main memory and passes them to the arbiter. The arbiter determines whether the instruction is native to the GPP or a extension instruction. Based on this analysis the instruction is either fed to the GGP or actions are taken to control the RP.

Because both processors need to access the main memory some sort of arbitration is required. The data bus is multiplexed to either the RP or the GPP. The arbiter controls the memory multiplexer. The data fetch component fetches the data from the main memory.

The Exchange registers are used for inter-processor communication i.e. data transfers between the GPP and RP. The exchange registers are accessible by both processors. The exchange registers are meant to transfer small amounts of data.

### 1.3 The Re-configurable Processor

The re-configurable processor or also referred to as CCU (Custom Configurable Unit) is the very essence of the MOLEN framework and needs some further explanation. The RP can be any hardware core, from an advanced ALU (Arithmetic and Logic Unit) up to a processor as complex as a GPP. The RP can use the principle of micro-code, but doesn't have to do so.

The RP has a dedicated interface to the rest of the MOLEN Framework, this interface is specified in depth by appendix B. Every RP has to comply to this interface.

#### 1.4 The Polymorphic ISA

ISA (Instruction Set Architecture) is the set of instructions a particular processor supports. in order to support additional features like for example a RP one could extend the ISA with new instructions. The policy of adding instructions to the ISA for each hardware function or RP has proven to be inefficient. Because it leads to so called instruction set explosion. Large instruction sets with complex instructions make it hard to develop efficient compilers. Thus instruction set explosion is undesired<sup>3</sup>

To prevent a instruction set explosion a one-time instruction set extension is applied in the MOLEN framework. This instruction set extension exists of a limited number of instructions enabling a virtual infinite extension of functions. The complete extension exists of eight instructions listed hereafter.

- set The set instruction initiates a re-configuration of the RP. There are two forms of this instruction namely *p-set* and *c-set*. The *p-set* is a partially set and configures only frequently used functions, while the *c-set* is used to configure all the functions. Thus the *p-set* partial re-configures the RP. The general format of the set instructions are *set* <*address*> where address is the header address of the re-configuration data.

- **execute** The execute instruction is meant to execute a micro-code program on the RP, the format of this instruction is *execute <address>* where address is the start address of the micro-program.

- **set prefetch** This instruction is used to prefetch the configuration data into a fast local memory to diminish loading times.

- execute prefetch Prefetches the micro-program to a local memory.

- **break** The break instruction is used to synchronize the two processors, RP and GPP. The *break* instruction completes a phase of parallel execution of both processors. When a break instruction is fetched the program execution is postponed until both the RP and GPP have finished there current process. Thus the break statement is used to enable parallel execution of a hardware and software threat and forbids it in case of dependency between the two threats

- **movtx** Used to transfer the contents of an general purpose register to a exchange register.

- movfx Used to transfer the content of an exchange register to a general purpose register.

The described instructions are handled by the arbiter, except for the *movtx* and *movfx* instructions which are special instructions offered by the  $GPP^4$ . The other instructions are executed by asserting signals of the RP interface. Native GGP instructions are supplied to the GPP.

$<sup>^{3}</sup>$ The fact that smaller instruction sets enable development to more efficient compilers was discovered in the seventies, the architecture referred to as RISC (Reduced Instruction Set Computer) became popular since this discovery. However GPPs used in nowadays PCs are still CISC (Complex Instruction Set Computer). This less efficient architecture is still used in order to maintain backwards binary compatibility.

$<sup>^4\</sup>mathrm{The}$  GGP of the current prototype is a PowerPC 405, embedded as hardcore in the Virtex II Pro FPGA

Not all the instructions are supported by the current prototype. The prefetch and break commands are not supported, neither is the set instruction.

The solution developed during this thesis enables the set command, although only the c-set command will be supported.

- **start-op** This signal is use to request either the execution of the micro-program or a re-configuration of the RP depending on the set and execute signal.

- end-op This signal tells the arbiter that the requested execution has been performed.

- set The set signal is used as qualifier, when the set and start-op are asserted a reconfiguration is requested. When the set signal is not asserted a micro-program execution is requested.

- execute This qualifier is used to indicate a micro-program execution request.

- **micro-code address** This bus is used to pass the start address of either the micro-code or re-configuration data.

### 1.5 Aims and Context of This Thesis Work

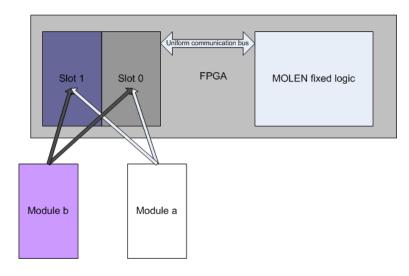

The current prototype does not enable re-configuration of the RP, the main aim of this thesis is to implement RPR (Run-time Partial Re-configuration) and integrate it in the MOLEN framework prototype. The current prototype platform is the Virtex II pro based XUP (Xilinx University Program) board.

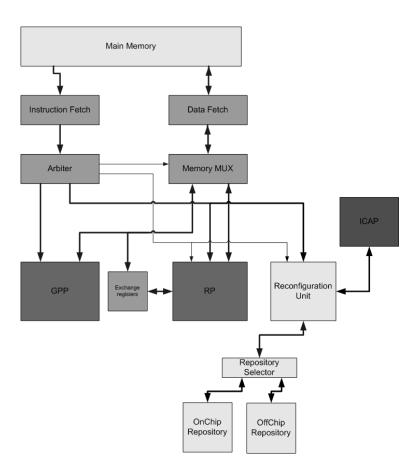

The unit to be develop must interface with the arbiter of the MOLEN framework as shown in figure 1.2. The following paragraph describes the proposed design and its operation in brief.

The arbiter will request a re-configuration by asserting the set and start-op signal as well as supplying the start address of the re-configuration data using the micro-code address bus. The re-configuration data is stored in repositories (i.e. memory). The current design foresees two repositories as shown in figure 1.2. The ICAP (Internal Configuration Access Port) is an internal Virtex II Pro component enabling run-time partial re-configuration of the FPGA.

### 1.6 About Micro-code

Although nowadays FSMs (Finite State Machines) are popular for control logic implementation, it has some disadvantages when it comes to control of complex systems. An other method for implementation control is micro-code, in contrast to the method FSM

Figure 1.2: Schematic representation of the polymorphic processor framework, including units for partial re-configuration

it has proven to be convenient especially in complex systems.

The just mentioned characteristic is the main reason for featuring the micro-code principle in the MOLEN framework.

Digital systems are usually divided into two distinct parts, namely datapath and control. Computer architectures are usual designed using this principle. There are various ways to implement the control part, a FSM is a commonly used method.

Some digital systems like computers require complex control logic. When using a FSM this will lead to a large number of states. Such FSMs are hard to implement and even harder to debug. Instead of using a FSM another method know as micro-code is an attractive alternative for implementation of control logic.

The micro-code principle dates back to the 1950's and was first introduced by Wilkes [12]. Since its introduction the micro-code principle has involved and is widely used in many computer architectures. Micro-code control is based on small programs,

taking care of the control. These programs are called micro-programs. Usually there is a single micro-program for each machine-instruction, covering the control for that specific instruction.

Thus the control of each instruction can be designed independently. This is an advantage over the FSM method, using one huge FSM covering each instruction. Furthermore micro-code is more flexible, because the micro-program(s) can be adapted afterwards.

FSM control can be divided over multiple FSM's to minimise the complexity. Although large FSMs are prevented, it doesn't offer the flexibility and extendibility of the micro-code principle.

We can state that micro-code based control can be advantageous for implementation of complex control, although it requires a non constant<sup>5</sup> amount of memory to store the micro-programs.

Similar to machine code, micro-code is constructed out of binary codes. Machine codes are usually divided into a few field (e.g. the first 6 bits contain the op-code, the next 5 bits contain the target register address et cetera) as is micro-code. The format of micro-code usually exists of two fields, one field is used for control while the other is used for sequencing (i.e. determination of which micro-instruction is to be executed next). Thus a single micro-instructions contains information for control as well as information determining which instruction must follow the current one.

Furthermore there are two distinct types of micro-code, horizontal and vertical. De horizontal controls the hardware directly (i.e. The content of the "control" field is directly supplied to the hardware, hence that the content represents the control signals), the vertical type includes a decode stage (i.e. the content of the "control" field is decoded before the actual hardware is controlled).

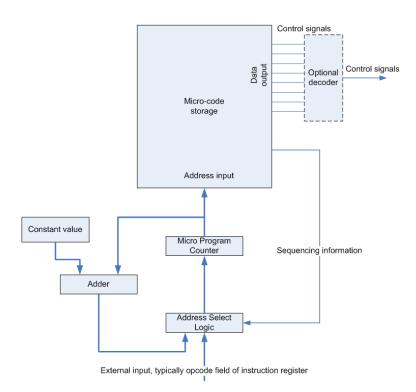

Figure 1.3 shows a typical implementation of micro-code control. The micro-code storage is usual implemented using a certain type of memory: RAM, ROM etc depending on the desired degree of flexibility. A specific range of the output data is supplied to the "logic under control", either direct (horizontal micro-code) or via a decoder (vertical micro-code).

The remaining bits of the output data contain the sequencing information and are supplied to the address select logic. This block controls the micro-program counter, which serves a similar purpose as a program counter known from computer architectures. The micro-program counter selects the next micro-instruction to be executed.

Micro-progams are usually executed in sequential order, although unconditional

<sup>&</sup>lt;sup>5</sup>The memory usage will grow when control complexity increases

Figure 1.3: Micro-code control logic

jumps are also supported. As mentioned before the sequencing information determines the next micro-code to be executed. In case of a sequential execution the address generated by the feedback loop is supplied to the micro-program counter. In case of a jump the sequencing bits are used to to determine the next address to generate (e.g. The sequencing bits represent the relative jump). Thus the number of bits reserved as sequencing information determine the maximum jump.

Furthermore there is a sequencing code serving as end instruction meant to stop micro-code execution at the end of the micro-program. The address select logic can also select an address based on information supplied from outside the micro-code control logic This external supplied information triggers the execution of a specific micro-program. In micro-code based GPPs the external signal is usually the op-code field of the machine-instruction. The content of the op-code field is used to determine the start address of the correct micro-program (i.e. the micro program handling the control of the instruction identified width the supplied op-code).

The MOLEN framework uses a slightly different implementation of micro-code control, although the principle is the same. The implementation shown in figure 1.3 is used for clarity and to eliminate MOLEN framework specific details, irrelevant for the general description given in this section.

Micro-code is supported by the MOLEN Framework for implementation of RPs

9

with complex control. The micro-programs are store in the main memory. The micro-instructions are redirected to the RP by the arbiter. Thus by using micro-code a unlimited number of special instructions can be implemented. These instructions are executed by a RP

For a more detailed description the interested reader is referred to [8] in particular section 5.7. Another another interesting document regarding this topic is [11].

This chapter discusses the matter of partial re-configuration. The discussion is meant to explore the principle and how we can use it to enable run-time re-configuration of the CCU (Custom Configurable Unit) in the MOLEN framework.

Section 2.1 discussed RPR (Run-time Partial Re-configuration) in brief while section 2.2 defines the desired usage of the RPR principle in the MOLEN framework. This section states what we expect from the RPR principle. The remaining sections are mainly focused on how to use the RPR principle in order to implement CCU swapping in the MOLEN framework.

The Xilinx supported design flows for RPR are discussed in section 2.3. These design flows are develop by Xilinx to simplify RPR design implementation.

Section 2.4 discusses the Virtex Pro organisation, furthermore this section gives information about the process of re-configuration. The composition and format of the re-configuration data is discussed in section 2.5. The re-configuration data is wrapped in a file. The format of this file is also discussed in 2.5.

The matter of bitstream manipulation is discussed in section 2.6. Bitstream manipulation is used to enable re-location. The ICAP (Internal Configuration Access Port) is described in section 2.7, the ICAP gives access to the re-configuration logic from within the FPGA.

Section 2.9 and 2.8 are about the future developments of RPR and the current support among FPGA's. Design proposals are discussed in section 2.10. This section also includes a trade off. The last section outlines the proposed functional design strategy.

## 2.1 Run-time Partial Re-configuration

Run-time partial re-configuration is a feature offered by todays state of the art FP-GAs including the Virtex II pro. The feature enables hardware designs to be partially re-configured. It is used for run-time upgrades or for reliability in high radiation environments<sup>1</sup>. Hardware task swapping is a third application of RPR, although it is rarely used.

$<sup>^1\</sup>mathrm{Radiation}$  can harm the current configuration, by performing frequent re-configurations malfunctioning of the system is prevented

Although partial re-configuration is supported it is not often used, especially not in the industry. Academic users have generally more interest in this feature. Due to the fact that the run-time partial re-configuration is relatively slow and limited, most of the academic research concentrates on the conceptual level. Some experimental so called "self configuring systems" are developed, but they haven't proven to be very efficient.

Many papers discussing the matter of partial re-configuration conclude that the feature is not mature enough to exploit its potential. The current limitations of partial re-configuration is seen as major obstacle to a totally new application of FPGAs, namely self reconfiguring systems on chip.

A fast and more mature version of partial re-configuration enables the development of efficient self reconfiguring systems. Which would be a complete new and promising concept. Efficient self reconfiguring systems combine the flexibility of software and the performance of hardware.

#### 2.2 RPR Usage in the MOLEN Framework

This section discusses a general concept of the desired usage of the partial reconfiguration feature of the Virtex II pro in the MOLEN processor. Although this concept is naive it is good to have an ideal concept before considering possible limitations. By this approach one is not influenced or actually controlled by the limitations, but can anticipate to them by adapting the naive design to a feasible version. Which should result in a design close to what is initially intended.

Implementation of real-time hardware unit swapping is one of the phases of the development of the MOLEN framewok. RPR is supported by the Virtex II pro FPGA. The Virtex II pro is currently used as prototyping platform for the MOLEN project. Hardware unit swapping can be realized by using the RPR principle.

Using the RPR principle we want to implemented a form of hardware task swapping. For efficiency reasons we consider multiple hardware tasks (i.e CCUs) to operate in parallel. Using RPR we want to enable "loading" of hardware tasks. Furthermore we want the loaded hardware tasks to be mapped to a free space of the FPGA. When there is no free space available, we want other tasks to be removed to make place for the new task.

The dynamic (i.e. run-time) mapping of the hardware tasks also referred to as re-location, would highly improve the efficiency and user friendliness of the MOLEN framework. The remainder of the chapter describes the technical details of RPR. Furthermore the feasibility of our proposal is determined.

#### 2.3 Run-time Partial Re-configuration Design Flows

Xilinx offers two basic methodologies for implementation of partial re-configuration [13]. Module based and difference based partial re-configuration. In this section the two Xilinx supported methodologies are described.

A third possibility is the manipulation of the configuration data. This last option is not supported by Xilinx ,but there are some academic projects using this unorthodox methodology see [4], [9] and [3]. This method is not discussed in this section, but in section 2.6 because it requires more detailed knowledge of the re-configuration process.

#### 2.3.1 Module Based Partial Re-configuration

The module based partial re-configuration methodology integrates partial reconfiguration in the "Xilinx Modular Design flow". This methodology is originally intended to manage projects in which multiple designers participate.

The modules of a modular design are separate projects. A module can be implemented independent. The integration of modules is done after successful verification of each module.

Xilinx has extended the modular design flow in order to support partial reconfiguration. A module based partial re-configurable design is composed of multi modules. Each module can either be static or re-configurable.

The "Modular design flow" is based on the following steps, which are derived from Xilinx documentation see [13].

- 1. A top-level design needs to be constructed which defines the interfaces of each module. Furthermore each module must be assigned a fixed area on the FPGA by means of a floorplan.

- 2. The separated modules can be developed and tested independently. The implementation must meet the constrains specified by the toplevel design and floorplan.

- 3. Finally the intended system can be realized by intergrading the separately implemented modules.

The described design flow can be extended by making one or more modules reconfigurable. In order to make a module re-configurable one has to take care of signals crossing the module border. Signals crossing the re-configurable modules boundaries must do so through fixed routing bridges referred to as "bus macros".

The "bus macros" function as fixed interfaces at the module boundaries. Due to these components, a module can safely being overwritten by another module compatible to the interface. Without losing inter-modular communication.

The module based design flow does not support dynamic mapping of a module. The area that will be occupied by the module must be determined during implementation. Thus dynamic mapping or re-loaction is not supported by this standard design flow.

The preceding discussion leads to the conclusion that the "Module based partial re-configuration" methodology does not support re-location of hardware units. The "Module based partial re-configuration" methodology must be extended or another methodology must be used to enable re-location.

#### 2.3.2 Difference Based Partial Re-configuration

The "Difference based partial re-configuration" is the other Xilinx supported methodology for partial re-configuration. This difference based methodology is meant to switch to another implementation which slightly differs from the original.

The advantages of this method is that only the differences between the two implementations are re-configured. The re-configuration data for the partial re-configuration is formed by the difference between both implementations. Due to the fact that the redundant parts of the implementation are preserved and only the changes are altered there is a gain in re-configuration latency above a complete re-configuration.

Although the discussed methodology offers a superb way to perform a runtime upgrade, it is not suitable in the foreseen usage of partial re-configuration in the MOLEN processor. Because CCU's typically use a significant area of the chip. The difference based flow is not beneficial in such case. However the difference based flow can be advantageous when we consider two or more CCUs which slightly differ. Using the difference based method in these cases can result in a significant performance gain, although the logic controlling the re-configuration process will increase in complexity.

Further research must be done in order to determine whether the it is worth supporting difference based design in the MOLEN framework.

### 2.4 Virtex II Pro, Organisation and Re-configuration

In this section the re-configuration of the Virtex II pro is discussed. The principle of re-configuration and the organization of the re-configurable components are discussed. The information in this section is mainly intended to understand the re-configuration process and the format of the re-configuration data.

An FPGA is a chip containing logic components and programmable interconnects. During configuration the components are programmed and interconnections between these components are made in order to realize a digital system.

A logic component typically contains LUTs (Look Up Tables) as well as flip flops. The former is used to emulate combinatorial behavior while the later is used to construct sequential logic. By means of the programmable interconnects the logic components are connected in order to realize a digital system.

A FPGA is re-configured using re-configuration data, generated by implementation tools. Xilinx refers to the re-configuration data as bitstream. The bitstream is usually created by synthesizing a hardware description, formulated in a HDL (Hardware Description Language) like VHDL.

Nowadays FPGAs offer specialized hardware units in addition to the standard logic components. These dedicated hardware blocks are usually multipliers, dividers, RAM or other specialized units.

Although FPGAs are commonly used for rapid prototyping, new application fields are foreseen due to development of concepts like RPR.

#### 2.4.1 Configurable units of the Virtex II pro

The Virtex II pro FPGAs has several programmable logic components as described hereafter. The descriptions are intentionally kept brief, because they are meant to give a general understanding prior to the discussion of the architectural organization of the FPGA.

- **CLB** The *Configurable Logic Blocks* are the basic components of the FPGA. Combinatorial as well as sequential logic can be constructed using these blocks. Furthermore these blocks contain multiplexers.

- **Multipliers** The FPGA is equipped with a number of dedicated multipliers. The dedicated multipliers are much more efficient in terms of footprint than a multiplier constructed using CLBs.

- **BRAM** Block RAM Memory for data storage are encapsulated in the FPGA.

- **SelectRAM** These components are used to configure a interface to the BRAMs. Memory blocks of a desired capacity and width<sup>2</sup> can be configured using BRAM and BRAM interconnect components.

- **IOB** Input Output blocks, contain logic to configure a pin of the FPGA as input or output. Furthermore the IOB can be used to configure a specific I/O standard.

- **IOI** The *Input Output Interface* components are used to configure the I/O pins behavior e.g. tristate, weak, strong etc.

<sup>&</sup>lt;sup>2</sup>There are some restrictions regarding the width an capacity

- **PowerPC hardcore** The version of Virtex II pro FPGA used during this project contains two hardcore PowerPC general purpose processors. The cores are mapped within the configurable array, but are not re-configurable themselves.

- **MGT** The *Multi Gigabit Transceiver* core is a programmable core used for high speed data communication with the outside world. The MGT cores are not used within this project.

- **DCM** The *Digital Clock Manager* The DCM primitives are generating clock signals for the design. A DCM can produce an number of clock signals, DCMs can either multiply or divide a source clock signal. Furthermore a DCM can adapt the phase ad the duty cycle of the input clock cycle etc.

#### 2.4.2 Interconnection Infrastructure

The interconnection infrastructure is formed by routing wires. These wires run through the chip in vertical and horizontal direction. The wires can cross the entire chip or only part of it, respectively local and global routing wires.

During configuration, routing wires are connected to each other in order to create paths. These paths interconnect the various components of the FPGA. This process is referred to as routing. The connections are made using the interconnection switches.

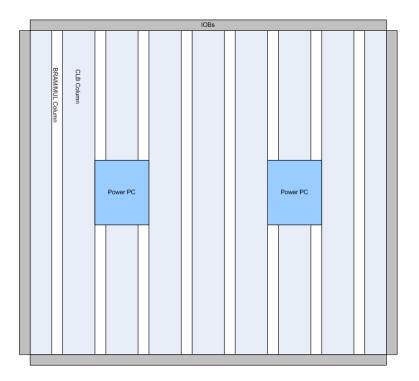

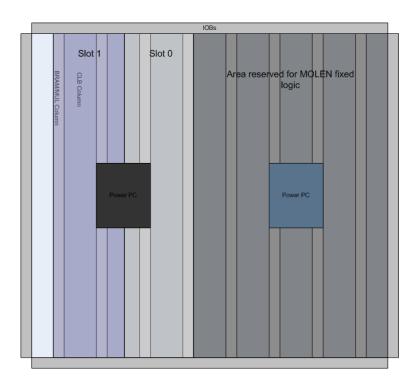

#### 2.4.3 Virtex II pro Architecture

In general the array of an FPGA is organized in a way that enables efficient routing. Because the organization of the array is crucial to determine if bitstream manipulation is feasible, a discussion follows.

The array is organized in columns of equal components see figure 2.1. Each column is divide in multiple frames. In general there are two types of columns: CLB columns and BRAM/MUL columns. The former contain CLB elements while the later contain multipliers, memory and selectRAM components. BRAM/MUL columns are followed by CLB columns, this pattern is repeated throughout the entire array. The two hardcore PowerPc units are located half way the third<sup>3</sup> an seventh column see figure 2.1. The PowerPc units stretch two BRAM and one CLB row. IOB elements surround the entire array.

Re-configuration is the process of "programming" the FPGA elements and routing the interconnection between them. Information about the "programming" of elements and interconnection paths is given by the re-configuration data or bitstream.

The Virtex II Pro is a SRAM based FPGA. SRAM based FPGAs feature a SRAM memory to re-configure the FPGA. The bits stored in this memory configure the under

<sup>&</sup>lt;sup>3</sup>The columns are counted from left to right

Figure 2.1: Organization of Virtex II Pro array

laying components such as CLB's et cetera. The memory is written in a vertical way segment by segment. These segments also referred to as frames are one bit wide and are the smallest addressable portion of the configuration memory.

### 2.5 Re-configuraton Data

The re-configuration data referred to as bitstream is basically a sequence of commands and data. The re-configuration logic encodes this bitstream and configures the FPGA according to these commands and data.

The following section describes the composition of a bitstream. An example bitstream is given and discussed in detail. The second section handles the format of a bit file. A bit file is a file generated by the Xilinx tools. A bit file is composed out of the bitstream and some additional information.

#### 2.5.1 Bitstream Composition

A bitstream starts with a unique synchronisation word, this word is unique within the bitstream. The rest of the bitstream is composed out of headers followed by a number of data words. The header contains the destination of the data as well as the number of

data words that follow. The composition of header and data is called a package.

There are two forms of the header word, the Type 1 and the Type 2 header. A Type 2 header is optional and follows the Type 1 header. An additional type 2 header must be used when the word count (i.e the number of data words following the header) is to large to fit in the type 1 header.

When a type 1 header is used the ten least significant bits of the header word are used to represent the word count (The maximum word count value is  $2^{10} = 1,024$ ) When using a additional Type 2 header the 27 lower bits of this word represent the word count (The maximum word count is  $2^{27} = 134,217,728$ ).

There are two other commands, namely the *de-synchronisation* word and the *no-operation* word. The *de-synchronisation* word is used to end the re-configuration, a few additional *no-operation* words may follow to flush the re-configuration logic's buffer. Table 2.1 shows a example Bitstream, this Bitstream is not complete, but it shows how a Bitstream is composed.

In the example bitstream a few specific registers are addressed. These registers are embedded within the re-configuration logic and accessible through the ICAP. The address registers and there purpose are described hereafter.

**CRC** Cyclic Redundancy Check register, this register is used to store the CRC word of the bitstream.

**CMD** The command register

FAR Frame Address Register

FDRI Frame Data Register Input

#### 2.5.2 Bitstream File

The Xilinx Bitgen tool is used during the design flow to generate Bitstreams as described in the paragraph 2.5. Bitgen produces a ".bit" file, composed of the Bitstream and and some additional information regarding the Bitstream. Because the Bit file format is not documented some reverse engineering was use to analyse the actual format. Understanding the Bit File format is necessary because when applying on-chip partial re-configuration we need to store the Bitstream in On-chip memory. Furthermore the on-chip re-configuration logic doesn't except the additional information, only the raw bitstream must be written to the configuration port.

The Bitgen tool generates the Bit file using the ncd file, the ncd file is a description of the design implementation in respect to the target device. The ncd file is the output of the PAR (Place And Route) process. The Xilinx implementation flow is given by the following enumeration.

| Configuration Data | Explanation                                        |

|--------------------|----------------------------------------------------|

| 0xAA995566         | Synchronisation word                               |

| 0x30000001         | Type 1 Header: Write 1 word to the CRC register    |

| 0x00009A32         | Packet Data: CRC Word                              |

| 0x30008001         | Type 1 Header: Write 1 word to CMD register        |

| 0x00000001         | Packet Data: WCFG command                          |

| 0x30002001         | Type 1 Header: Write 1 word to the FAR register    |

| 0x02000000         | Packet Data: Frame Address                         |

| 0x3000401A         | Type 1 Header: Write 26 words to the FDRI register |

| 0x???????          | Packet Data: Reconfig. Data word 1                 |

|                    | Packet Data: Reconfig. Data n                      |

| 0x???????          | Packet Data: Reconfig. Data 26                     |

| 0x0000A53B         | Auto CRC word                                      |

| 0x000000D          | De-synchronisation Word                            |

| 0x20000000         | Optional No Operation word                         |

| 0x20000000         | Optional No Operation word                         |

Table 2.1: Example Bitstream

- 1. HDL coding

- 2. Synthesise

- 3. Translate

- 4. Map

- 5. Place and Route

- 6. Programming File Generation (i.e. Bitstream)

As mentioned in the preceding paragraph, the Bit File is composed of a header followed by the Raw Bitstream. The Bit File exists of a few sections each containing specific information. The header information is used by Xilinx programming tools to validate whether the Bitstream suites the target device.

The sections of the Bit File contains a key, length field and a data field. The key is a single ascii character, a to e where a is the fist section b the second etc. The length field is always followed by NULL byte (i.e. hex 00). The Length field is a single byte representing the length of the data field in bytes. The information or header sections contain ascii formatted strings terminated with a NULL word<sup>4</sup>. The last section, section e contains the Bitstream and some additional information. Interesting detail is that the first section is not preceded with a character.

<sup>&</sup>lt;sup>4</sup>Equivalent to C strings

# Table 2.2: Bit file section composition Key Length Content

Table 2.2 shows the typical section composition all sections comply to this format. Except for the first section referred to a preamble. The e section containing the actual has bitstream has multiple byte length field in contrast to the other sections al having a one byte length field.

**preamble** Nine byte section containing undefined data, probably a fixed header saying this is a bit file.

NULL word ascii NULL word (Hex 00)Length field Length of the preamble section (hex 09)Data field probably an ID content: (hex 0F F0 0F F0 0F F0 0F F0 00)Extra NULL word

Section 'a' Source file

Key (ascii 'a')

NULL word

Length field Content: Variable

Data field Source ncd file, content example: PRM2\_partial.ncd

Section 'b' Target device

Key ascii 'b' NULL word Length field Data field Target device, content example: 2vp30ff896

Section 'c' Date of generation

Key ascii 'c' NULL word Length field Data field Date of generation, content example: 2007/07/26

Section 'd' Time of generation

Key ascii 'd' NULL word Length field Data field Time of generation, content example: 15:15:19

Section 'e' Bitstream

Key ascii 'e'

NULL word

Length field The length of the bitstream in bytes<sup>5</sup>

**Dummy word** The dummy word is apparently used to flush the buffer of the re-configuration logic, content : hex FF FF FF FF

Data field bitstream

- content start: hex AA995566

- content end: hex 00 00 00 0D or hex 20 00 00 00

## 2.6 Re-location by Bitstream Manipulation

The two supported methodologies have proven to be insufficient in order to implement the desired concept of relocation. Because of that other ways must be explored. At first the possibility and feasibility of bitstream manipulation is discussed. The discussion is based on the following question.

Is it possible to manipulate the configuration data in such a way that the module will be mapped to an other area as it was originally intended to ?.

A brief search for papers concerning this subject revealed that the idea of configuration data manipulation had been risen to the minds of several researchers. In these papers concepts are proposed. Some of them even claim functional implementations. For more detail see [3], [4] and [9].

Based on this information the answer to the earlier question is yes.

The question remains what exactly must be manipulated, for bitstream is a rather vage term which can interpret in many ways. In section 2.5 we saw that the addressing of the destination frames is incapsulated within the bitstream. If we alter the frame addresses in the bitstream by adding an offset, the re-configuration is applied to a other area of the FPGA. Thus by doing so we are able to configure various areas of the FPGA using a single source bitstream.

The implementation of this relocation must scan the bitstream for the hearder word addressing the FAR (Frame Address Register) and alter the word following this header. Hence that the word following the header is the frame address.

<sup>&</sup>lt;sup>5</sup>In contrast to the other length fields this length field is three bytes wide

| Name   | Direction | Description                                              |

|--------|-----------|----------------------------------------------------------|

| CLK    | Input     | Clock signal                                             |

| CE     | Input     | Config. Enable, set 'high' to pause reconfig. operation. |

| Write  | Input     | Read, write signal write='0' read ='1'                   |

| BUSY   | Output    | Signal, asserted 'high' when re-configuration is pending |

| O[7:0] | Output    | Config. data output (read)                               |

| I[7:0] | Input     | Reconfig. data input (write)                             |

Table 2.3: ICAP pins

## 2.7 ICAP

The ICAP is one of the interfaces to the re-configuration logic. The other interfaces are: JTAG, serial slave and select map. The ICAP is the only interface that allows on-chip re-configuration (i.e. re-configuration controlled from within the chip).

The ICAP interface is a subset of the select map interface. The ICAP does not allow a complete re-configuration and there fore does not need some of the pins the select map interface is equipped with.

Both select map and ICAP allow re-configuration data to be written to or read from the re-configuration logic in byte wide portions. In addition to the data bus, both interfaces are equipped with some pins used to control the re-configuration process. The pins of the ICAP interface are described by means of table 2.3.

The ICAP interface is based on a handshaking principle. the CE and BUSY signal are used to control the data flow. The BUSY pin is asserted when the buffer is full. When the BUSY is asserted the data on the data-bus is ignored. The CE pin is used to pause the re-configuration process. Supplied data is only accepted when the CE signal is asserted and the BUSY signal is not.

There is a alternative way of controlling the ICAP, namely by keeping the ce asserted and using the clock pin to perform a write or read action. This method of controlling is based on the fact that a write or read action is performed on the falling edge of the clock signal if and only if the ce pin is asserted.

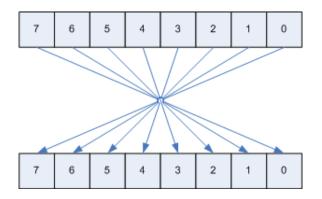

An important detail of the ICAP interface is that the re-configuration data needs to be bit swapped on a byte bases. Thus the MSB (Most Significant Bit) of a re-configuration byte is the LSB (Least Significant Byte) of the data-bus. This implies that bit 7 must be connected to bit 0 of the data-bus, bit 6 to bit 1 etc. Figure 2.2 gives a graphical representation of the swapping.

Figure 2.2: Bitswapping of a single byte

The ICAP can be instantiated as a primitive in a HDL based design. Furthermore Xilinx offers a core called the HW\_ICAP. This HW\_ICAP is a OPB (Onchip Peripheral Bus) device. The OPB interface allows the ICAP to be controlled by means of a microprocessor.

## 2.8 Support of Partial Re-configuration

Although some sources claim that partial re-configuration is also supported by non Xilinx FPGAs, documentation provide by other FPGA vendors regarding this feature is poor. Because of this reason the discussion is limited to Xilinx FPGAs only.

The MOLEN will likely be mapped to the Virtex IV or Virtex V FPGA in the near future. Because of that it is useful to know about the differences between these devices and the Virtex II pro.

The Virtex IV and Virtex V are both equipped with a ICAP interface similar to the one of the Virtex II pro. The width of the data-busses and the data-rate of these busses are the only differences among the Virtex series ICAP primitives. Thus it is rather easy to develop a generic solution compatible width all Virtex FPGAs.

## 2.9 Future Developments

Partial re-configuration is a feature which enables the development of self-reconfiguring systems. In nowadays FPGAs the feature is not mature enough to make these systems efficient. There are two major disadvantages to modern FPGAs supporting partial re-configuration.

Re-configuration latencies Re-configuration of a FPGA is relatively slow and will

Figure 2.3: Single configurable module concept

therefore delay the system significantly. It is possible that the execution time diminish by the dedicate hardware is lost due to the re-configuration delay.

**Array organization** The array of most modern FPGAs is not uniform enough to easily implement re-location of hardware units.

To fully exploit the RPR concept FPGAs needs to be improved especially regarding the mentioned RPR limiting issues.

Whether future FPGAs will be designed for RPR systems depends mainly on the economic benefits for FPGA manufacturers.

## 2.10 Design proposals

Study of the Virtex II pro device and discussion with people of the CE group resulted in three design proposals. This section handles the advantages as well as disadvantages of the each proposal. Furthermore a tradeoff is included, based on this tradeoff a plan is made for the functional design.

#### 2.10.1 Single Re-configurable Module

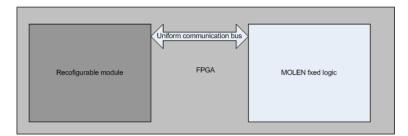

The most basic implementation of RPR is a "Single configurable module" design. This design is based on a two module approach, where one module is fixed(MOLEN framework) and the other one is re-configurable (RP) see figure 2.3. Note that in this discussion the term unit and module are considered to be synonym.

The re-configurable module and fixed module are equipped with a fixed interface. The re-configurable module can be swapped with any other module supporting the same interface and which is mappable to the area reserved for the re-configurable module. Figure 2.4 shows the module swapping principle.

The main advantage of the described concept is the simplicity, which implies that it is rather easy to implement. However the concept lags in flexibility, because there

Figure 2.5: Multiple non-relocatable module concept

can be only one module present at a time. Every time the MOLEN needs another module a time consuming re-configuration needs to be performed. This can contribute to a significant decrease of performance especially when two modules are used in an alternating order.

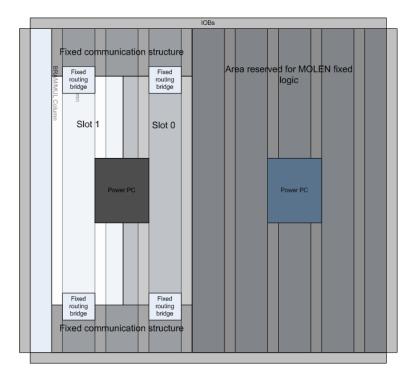

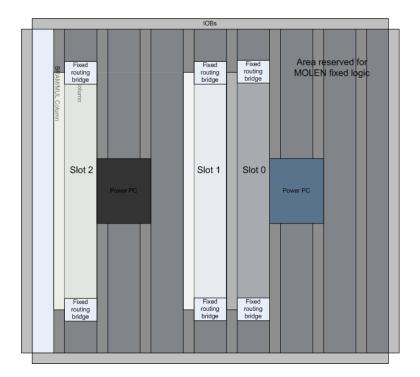

#### 2.10.2 Multiple Re-configurable Non re-locatable Modules

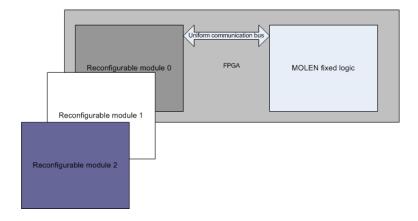

A more flexible approach is by offering multiple re-configurable areas instead of one. In contrast to the earlier one, this concept enables swapping one module while the other one(s) remain(s).

In this conceptual discussion we limit the number of independently re-configurable areas to two. These re-configurable areas are called slots throughout this document. Both slots can contain one single module. A slot can be re-configured without interfering

Figure 2.6: Multiple non-relocatable module floorplan

with the other module. Figure 2.5 gives a graphical representation of this concept.

Due to the fact that the module bitstreams are location fixed a module can only be mapped to one of the slots. The slot a module is mapped to can only be determined during design time and not during run-time. One can overcome this restriction by generating a separate bitstream for each slot. In the current discussed concept this means that two bitstreams per module are required. When increasing the number of slots the number of bitstreams increases linear, because each module must have a separate bitstream for each slot. This work around results in multiple bitstreams all serving the same function. Because these bitstreams must all be present in memory it is obvious that this work around dramatically decreases the memory usage efficiency.

Due to its physical architecture the FPGA can only be configured frame by frame, each frame spans the complete device height. Based on this observation the proposed slots can at best be aligned vertically, making the slots independently re-configurable.

Although the advantages of this choice is obvious it implies a new problem. Due to the very nature of module based design, modules can only communicate to modules adjacent to them self. By aligning the slots vertically the slot adjacent to the fixed logic isolates the other slot from the fixed logic as shown in figure 2.6.

The problem immersed in the preceding paragraph can be tackled by extending the

Figure 2.7: Communication structure

fixed logic by a communication structure interconnecting the slots and the fixed part of the MOLEN. Figure 2.7 shows this principle.

During and after re-configuration the communication structure must remain unchanged. Due to the fact that re-configuration is glitch less the logic can safely be overwritten by the original configuration leaving the logic unharmed.

The just mentioned principle can be used to prevent the communication structure from being influenced during re-configuration. The principle can be used by including the original configuration data of the communication structure vertically adjacent to the slot area within the partial bitstream.

The concept discussed in this section enables swapping on a module bases, although the description is based on two slots the concept can easily be extended to support more slots. The main limitation of the concept is that a module can only be mapped to a specific slot. Random placement of a module can be enabled by generating a bitstream for each slot. This method implies an significant increase of bitstreams to be stored in the main memory, which has a negative influence on the memory usage efficiency.

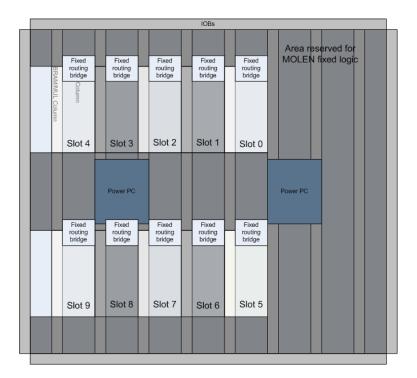

#### 2.10.3 Multiple Re-configurable Re-locatable modules

The multiple re-locatable module concept is a extension of the previous discussed one. The currently described concept is based on the slot based architecture discussed earlier.

Figure 2.8: Multiple relocatable re-configurable modules

The Multiple re-locatable module concept enables a module to be mapped to any slot. The re-locatable mapping is realized by performing bitstream manipulation.

Re-locatable mapping by bitstream manipulation requires slots that are completely homogenous. To create a significant number of homogenous slots the current MOLEN floorplan needs some changes. The proposed changes are graphically represented by Figure 2.9.

Figure 2.9 shows that the FPGA organization is a limiting factor while planning homogenous slots. An other FPGA could be more convenient.

Other slot organizations could be proposed but the one described is the most feasible option. Due to the fact that the array can only be configured per frame it is beneficial to keep the slots narrow (horizontally seen). Because narrow slots contain less frames the re-configuration latency is minimized.

Furthermore multiple slots in the vertical direction will increase the complexity of a re-configuration operation, because overwriting of the other slots vertically adjacent to the one re-configured must be prevented.

This issue can be tackled by reading out the entire vertical area first. After that merging the read out data with those of the module to be replaced. By writing the merged data back only the intended module is changed This sequence of read, merge and write back is too time consuming to be effective. Figure 2.10 shows an other though less efficient floorplan.

Figure 2.9: Floorplan modification proposal

Figure 2.10: Inefficient floorplan proposal

| Proposal              | Table 2.4: ScorDesign complexity |     | Performance | Appraisal  |

|-----------------------|----------------------------------|-----|-------------|------------|

| Single                | +                                | -   | -           | Useful     |

| Multi non-relocatable | +                                | +   | +           | Useful     |

| Multi relocatable     | ++++                             | +++ | +++         | Final goal |

#### 2.10.4Trade Off

In this section three design proposals are discussed, namely "Single re-configurable module" figure 2.3, "Multiple non-relocatable re-configurable modules" figure 2.5 and "Multiple re-locatable re-configurable modules" figure 2.8. The advantages and disadvantages of each proposal has been discussed. A trade off needs to be performed to determine the best solution. A rating table is used for this tradeoff, see table 2.4.

By means of table 2.4 the three design proposals are rated. The proposals are rated on implementation complexity, flexibility and performance. Furthermore a total appraisal is given.

From table 2.4 we conclude that the design of both the single module and the Multi non-relocatable are equal in complexity. Because the single module design lags in flexibility and performance, mainly due to constant swapping, it is given a lower appraisal. The single module design is however a useful intermediate stage during the development.

The Multi non-relocatable leads to more flexibility and performance with about the same amount of effort. A disadvantages of the this design however is the necessity to schedule the mapping of modules during compile time. The Multi relocatable overcomes this disadvantages because the mapping is dynamic (i.e. the destination slot is run-time determined).

The multi re-locatable design enables the modules to be mapped to a free slot, if there are no free slots left a replacement algorithm will determine which other module must be dropped. Thus the dynamic or re-locatable mapping implies an administration of slot usage to be kept, as well as the implementation of a replacement algorithm. This will increase the design complexity significantly.

In conclusion we state that the *Single Module* option is a useful intermediate stage, the Non-relocatable option on the other hand is considered a valuable addition to the MOLEN framework. In fact some members of the Computer Engineering group can use it in there current research, the *relocatable* option is the by far the most advantaged application of Partial Re-configuration.

# 2.11 Functional Design Strategy

Based on the tradeoff a plan or strategy for the functional design can be made. As discussed in the preceding sections at first a one slot solution is implemented. In the second phase this implementation is extended to support multiple slots. The last phase of the design implements re-location of units.

The main advantage of the three phase approach is a spreading of complexity. Furthermore the second phase implementation is not just a intermediate version, but is actually useful for other MOLEN project members. In both the plan of approach and the introduction, we have briefly defined the purpose of the logic to be designed. In this chapter we are defining some key requirements, in order to determine some design consideration. Based on the design considerations the functionality is divided among a few functional units.

The remainder of this chapter is organized as follows. Section 3.1 discusses the functionality of the PRMU, this section gives a definition of the PRMU. In section 3.2 the initial demands are given, these are demands the design must comply to in order to enable integration into the MOLEN Framework. The initial demands lead to a few design considerations discussed in section 3.4. Based on the design considerations a more detailed definition of the PRMU is given in section 3.5. The maximum data rates of some key interfaces are discussed in section 3.6, while the storage of the bitstream in the repositories is discussed in section 3.7. The last section discusses the interface of the CCU, this interface has no relation with the PRMU design. The interface is discussed because it determines the signals of the communication structure between the fixed and re-configurable parts of the design.

## 3.1 Functionality

Based on the conclusions of the preceding chapter, a draft diagram is made. This block diagram is shown in figure 3.1. The PRMU (Partial Re-configuration Management Unit) functional block covers the main functionality of this thesis work. The other blocks are either hardware components or IP-cores.

The PLB (Processor Local Bus) including related components are used to access the off chip DDR-memory. The PLB is composed of Xilinx supplied ip-cores, these IP-cores can be instantiated without significant effort.

The key functionality of the design is: Partial re-configuration of the FPGA using configuration data from a storage device. The storage device can either be implemented using internal FPGA resources or physical memory external to the chip.

## **3.2** Initial Demands

There are four demands tot the design, these demands are a result of the implementation platform chosen and the foreseen integration within the MOLEN Framework.

Figure 3.1: Total design simple version

- The implementation target is the XUP (Xilinx University Program) Board. The XUP Board is equipped with a Virtex 2 pro FPGA, type V2P30. The board contains a few other chips and expansion slots, the most relevant of these is the DDR (Double Data Rate) Memory.

- The On-chip Repository must be implemented using the FPGAs BRAM components.

- The Off-chip Repository must be implemented using DDR memory available on the XUP (Xilinx University Program) board.

- Interfacing with the DDR memory must be done using the PLB (Processor Local Bus).

Furthermore performance, re-configuration latency in particular, is an important issue. The design should enable re-configuration at the maximum speed. The design should also be portable to the Virtex 4 device, because this devices has several advantages a higher re-configuration data-rate is one of them. The following concrete demand is extracted from the preceding discussion.

• The design must enable re-configuration at the highest possible data-rate on both the Virtex 2 Pro and the Virtex 4.

## 3.3 Memory Demands for Bitstream Storage

As mentioned earlier the bitstream must be stored in memory. Based on the specifications in the Virtex 2 Pro datasheet [1] we can estimate the required amount of memory.

According to the Virtex 2 Pro datasheet [1] a complete bitstream contains approximately  $12 * 10^6$  bits. In the two slot design proposed in chapter 2 a single slot covers about a quarter of the FPGA area. Thus a bitstream for such slot contains about  $3 * 10^6$ bits. This implies that storing a bitstream requires at most 366 KB.

The Virtex 2 Pro, type XCVP30 contains a total amount of 2,448 Kb or 306 KB. Thus the on-chip memory resources are limited, moreover it is not even enough to store a single bitstream.

In the current prototype the bitstream address is 24 bits wide, allowing a addressing range of  $2^{24} = 16,777,216$ . In case of the 64 bits addressable DDR memory this means that 428 bitstreams can be stored as proven by the following calculations.

The total addressable bytes: 16,777,216 \* 8 = 134,217,728B = 131072kBThe total number of bitstreams:  $\frac{131072}{306} = 428$

### 3.4 Design Considerations

Based on the available resources and resources used by the current MOLEN prototype an on-chip and off-chip Storage of re-configuration data is proposed, from now on referred to as repositories. Besides the two supported repositories, the design must be extendable to support other repositories as well.