# Rcosy DES.6392 Reconfigurable Compiler System - Rcosy Towards a Quantitative Model for Hardware/Software Partitioning.

Roeland J. Meeuws Yana Yankova Koen Bertels

Computer Engineering Laboratory

Faculty of Electrical Engineering, Mathematics, and Computer Science

Delft University of Technology

Mekelweg 4, 2628 CD Delft, The Netherlands

E-mail: {rmeeuws,yyankova,koen}@ce.et.tudelft.nl

#### Abstract

In the field of Reconfigurable computing the problem of partitioning a system in hardware and software parts has been tackled in many different ways. Our idea is to devise a quantitative model based on software metrics that are representative for different hardware characteristics. In this paper we research the different estimation and partitioning strategies currently employed in the field as a preparation for developing such a model. We determine that much research has been done on area and speed metrics, while power, memory, and communication aspects have not received much attention. Furthermore, we find that many different partitioning strategies have been developed. Many of which aim to be hill-climbing algorithms, i.e. algorithms that try to find a non-local optimum. Based on the literature we review, we conclude that estimation in a future quantitative model must have a clear notion of error and precision. Furthermore, the use of software metrics as a basis for hardware software partitioning has not been sufficiently explored. On the subject of partitioning strategies, we conclude the need for incorporating the dynamic aspect of reconfigurable computing. Furthermore, partitioning and estimation should be on the same level of granularity.

**Keywords:** Hardware/Software Partitioning, Hardware Estimation, Software Metrics, Reconfigurable Computing

## Contents

| 1 | Inti | coducti          | ion 1                                               |

|---|------|------------------|-----------------------------------------------------|

|   | 1.1  | A case           | e study: Software Radio                             |

|   | 1.2  | Recon            | figurable Computing Requirements                    |

|   | 1.3  | MOLI             | EN and Delft Workbench 4                            |

| 2 | Hig  | h Leve           | el Estimation, Metrics, and Profiling 8             |

|   | 2.1  |                  | Speed, and Power                                    |

|   |      | $2.1.1^{'}$      | Area                                                |

|   |      | 2.1.2            | Speed                                               |

|   |      | 2.1.3            |                                                     |

|   | 2.2  | Other            | metrics                                             |

|   |      | 2.2.1            | Communication                                       |

|   |      | 2.2.2            | Memory Usage                                        |

|   | 2.3  | Softwa           | are metrics and comparability                       |

|   | 2.4  |                  | fying metrics $\dots$ $\dots$ $\dots$ $\dots$ 23    |

|   |      | 2.4.1            | Dynamic vs. Static                                  |

|   |      | 2.4.2            | Level of design                                     |

|   |      | 2.4.3            | Data structures                                     |

|   |      | 2.4.4            | Strategies                                          |

|   |      | 2.4.5            | Application Domains                                 |

|   |      | 2.4.6            | Use of libraries and component models 29            |

|   |      | 2.4.7            | Granularity of Estimation                           |

|   |      | 2.4.8            | Error in estimation                                 |

|   | 2.5  | Chara            | cterizing hardware synthesis and optimization 31    |

| 3 | Har  | $\mathbf{dware}$ | /Software Partitioning 33                           |

|   | 3.1  |                  | ioning Algorithms                                   |

|   | 9    | 3.1.1            | Greedy                                              |

|   |      | 3.1.2            | Simulated Annealing                                 |

|   |      | 3.1.3            | Kernighan-Lin/Fiduccia-Mattheyses                   |

|   |      | 3.1.4            | Evolutionary or Genetic Algorithms                  |

|   |      | 3.1.5            | Global Criticality/Local Phase Driven Algorithms 38 |

|   |      | 3.1.6            | Dynamic Programming                                 |

| R | efere | nces                              | 48 |

|---|-------|-----------------------------------|----|

| 4 | Con   | nclusions                         | 46 |

|   | 3.4   | Synthesizability and Partitioning | 45 |

|   | 3.3   | Dynamic versus Static Solutions   | 43 |

|   | 3.2   | Partitioning and Estimation       | 43 |

|   |       | 3.1.8 Clustering Algorithms       | 42 |

|   |       | 3.1.7 Binary Constraint Search    | 41 |

## Chapter 1

### Introduction

For many years, computers have been based on the Von Neumann Machine (or Stored-program machine), which is a machine divided into a processing unit, a combined data and program memory for data, and a sequential flow of data and control elements between the memory and the processing unit [1]. The idea of a program of instructions that are executed sequentially made the implementation of algorithms much simpler, hence the rapid advancement of software development in the following decennia became possible.

However, as Backus [2] pointed out, the concept showed an inherent bottleneck, which he called the "Von Neumann-bottleneck". Because the processing unit and the memory in a Von Neumann-machine are separate, instructions and data have to be moved continually. Furthermore, the sequential nature of this process limits the speed one can achieve by exploiting more parallelism. Still, the Von Neumann-computer has been successful due in no small part to the many tools supporting the paradigm at each level. Moreover, the miniaturization of electronics have provided regular speed improvements (Moore's Law), diminishing the need for a non-Von Neumann architecture.

Despite the dominance of Von Neumann machines, other architectures have been used in specific areas. These application specific systems (ASICs) are able to use the parallelism inherent to the problem at hand and combine processing and storage into their data-path. In contrast to more general applications, application specific systems did not need the programmability and flexibility of the Stored-Program machine. Special languages, tools, and design methodologies have been developed to make the implementation of ASICs possible.

In recent years, the continuing applicability of Moore's Law has come into question. For one, wire delays become an increasing problem at higher speeds, and second, the manufacture of transistors smaller than a few atoms seems unlikely. Furthermore, a growing demand for mobile technology and

other systems with limited power supplies have made the use of fast Von-Neumann processors in such systems difficult if not impossible. To cope with this problem, designers increasingly use ASICs to speed up expensive algorithms like media encoding and signal processing. Such systems, where both programmable and application specific systems are combined, are called heterogeneous systems.

The problem that remains, however, is the inflexibility of such custom hardware, i.e. every different task needs a different circuit. This results in a combinatorial explosion of ASICs, driving up the cost considerably. In order to remedy this problem the research community introduced Reconfigurable Computing (RC). Reconfigurable Computing combines programmable software components with programmable hardware components [3], like FPGAs. Hence, Reconfigurable Computing advances the idea of heterogeneous systems by introducing programmability to the hardware components. These programmable hardware components make it possible to dynamically load different ASIC designs or configurations, making flexible non-Von Neumann machines a possibility. To clarify the concept of Reconfigurable Computing, let us look at [4], where three levels of programmability are identified for both control-flow models (software) and data-flow models (hardware) (Table 1.1). The programmability in Reconfigurable Computing comprises all those instances of programmability.

| Control-flow                       | Data-flow                          |

|------------------------------------|------------------------------------|

| Different programs can be executed | Different circuits can be executed |

| Executing programs can be modi-    | Executing circuits can be modified |

| fied                               |                                    |

| Dynamic behavior through choice    | Dynamic behavior through choice    |

| in control flows                   | in data flows                      |

Table 1.1: Three different levels of programmability in control-flow and data-flow systems, as presented in [4]

### 1.1 A case study: Software Radio

As an illustration of how Reconfigurable Computing can help alleviate processing requirements, while remaining flexible, we will now look into the Software Radio[5, 6, 7, 8, 9]. In mobile communications many different frequency bands are used for different applications, like GSM for voice, GPRS for Internet, and UMTS for video. To make things more complicated the exact frequencies differ per region, for example GSM at 1800MHz in Europe and Asia and GSM at 1900MHz in North America. Because of the different networks, frequencies, and bandwidths, a programmable radio that can service different networks on demand would be beneficial.

However, the computing power required for a software radio on a conventional processor are quite high. As an illustration, look at the example in [6], that mentions that processing a 500MHz carrier frequency using a 1 GHz sampling rate (as dictated by the Nyquist theorem) on a 32-bit 4-issue 4GHz system, leaves 32 operations per sample, which is not enough to filter and (de)modulate the signal, apply error correction, and so forth. [6], argues for the use of a heterogeneous multiprocessor architecture, i.e. an architecture that comprises different ASIC and General Purpose processors, to tackle this problem. Nevertheless, such an approach may be expensive. [7, 8] suggests Reconfigurable Computing (especially FPGA technology) as a means to make radio signal processing possible, while remaining flexible enough to service different networks at different times. In [8] we even find an example design: the Layered Radio Architecture.

#### 1.2 Reconfigurable Computing Requirements

Although the advantages of Reconfigurable Computing are clear, it has not pervaded industry as traditional computing has. In an attempt to explain this, [3] argues that while the Von Neumann Machine is supported by an extensive and mature base of tools, apis, and design methodologies, no such extensive support is available for the Reconfigurable Computing paradigm. In other words, for Reconfigurable Computing to be commercially applicable, it should have a comparable support base. In recent years some tools have been developed to attack this problem.

The problem doesn't end there, however. Because Reconfigurable Computing moves away from the von Neumann model, the extensive base of support should be adapted accordingly. In [10], for example, current hybrid programming models are pointed out to be immature, because FPGAs and CPUs are treated completely separate. In order to make the design of Reconfigurable Computing systems feasible the paper proposes a more transparent model, i.e. the multi-threading model. This model provides a way to describe concurrency without specifying where the thread will be implemented. A separate partitioner can then partition the threads over the hybrid processing elements. In [11] this model is elaborated in more detail. The paper describes how to implement software and hardware threads by using a common abstraction layer in the operating system, providing a common interface between hardware and software threads. Another possible programming model for reconfigurable computing is presented in [12], where a functional programming model, called V, is introduced. That model uses implicit parallelism and aims to be similar to both traditional embedded (compositional) functional models, as well as more component based models used in hardware design. Computational models need to be redefined with respect to Reconfigurable Computing as well. In [13] a redefinition of the term algorithm, as used in computability theory, is presented tailored to Reconfigurable Computing.

#### 1.3 MOLEN and Delft Workbench

Our research group has been working on reconfigurable computing for some time and we have developed a reconfigurable programming paradigm, with an accompanying platform, called the MOLEN programming paradigm [14] and the MOLEN polymorphic processor [15] respectively. The MOLEN programming paradigm features parallel hardware and concurrent hardware processes, but is intended to be sequentially consistent, i.e. the result must be the same as when the program would have been executed sequentially, and is targeted at single-program execution. As these papers mention, this paradigm has been developed to cope with 4 problems commonly associated with reconfigurable computing:

#### • Opcode space explosion

If new instructions are defined for every (every) configuration on a reconfigurable platform, a potentially unlimited amount of opcodes are needed to be able to implement a broad number of applications, however, a typical architecture has only a limited amount of unused opcodes available.

- Limitation of the number of parameters

Several reconfigurable computing approaches offer only a limited amount

of input and output parameters. The maximum amount of parallelism

that can be attained, therefore, is limited too.

- Lack of parallel execution support

Many architectures don't facilitate executing sequential data-independent

operations or configurations in parallel.

- Lack of modularity

The configurations used in reconfigurable systems are often specific to

a certain platform or technology. This makes it quite laborious and

thus expensive to port configurations to another platform.

In order to provide solutions for these problems the MOLEN programming paradigm suggests a limited instruction set extension. This extension provides instructions to load and execute configurations, a large register set for parameter passing, and the possibility to execute different configurations on the reconfigurable unit in parallel.

Loading configurations is implemented using configuration microcode, which is code that performs the actual configuration. This way different types of reconfigurable units can be configured without the need for changing the MOLEN architecture providing a much needed degree of modularity. A so-called SET operation is defined that loads the configuration microcode and initiates the configuration procedure.

When a configuration is completed the added functionality can be executed using an EXECUTE instruction. The EXECUTE instruction uses one opcode in the base opcode space and provides  $2^{(n-o)}$  (where n = no. bits per instruction, o = no. of bits per opcode) additional configured operations, addressing the problem of the opcode space explosion. The EXECUTE instruction loads an execution microcode program into the reconfigurable unit. This program is then executed using the configuration previously loaded by the SET operation. Multiple available configurations may be executed in parallel. Explicit synchronization among the core processor and the different configurations can be performed using the a special instruction (BREAK).

Before the EXECUTE instruction can commence, however, the necessary data should be provided to the register set in the MOLEN architecture responsible for parameter passing (XREGS). Therefore, instructions (MOVTX, MOVFX) for moving data between the core processor and memory on one hand and the core processor and the XREGS on the other have been added as well.

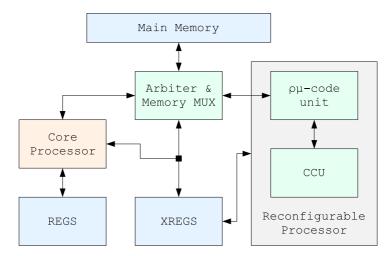

Figure 1.1: A basic overview of the general MOLEN platform.

The basic structure of the MOLEN platform is depicted in Figure 1.1. First instructions are fetched from memory and partially translated by the arbiter in order to decide whether they are redirected to the core processor or the reconfigurable unit. The reconfigurable unit comprises of a reconfigurable microcode unit or  $\rho\mu$ -code unit and a custom computing unit (CCU). The  $\rho\mu$ -code unit interprets and executes the configuration- and execution microcode, and the CCU is the actual configurable hardware part, e.g. a

#### FPGA.

We have already established the need for extensive tool support when considering the acceptance of reconfigurable computing in industry. Tool support and integration for reconfigurable computing is the main focus of the Delft Workbench project. Its research covers the entire design process from code profiling to compilation. The project has four main objectives [16]:

#### • Program Analysis and Performance Prediction

The Delft Workbench aims to identify functions in a program that might benefit the most from hardware implementation. These functions are then characterized by performance and area metrics, in order to find a set of functions with optimal increases in performance given the constrained area of the target platform. The result is a (semi-)automatic selection of a set of functions for migration to hardware.

#### • C-to-VHDL mapping

In order to implement software functions in hardware, a designer would traditionally translate them to VHDL manually. Within the Delft Workbench, effort is being made to automate this process. One example of such automation is the C-to-VHDL compiler, that is being developed. It can translate C programs or candidate functions to VHDL. A problem with such a compiler, however, is the lack of interactive design space exploration it allows. For this purpose Delft Workbench envisions a library of FPGA configurations with an accompanying performance model, which helps the designer evaluate different design alternatives.

#### • Retargetable Compiler

When a set of candidate functions is determined, the Delft Workbench provides a retargetable compiler that can compile these functions to a MOLEN architecture. Functions are translated to code for configuring the FPGA, moving the needed parameters, starting the execution, and retrieving the output. The compiler must deal with all compilation issues for the GPP as well as the added difficulties introduced by adding a reconfigurable unit.

#### • Integration and Validation

The output of the retargetable compiler can now run on a real MOLEN implementation, allowing actual performance statistics, like FPGA reconfiguration time, to be obtained. These statistics are used as feedback for the Delft Workbench tool-flow. A refined set of candidate functions and a refined schedule are determined using the feedback information. This process iterates until the designer is satisfied with

the results. The iterative nature of the process implies a tight coupling among the different tools in the tool-flow.

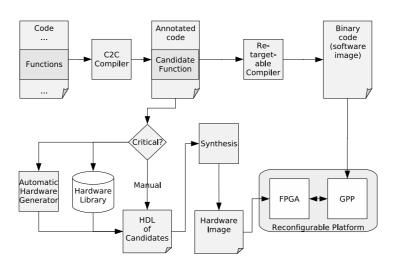

Figure 1.2: A basic overview of the general Delft Workbench tool-flow.

The Delft Workbench project focuses mainly on the MOLEN programming paradigm as its target platform. The tools and tool-flow envisioned by Delft Workbench are depicted in Figure 1.2. At the moment partitioning of a program for the MOLEN platform is still manual. The Delft Workbench project proposes a code profiler and partitioner that automate this task. The goal of this profiler/partitioner is to increase the speed of the application, while staying within the bounds on the limited area of the reconfigurable unit. In order to decide where parts of a program should reside, the Delft Workbench specifies the need for a decision model based on metrics collected during profiling.

Currently, no such model exists. Therefore, in order to develop such a model this paper investigates different metrics, estimation strategies, partitioning models, and partitioning strategies. The paper is organized as follows. In Section 2 I will discuss metrics that indicate hardware aspects of a (part of a) program and estimation techniques to determine them. Then, in Section 3 I will review hardware/software partitioning models and strategies. Finally, in Section 4 I will briefly discuss the results presented in this paper and indicate possible elements for the decision model to be used in the code profiler/partitioner in Delft Workbench.

### Chapter 2

## High Level Estimation, Metrics, and Profiling

Estimation of different cost parameters has always been an important activity in high level system design. Estimates of e.g. speed, area, or power inform a designer about whether a design will meet requirements, stay within budget, and so forth, thus driving further design choices. Not only cost parameters can be important measures to a designer, others, like loop frequency or data reference locality, might help direct the design process as well. Many tools and algorithms have been developed over the years that help determine metrics and thus make the job of the designer easier. If we go one step further and model the process of selecting candidates for hardware implementation, we need to look at the measures and their meaning. In this section we will discuss different metrics and techniques to estimate them. First I will briefly present the different papers I reviewed. Then, I will review different aspects of the estimation schemes by finding ways to classify these metrics. Furthermore, we will briefly go into synthesis and optimization and how we may measure its effects.

### 2.1 Area, Speed, and Power

Most work in estimation has focused on area, speed-up, and power, probably because they directly correspond with the cost and obvious requirements of designs. We will discuss them here first, before we go on to less obvious areas of estimation.

#### 2.1.1 Area

Area estimation has been tackled in various ways by different groups. In [24] a lower bound on area is estimated under certain performance constraints. Specifically, they estimated the number of modules of each type and the area

| Paper | Dynamic/<br>static | Level of<br>design    | Application<br>Domain                                                                      | Data<br>structure                           | Node<br>model                          | Granularity        | Strategy                  | Complexity               | Error                                                   |

|-------|--------------------|-----------------------|--------------------------------------------------------------------------------------------|---------------------------------------------|----------------------------------------|--------------------|---------------------------|--------------------------|---------------------------------------------------------|

| [17]  | Static             | Behavioral            | Multimedia                                                                                 | CDFG                                        | multiple<br>(non-<br>)linear<br>models | Entire<br>Graph    | Hierarchical              | linear                   | 2.5%-10%                                                |

| [18]  | Static             | Behavioral            | Communication                                                                              | Custom                                      | n/a                                    | Functions          | Incremental               | O(1) per iteration       | about 7%                                                |

| [19]  | Static             | Behavioral            | Multimedia                                                                                 | CDFG                                        | Bit-width<br>based                     | Entire<br>Graph    | Neural                    | nonlinear                | 10% large<br>error with<br>badly<br>trained<br>networks |

| [20]  | Static             | System/<br>Behavioral | Multimedia,<br>Mathemati-<br>cal                                                           | VHDL Ab-<br>stract Syn-<br>tax Tree         | Bit-width<br>based                     | Entire Application | Scheduling                | nonlinear                | 16%                                                     |

| [21]  | Static             | Behavioral            | Multimedia,<br>General<br>Purpose                                                          | PACT<br>HDL Ab-<br>stract<br>Syntax<br>Tree | Simple                                 | Entire Application | scheduling,<br>allocation | nonlinear                | average 25%<br>(maximum<br>of 241%)                     |

| [22]  | Static             | RTL and<br>lower      | n/a                                                                                        | Boolean<br>expres-<br>sions                 | n/a                                    | n/a                | Complexity                | linear                   | within<br>56%                                           |

| [23]  | Static             | Behavioral            | Multimedia,<br>Compression,<br>Mathemati-<br>cal, General<br>Purpose,<br>Cryptogra-<br>phy | CDFG                                        | unknown                                | Entire<br>Graph    | Hierarchical              | linear                   | 60–100%                                                 |

| [24]  | Static             | Behavioral            | Multimedia                                                                                 | DFG                                         | Simple                                 | Entire<br>Graph    | Scheduling                | $O(nc^2)$                | n/a                                                     |

| [25]  | Static             | Behavioral            | n/a                                                                                        | (annotated)<br>CDFG                         | Simple                                 | Entire<br>Graph    | scheduling                | $O(speedest.) + O(n^2)$  | n/a                                                     |

| [26]  | Static             | Behavioral            | Cryptography                                                                               | n/a                                         | Simple                                 | n/a                | Hierarchical              | n/a                      | n/a                                                     |

| [27]  | Static             | System/<br>Behavioral | Multimedia                                                                                 | H-CDFG                                      | Simple                                 | Entire<br>Graph    | Hierarchical              | $O(n \log n)$            | n/a                                                     |

| [28]  | Static             | Behavioral            | Multimedia,<br>General<br>Purpose                                                          | (C)DFG                                      | Simple                                 | Node clus-<br>ters | Hierarchical              | linear                   | n/a                                                     |

| [29]  | Dynamic            | System                | Communication                                                                              | (annotated)<br>DFG                          | Bit-width<br>based                     | Entire<br>Graph    | Scheduling                | $O(simulation) + O(n^2)$ | n/a                                                     |

Table 2.1: Different classifications of area estimation found in several papers and indications of estimation error in those papers. For an explanation of the classifications, please refer to Section 2.4.

needed for interconnect. The paper explains how lower bound estimates can be determined by scheduling a DFG and accounting for the minimum number of modules and busses required.

Because area estimation tries to predict the results of synthesis tools, [21] tries to find estimates by mimicking high level synthesis. Techniques like force directed scheduling, resource allocation, operation assignment, and interconnection binding, all come from high level synthesis. The algorithm uses a simplified model of an FPGA only taking into account standard LUTs and multiplexers as interconnection structures. Furthermore, optimizations during synthesis are not taken into account. Although these simplifications make the estimation process considerably faster, they also reduce the accuracy of the result.

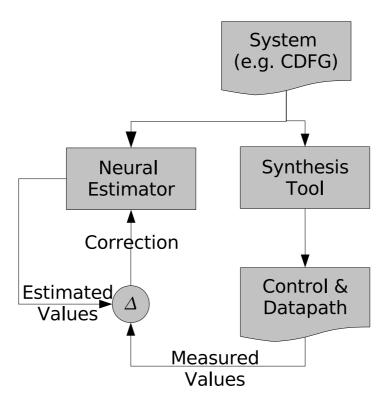

Where some area estimation techniques aim to be deterministic and are based on knowledge about synthesis, the neural estimator (NESTIMATOR)

Figure 2.1: The NESTIMATOR neural estimator from [19] working together with a synthesis tool. The results of synthesis are compared with estimates and the neural network is adapted accordingly.

in [19] takes a more non-deterministic approach. The estimator in this paper is first "teached" to correlate characteristics of a behavioral design to synthesis results by providing it with hundreds of examples. The setup is depicted in Figure 2.1. The feed-forward neural network used in this paper consists of 4 layers of neurons. The hidden layers use non-linear sigmoid neurons and the output layer uses linear neurons. The input to the neural network are several metrics characterizing CDFGs:

- Number of allowed time steps

- Maximum allowed clock period

- Average delay and area and variances of each FU type

- Number of nodes using each FU type

- Number of nodes

- Average bit-width of nodes and variance (indicates node and interconnect area)

- Average path length and variance (indicates interconnect area)

- Average number of inputs/outputs and variance (indicates interconnect and controller area)

- Average minimal and maximal lifetime of outputs and variances (indicates storage cost)

- Complexity of the CDFG (indicates parallelism)

An approach targeted specifically at partitioning algorithms is introduced in [18]. This paper describes how a preprocessed information data structure holding basic design information can be maintained between succesive iterations making it possible to get an updated estimate of the area during every new iteration of the partitioning algorithm in constant time. [30] demonstrates the usefulness of incremental estimation by integrating the technique into the COSYN algorithm.

Another approach concerning estimation during the partitioning process is defined in [25]. Here the optimal cost of a given partitioning for the minimal execution time is calculated. The optimal cost is determined by adding the costs of single nodes while accounting for the sharing of resources. Resource sharing is represented by the sharing factor which is based on the similarity between nodes. Similarity may be defined in multiple ways, but must indicate to what level nodes can share hardware.

In [23] the estimation is executed before the partitioning process and therefore tries to be independent of specific synthesis tools. Because of this,

the approach taken in this paper only takes into account the data paths. The estimates are used in a cost function in a partitioning algorithm and only need to be indicators of the actual area. This means that, although disregarding the control paths does result in a significant error, the metric can still be applied in partitioning.

As part of the fine-grained and coarse-grained partitioning strategies targeted specifically at FPGAs in [28] the authors present an area estimation approach. The partitioning strategy utilizes an area estimation algorithm that is based on summation. However, this summation handles computation area and storage area separately. This way the different logic used for storage (flip-flops) and computation(LUTs) is more accurately represented in the estimate.

| Pattern Node  | Formula            |                            |

|---------------|--------------------|----------------------------|

| type(s)       |                    |                            |

| Constant      | INPUT, OUTPUT      | y = C                      |

| Linear        | Unsigned ADD and   | $y = p_0 + p_1 n$          |

|               | SUBTRACT           |                            |

| Quadratic     | (Un)signed integer | $y = p_0 + p_1(n - p_2)^2$ |

|               | MULTIPLICATION     |                            |

| Bi-product    | (Un)signed multi-  | $y = (m - p_0)(n - p_1) +$ |

|               | input ADD and      | $p_2$                      |

|               | SUBTRACT           |                            |

| Multi-linear2 | multi-input AND or | $y = p_0 + (p_1 *)$        |

|               | OR                 | (x/2)(z/2-1)               |

Table 2.2: Bit-based area models of the main operators in LUTs, as mentioned in [17].(y=area(LUTs), n=bit-width, m=inputs,  $p_i$ = experimentally determined constants)

In an effort to guide optimizations in an SA-C compiler [17] introduced an area estimation technique that captures the impact of compiler optimizations to the area of a design. The estimator executes between the optimization and synthesis phases. Because the estimator is targeted at a specific compiler, the estimator can use detailed characterizations of the nodes in the DFG, depicted in Table 2.2. The estimate is further refined by looking for common patterns of synthesis optimization, and adjusting the estimate accordingly.

Instead of estimating the resource utilization of an entire design, some papers try to estimate the impact of specific aspects of a design. In [31], for example, we encounter a way to estimate the effect of loop unrolling on the area. The approach models pipelining and full- and partial unrolling of loops and this way accounts for an increase of the number operators and coarser

grain array indexing. The paper mentions that unrolling of outer loops, loop strip-mining, loop merging, and optimizing loop-unrolling side-effects should be investigated to make the estimation more accurate.

A narrower approach focusing only on boolean functions is presented in [22]. It demonstrates the use of a complexity measure in estimating the area of high level descriptions. This complexity measure is based on the sizes and probabilities of prime implicants in the on-set of boolean functions and shows an exponential relation with the area needed to implement the functions. This relationship is the basis for the area estimation in this paper.

Estimating area specifically from software oriented languages like C or Matlab has been covered in several papers. The researchers in [26] tried to base the area estimation on extracting relevant operations from the source code, matching modules from a library to the operations, and use timing information to find out where resources can be shared. The accuracy of this approach was somewhat disappointing, because

- the authors of [26] did not use the impact of the control logic in the area estimation

- the approach did not account for optimizations

- the algorithm needs the C description to have a hierarchy close to the hierarchy of the final design.

Using Matlab specifications as a starting point [29] uses simulation to obtain execution traces that drive the estimation process. The traces are used to build a DFG of the program. Together with an FPGA performance model that determines the characteristics of specific operations based on bit-width and clock speed, the DFG is used to estimate the area required by the Matlab code. The authors have chosen to use an area/latency grid to schedule the DFG before estimation. Using this approach they try to account for resource sharing and area constraints at the same time.

As a part of the research around the MATCH Compiler [32] the authors of [20] present an area estimator to provide the compiler with information for automatic design space exploration. The estimation comprises counting all operations and registers and uses a simple heuristic formula (Equation (2.1)) to calculate the number of CLBs that is needed for a design.

$$N_{CLBs} = 1.15 * max(N_f/2, N_r)$$

(2.1)

$N_f$ : # of function generators

$N_r$ : # of registers

The algorithm uses a library to count the number of function generators used by the operations. To get more accurate estimates. the paper describes a type refinement pass, which determines the bit—widths needed for each variable and operation before estimation.

The authors of [27] introduced an estimation technique where an entire trade-off curve is calculated. Their algorithm uses H-CDFGs, which are CDFGs with other CDFGs as nodes. From the bottom levels of the H-CDFG up, the CDFGs are scheduled and resources are allocated using different time constraint values. Calculation of the total number of required resources of multiple CDFGs is based on several heuristic and deterministic summation rules that account for resource sharing.

#### 2.1.2 Speed

In order to get an approximation of the performance of a design, the research community has proposed many ways of estimating latency and speed—up. Performance measures like these can indicate if a design is within performance constraints and can drive hardware/software partitioning.

An example of latency estimation can be found in [24] for example. Apart from estimating area, this paper also presents a way to calculate a lower bound on latency given certain resource constraints. The lower bound is based on the critical path latency and depending on the resource constraints is increased by the extra delay of every module on the critical path due to module constraints.

In [25] the latency of a hybrid hardware/software system is estimated by determining the critical path of a Co-design graph as defined in the same paper. The Co-design graph is a task graph with annotated nodes and edges. For latency estimation the nodes are annotated with latency information and for edges the graph records whether they are software or hardware edges and whether they indicate a control or a data dependency. The critical path is then determined by finding the longest path in the task graph.

As with area [27] tries to estimate entire trade-off curves for the latency of a design using different timing constraints. Again the H-CDFGs are traversed in a bottom-up fashion and the latency is calculated at every level by accounting for the allocated resources due to the timing constraints.

The COSYN [30] and CRUSADE [36] co-synthesis algorithms estimate finish times of tasks with the longest path algorithm. Described in [30] the algorithm finds the longest path in a DAG taking in to respect both the execution and communication times of tasks and links respectively.

The partitioning algorithms in [28] discussed earlier, also estimate latency by first determining the longest path. This preliminary value is then

| Paper | Dynamic/<br>static | Level of<br>Design                       | Application<br>Domain                                                     | Data<br>structure                   | Node<br>model      | Granularity                        | Strategy                                               | Complexity                | Error |

|-------|--------------------|------------------------------------------|---------------------------------------------------------------------------|-------------------------------------|--------------------|------------------------------------|--------------------------------------------------------|---------------------------|-------|

| [33]  | Static             | Instruction-<br>level                    | n/a                                                                       | Intermediate code                   | n/a                | Application                        | Complexity                                             | n/a                       | 8%    |

| [29]  | Dynamic            | System                                   | Communicatio                                                              | (annotated)<br>DFG                  | Bit-width<br>based | Entire<br>graph                    | Scheduling                                             | O(simulation nonlinear    | 10%   |

| [20]  | Static             | System/<br>Behavioral                    | Multimedia,<br>Mathemati-<br>cal                                          | VHDL Ab-<br>stract Syn-<br>tax Tree | Bit-width<br>based | Entire<br>Graph                    | Scheduling                                             | linear                    | 13%   |

| [24]  | Static             | Behavioral                               | Multimedia                                                                | DFG                                 | Simple             | entire graph                       | Scheduling                                             | $O(nc^2)$ (c: time steps) | n/a   |

| [34]  | Dynamic            | Behavioral                               | Multimedia,<br>Cryptogra-<br>phy, Com-<br>pression,<br>General<br>Purpose | n/a                                 | n/a                | Loops                              | Simulation                                             | O(simulation O(1))        | n/a   |

| [25]  | Static             | Behavioral<br>(during par-<br>titioning) | n/a                                                                       | (annotated)<br>DFG                  | Simple             | entire graph                       | Scheduling                                             | $O(n^2 \log n)$           | n/a   |

| [35]  | Static             | Behavioral                               | Communicatio                                                              | n/a                                 | Bit-width<br>based | Functions<br>(=Occam<br>processes) | Complexity                                             | n/a                       | n/a   |

| [30]  | Static             | Behavioral<br>(during par-<br>titioning) | n/a                                                                       | Task graph                          | Simple             | Entire<br>graph                    | Incremental                                            | linear                    | n/a   |

| [36]  | Static             | Behavioral<br>(during par-<br>titioning) | Communicatio                                                              | Task graph                          | Simple             | Entire<br>graph                    | Scheduling                                             | linear                    | n/a   |

| [27]  | Static             | System/<br>Behavioral                    | Multimedia                                                                | H-CDFG                              | Simple             | Entire<br>Graph                    | Hierarchical,<br>Allocation<br>(bipartite<br>matching) | $O(n \log n)$             | n/a   |

| [28]  | Static             | Behavioral<br>(during par-<br>titioning) | Multimedia,<br>General<br>Purpose                                         | (C) DFG                             | Simple             | Node clus-<br>ters                 | Scheduling                                             | n/a                       | n/a   |

| [37]  | Dynamic            | Behavioral                               | Multimedia,<br>Cryptog-<br>raphy,<br>General<br>Purpose                   | Hierarchical<br>Loop<br>Graphs      | n/a                | Loops                              | Simulation                                             | O(simulation O(1))        | n/a   |

| [21]  | Static             | Behavioral                               | Multimedia,<br>General<br>Purpose                                         | PACT HDL<br>Abstract<br>Syntax Tree | Simple             | Entire<br>Graph                    | Scheduling                                             | nonlinear                 | n/a   |

Table 2.3: Different classifications of speed estimation found in several papers and indications of estimation error in those papers. For an explanation of the classifications, please refer to Section 2.4.

refined by adding the latency of moving input and output values from and to memory, the latency of transferring data over partition boundaries, and the latency due to synchronization between tasks.

Area estimation from Matlab code as presented in [29, 20] was already discussed in the previous section. These two papers also describe delay estimation techniques. In [29] the critical path is used as latency estimate. If area constraints introduce extra delays on the critical path, the latency estimate is changed accordingly.

The authors of [20] take a more elaborate approach. They split the delay estimation between estimating the critical path delay and the interconnection delay. The delay of single tasks on the critical path are not retrieved from a normal library, but are calculated using generic delay formulas describing functional units and using fan—in and bit width as inputs. Libraries can become more compact this way. In general the paper models the delay

of an operation with Equation (2.2).

$$\delta = a + bn_{fan-in} + \sum_{i=0}^{i=n_{fan-in}} c_i m_i \tag{2.2}$$

$m_i$ : bit-width of input i $n_{fan-in}$ : number of inputs

$a, b, c_i$ : experimentally determined constants

Using estimates for average interconnection length and physical FPGA wire lengths, the algorithm determines the average number of physical wires and programmable interconnect points and therefore the average interconnection delay.

Instead of determining a value for the latency of a design, papers [34, 37] use a temporal profile of a software program to determine the maximum speed-up that can be obtained by moving certain parts of the program to hardware. The more a function, for example, contributes to the total execution time of a program, the larger the potential speed-up when it is moved to hardware. However, [34] mentions that based on the examined programs a) almost 100% of the candidates for hardware implementation contribute 1% or less to the total execution time and b) memory access time and memory access rate have a significant impact on the performance gain that can be achieved. [37], on the other hand, puts the former comment in perspective by pointing at the 90-10 rule, which states that 90% of the execution time is spent in 10% of the code. It goes on to examine the validity of this rule and concludes that many application do indeed exhibit this behavior. Finally the paper presents a simple formula to calculate the expected speed up of partial hardware implementation based on loop frequency.

In an attempt to define a performance measure that makes it possible to compare hardware and software performance during Co-simulation, [35] describes using the CPI of OCCAM-II to indicate performance. The paper describes how to calculate the CPI for software-bound processes and how hardware-bound processes can be characterized by a so-called equivalent CPI. Both measures use a parameter that depends on the architecture, compiler, synthesis tool, and scheduling policy. These measures have to be determined for every new architecture that needs to be simulated. The hardware measure utilizes bit-based operator models to estimate timing characteristics. The models of the main operators is depicted in Table 2.4.

The algorithm in [21] measures the speed-up of a design by counting the number of control steps that are present in the control nodes in a CDFG and the number of times they are executed. Then it applies different formulas for hardware and software to obtain the execution times of both implementation alternatives. Simply dividing these yields the speed-up factor.

| Operation | Architecture           | $f(\delta, n)$                    |  |  |

|-----------|------------------------|-----------------------------------|--|--|

| +         | Ripple carry           | $2n\delta$                        |  |  |

| +         | $\mathrm{CCLA}(n/p^2)$ | $if(n=1)11\delta$                 |  |  |

|           | p = BCLA dimension     | else                              |  |  |

|           |                        | $11\delta(10 + \log p(1 +  $      |  |  |

|           |                        | n(n/4-1))(n/4+1)                  |  |  |

| *         | Baugh Wooley           | if $(n=1)2\delta$ else $4n\delta$ |  |  |

| *         | Bisection              | if $(n=1)2\delta$ else $4n\delta$ |  |  |

| /         | Restoring (Dean)       | $(3n^2+1)\delta$                  |  |  |

| /         | Non-Restoring (Guild)  | $3(n+1)^2\delta$                  |  |  |

| /         | Non-Restoring with     | $(11n+12)\delta$                  |  |  |

|           | 2-level CLA and        |                                   |  |  |

|           | Carry-save (Cappa-     |                                   |  |  |

|           | Hamacher)              |                                   |  |  |

| /         | Non-Restoring with     | $(9n+10)\delta$                   |  |  |

|           | 1-level CLA and        |                                   |  |  |

|           | Carry-save (Cappa-     |                                   |  |  |

|           | Hamacher)              |                                   |  |  |

Table 2.4: Bit-based timing models of the main operators as mentioned in [35].

The  $\mu$ -profiler as described in [33] uses the number of cycles gained by hardware implementation to drive the discovery and selection of custom instructions for ASIP designs. Both the decrease in computation cycles by moving a pattern in the intermediate code of an application to hardware and the frequency of that pattern contribute to the measure. The author admits this measure is crude, but argues it is useful for early discrimination between potential candidates for hardware implementation and patterns with insufficient prospect for speed gains. In the future this measure may be improved by accounting for ILP, pipelining, and other software optimizations.

One such optimization, i.e. loop unrolling, is specifically studied in [31]. We already discussed how the authors of this paper estimate area in the previous section and speed—up is handled in the same way. Results, however, show a larger discrepancy between estimates and measurements for speed—up, than for area. The authors explain how this might be caused by e.g. unbalanced pipeline stages due to resource constraints or other loop optimization side-effects and mentions that the underlying model of the algorithm should facilitate more complex algorithms that do account for these effects.

#### 2.1.3 Power

| Paper | Dynamic/<br>static                                                | Level of<br>Design | Application<br>Domain              | Data<br>structure                     | Node<br>model               | Granularity     | Strategy                                               | Complexity             | Error |

|-------|-------------------------------------------------------------------|--------------------|------------------------------------|---------------------------------------|-----------------------------|-----------------|--------------------------------------------------------|------------------------|-------|

| [38]  | Static<br>(dynamically<br>determined<br>input prob-<br>abilities) | Behavioral         | Communicatio<br>General<br>Purpose | CDFG,<br>state<br>transition<br>graph | Activity-<br>based<br>model | Entire<br>Graph | Hierarchical                                           | O(simulati $nonlinear$ | 11.8% |

| [39]  | n/a                                                               | System             | n/a                                | n/a                                   | n/a                         | n/a             | Complexity                                             | n/a                    | n/a   |

| [30]  | Static                                                            | Behavioral         | n/a                                | Task graph                            | Simple                      | Entire<br>Graph | Hierarchical                                           | linear                 | n/a   |

| [27]  | Static                                                            | System/Behav       | Multimedia                         | H-CDFG                                | Simple                      | Entire<br>Graph | Hierarchical,<br>Allocation<br>(bipartite<br>matching) | $O(n \log n)$          | n/a   |

Table 2.5: Different classifications of power estimation found in several papers and indications of estimation error in those papers. For an explanation of the classifications, please refer to Section 2.4.

In order to increase battery lifetime in mobile and embedded systems, reduce heat dissipation in high performance designs, etc. many researchers have sought to estimate the power usage during system design. In [40], for example, we find a taxonomy of several power estimation techniques at different levels. At the highest level the authors discern several design levels at which power can be estimated. For each level the authors further classified the estimation strategies as depicted in Table 2.6. The different levels in the taxonomy also correspond to the design process. At the early stages power intensive parts can be identified with system-level estimation. Later on when a behavioral description is available, instruction- and behavioral level estimation can help guide the partitioning process and optimization of software and hardware parts. Finally, before actual synthesis is performed, architectural estimation can help choose from different architectures.

The system-level partitioning algorithm in the TOSCA co-design environment [41] uses several power evaluation metrics to drive system level partitioning. In order to choose the best design alternative several metrics indicative of good power performance for different types of operating modes are proposed in [39]. The different system characterizations are:

# • Fixed Throughput Mode These systems are characterized for power by the Power to Throughput Ratio, which is the same as energy per operation. This metric is applicable to e.g. DSP applications.

# • Maximum Throughput Mode In these systems power is characterized by the Energy to Throughput Ratio. Energy and throughput, in this case, mean maximum energy per operation and maximum throughput respectively. Microprocessorbased systems are an example of these systems.

| Level           | Level Class Based on |                       |   | Pros                                                            | Cons |                                                                   |  |

|-----------------|----------------------|-----------------------|---|-----------------------------------------------------------------|------|-------------------------------------------------------------------|--|

|                 | Analytica<br>I       | Complexity            | • | requires little<br>information                                  |      | inaccurate activity<br>modeling<br>no block specific<br>estimates |  |

| Architectu      |                      | Activity              | • | block specific estimates                                        | •    | uniform distribution of capacitance                               |  |

| re              | Empirical            | Fixed Activity        | • | non-uniform<br>distribution of<br>capacitance                   | •    | disregards data<br>activity                                       |  |

|                 |                      | Activity<br>Sensitive | • | regards data activity<br>strong link to real<br>implementations | •    | n/a                                                               |  |

|                 | Static               | tic                   |   | estimates indicate<br>general trends                            | •    | no absolute accuracy                                              |  |

| Behaviour<br>al | Activity Dynamic     |                       | • | easy handling of data<br>dependencies                           |      | much slower than<br>static<br>requires input<br>specification     |  |

|                 | Instructi            | ion                   | • | applicable to CPUs and ASIPs                                    | •    | bad estimates for some instructions                               |  |

|                 | Syster               | n                     | • | can guide<br>optimization efforts<br>early on                   | •    | very low accuracy                                                 |  |

Table 2.6: Taxonomy of power estimation techniques as presented in [40].

#### • Burst Throughput Mode

Systems that only perform in bursts can be characterized by a modified *Energy to Throughput Ratio*. Energy in this case the energy during computation and the energy during idling per total number of operations. Systems with user-interaction are often in burst throughput mode.

#### • Area-Constrained Systems

Two metrics are proposed that can characterize Area-Constrained systems: The *Power by Area Product*, which allows to optimize for power, and the *Energy by Area Product*, which allows for optimization of area and power together. Many designs will have some degree of limitation for area.

Apart from presenting these metrics the paper also argues that communication between hardware and software parts contributes significantly to the power consumption of the design. When off-chip busses are involved this contribution can be even higher. In order to estimate the power used by communication from the hardware, TOSCA calculates the bus switching activity using the bus width, required bandwidth, and the encoding scheme for data and addresses.

An example of static power estimation at the behavioral level, as discussed in [40], is presented in [27], along with area and speed estimation techniques, discussed earlier. The paper estimates trade-off curves for power

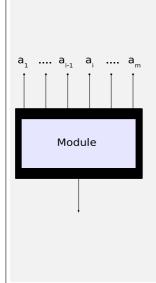

#### Switched Capacitance Matrix

The m-input n-bit module depicted on the left has a corresponding  $m \times n$  matrix of switching activities for each bit. The module capacitance can then be estimated with Equation (2.3).

$$C_{mod} = \sum_{i=1}^{m} \sum_{j=1}^{n} a_{i_j} \times c_{i_j}$$

(2.3)

$a_{ij}$  and  $c_{ij}$  are respectively the activity and a module-dependent constant for bit j of input i. The constant is determined by switch-level simulation of the module and the activity represents the probability that the bit will change between successive states.

Figure 2.2: Module power model used in [38].

consumption against varying timing constraints. The power estimation differs from the area and time estimation by taking into account the execution frequencies of functional units and the clock frequency.

The authors of [22] use the area prediction method discussed in the previous section together with estimates of the average node switching activity and gate capacitance. Problems with their approach are the need for additional estimators for switching activity and the restriction to single-output boolean functions.

The contribution of control-flow circuits to the power consumption of a system is often assumed to be negligible. This may be a fair assumption for data-flow systems, but for control-flow intensive designs this aspect must be considered during power estimation. One such approach can be found in [38]. This particular approach utilizes both STGs annotated with branch probabilities and CDFGs. Using a generic model for modules all edge capacitances are calculated using the probability of each state and each transition. Special probabilities are calculated in the presence of loops. Furthermore, the paper describes how the capacitance of the controller itself is estimated with a simple formula based on the number of states in the controller.

In the COSYN-LP algorithm [30] energy levels of tasks in a task graph are estimated by using execution and communication time as starting points. The energy level of a task is then estimated by adding the energy for all fan-

out edges and all preceding nodes to the tasks own energy level. This process starts from the bottom at the sink nodes and progresses upwards via the fan-in edges. If after partitioning multiple allocations have the same power level, an alternate estimation strategy is used, where different heuristics are used for processors, FPGAs and links.

#### 2.2 Other metrics

In Section 2.1 we discussed various methods of estimating the more obvious aspects of hardware design. In the last decade, however, other aspects like memory usage, communication, and design complexity have also been researched as possible driving forces for system design. We will now briefly review some of these metrics and their uses.

#### 2.2.1 Communication

Estimating the amount of communication is also present in some area, speed, and time estimation techniques (e.g. [24, 21, 20, 30, 39, 28]), and not without reason: communication requires interconnect circuitry, requires a fair amount of power, and introduces communication delays into the design. Therefore, accurate communication estimation can be a valuable asset to any system designer.

A more focused effort to estimate the communication latency can be found in [23]. This paper specifically estimates the communication between hardware and software segments in a hybrid system. They assume a shared memory model is used for communication between hardware and software and also that communication with hardware only occurs with adjacent hardware modules. The latter is a fair assumption in case of data-intensive designs.

Another paper on communication is [42]. In this paper we see how the amount of communication can be represented by the sum of all edge weights, or  $Total\ Edge\ Weight(TEW)$ . As edge weights the paper uses the amount of data transferred along the edges (in bits).

#### 2.2.2 Memory Usage

Few hardware-oriented memory usage estimation strategies have been proposed, but in e.g. [34], we can see that memory usage can have significant impact on the speed of a design. Furthermore, communication with the memory system and refreshing of volatile memory can impact power usage. And finally, memory modules, extra interconnect, and memory management

circuits require area. As with communication it seems clear that memory estimation can be very useful to a designer.

While many software profilers measure or characterize memory usage [39, 43, 44, 45] and some hardware/software partitioning algorithms [28, 36] take into account memory aspects of a design, to the best knowledge of the author there has been little research into memory usage in hybrid architectures.

One example of memory size estimation for hybrid architectures can be found in [46], where the size of individual data dependencies is estimated. The described algorithm focuses mainly on dependencies between loop iterations and requires single-assignment code, but it does give valuable information on memory size even in the early stages of design, when only a partially fixed execution ordering is present.

The authors of [47] point out the difficulty of hardware synthesis of programs with pointers. Traditional context-insensitive pointer analysis does not suffice. To answer this problem the paper describes a context-sensitive method of analyzing pointers in a program based on symbolic transfer functions. These functions capture how a function influences the program state. The program state and the symbolic transfer functions are represented as boolean expressions. The pointer analysis scheme presented utilizes binary decision diagrams to speed up the analysis, making context-sensitive pointer analysis feasible.

In [45] we find a study on reference locality in software programs resulting in some metrics that characterize data reference locality in a program. These metrics are based on hot data streams derived by bursty tracing [44]. Originally targeted at cache optimization on modern processors, this information may also help optimize local memory utilization in hybrid architectures or help decide whether a function can be efficiently implemented in hardware, because a function with an intensive and erratic memory access pattern might not benefit from hardware implementation at all.

#### 2.3 Software metrics and comparability

In defining a candidate selection model for hybrid architectures not only hardware metrics are important, but also software metrics. In previous sections we have already discussed software measures that may also describe hardware aspects ([45]) or may indicate code most susceptible to optimizations ([37]), but software measures also make comparisons of hardware and software implementations possible. In [48], for example, we find software energy models that enable the authors to compare different hardware / software partitions. There are some problems with such comparisons, though:

• Differences in precision

The precision of a software/hardware measure might be less accurate

than its hardware/software equivalent. This means comparisons are only as good as the least accurate measure.

#### • Differences in algorithms

Different measures are often determined using different algorithms, which makes it unclear if they are comparable in a straightforward way. Look, for example, at cyclometric complexity; it's not at all clear if software (C) and hardware (VHDL) cyclometric complexity are equivalent or comparable.

#### 2.4 Classifying metrics

Having discussed different estimation strategies and metrics for several aspects of a design we now move on to classification. In the following few sections I will discuss different aspects of the presented metrics and estimation strategies, and explore possible classifications.

#### 2.4.1 Dynamic vs. Static

One aspect of estimation strategies is whether they try to analyze a design statically, at compile-time, or dynamically, at run-time or during simulation. In the following we will refer to these as static estimation and dynamic estimation respectively.

From the papers discussed so far it seems static estimation has been dominant in the field of hardware/software partitioning and hardware synthesis. We can explain this if we take into account the many iterations partitioning algorithms may go through. If every iteration performs a potentially expensive simulation, partitioning can take a long time. This suggests that static estimation techniques aim to be fast more than they aim to be accurate.

Static estimation is also the dominant strategy in area estimation. Because area is almost always assumed to be fixed during run-time, this is only logical. When we look at hybrid architectures, however, the assumption that area is fixed during run-time does not have to apply. Future area estimation could take advantage of simulation to get dynamic area profiles.

Power estimation is often based on area estimates or area estimation techniques and thus power estimation, too, is mostly based on static estimation. In [40], however, we do find some cases of dynamic techniques like dynamic behavioral activity-based estimation (Table 2.6). Power consumption, especially that of control-intensive designs, depends on the input of an algorithm as well as the implementation itself. Therefore dynamic estimation can be useful for reasoning about power in designs.

The few dynamic estimation strategies discussed so far [34, 37, 29, 45, 40] all concentrate on speed and memory usage. These characteristics are often

dependent on the input and change during run-time. Still, hardware estimation mainly focusses on static estimation. If we look at software profiling and estimation, however, we find more dynamic techniques. It seems dynamic estimation techniques are more suitable for control-intensive designs, while static estimation is more suitable for data-intensive designs.

#### 2.4.2 Level of design

Different estimation techniques require different levels of detail in a design and have various levels of accuracy. Therefore, it is useful to categorize estimation according to the design step it is targeted at. We have already seen a similar taxonomy for power estimation techniques in [40].

It is not the aim of this paper to present an exhaustive study of system design steps, therefore we will use a simplified model of system design as a tool for discussing estimation. We discriminate three levels of design: System level, Behavioral level, and RTL/Instruction level. As can be seen from the Figures 2.1, 2.3, and 2.5, the behavioral level is the predominant level in the reviewed papers. This is mainly because the papers were selected based on their relevance to *high level* synthesis.

#### 1. System level

In the early stages of design a lot of high level decisions have to be made in a relatively short time. In order to give the designer information on different design alternatives, fast system level estimation is necessary. While, in this phase accuracy is not very important yet, estimates should be indicative of actual values. On the system level components are not yet (fully) specified using behavioral descriptions, or are modeled by a mathematical model. Papers on the MATCH compiler for Matlab models, for example, are considered to be on the system level in this view.

#### 2. Behavioral level

Later on in the design process system components will be refined with specific functional descriptions. This is the phase where many hardware/software partitioning algorithms are applied. The added detail potentially provides more accuracy in the estimates. This makes it possible to check various constraints on the design with greater certainty.

#### 3. RTL/Instruction level

After partitioning and hardware specification accurate estimation is possible for the hardware parts of the system. On the software side final estimates can be made using instruction level estimation. Estimation on these levels is often slow, because of the large amount of detail.

#### 2.4.3 Data structures

The speed and precision of estimation often depend on the data structures and the strategies that are used. Different data structures might capture different aspects of a system, or have different levels of efficiency. Traditionally, hardware synthesis has utilized data flow graphs as data structures and conversely many estimation techniques focus on these graphs. Software estimation techniques, however, are more control oriented and so use other representations like control data flow graphs and call graphs. Most literature on hardware/software estimation uses one or more of the following data structures:

#### • DFG

A Data Flow Graph (DFG) is a DAG where every node represents an operation and every edge represents a data dependency. Because there is no control information present in the DFG, the execution flow of the DFG is straight-forward and analysis is relatively easy. Many algorithms in hardware synthesis are based on these structures. The dependencies give information on which tasks can run in parallel. The absence of control information makes DFGs less suitable for representation of higher level functional specifications, like a C-program. A different term for DFG is Task Graph. These terms are often used interchangeably. Nevertheless, a DFG is often assumed to have finer grain nodes, like operations, while Task Graphs have coarser nodes, e.g. another DFG.

#### • CFG

In the traditional von-Neumann computing paradigm, an often used representation of programs during e.g. compilation or analysis is the Control Flow Graph (CFG). In this directed but cyclic graph, edges denote the transference of control from one node to the other, where nodes represent basic blocks, i.e. blocks without branches or jumps. While this graph can accurately represent the control constructs in higher level languages, its disadvantage is the single thread of control inherent to the control dependencies. This makes discovering parallelism using CFGs difficult.

#### • (H)CDFG

To account for both data and control dependencies in high level designs, the research community came up with the *Control- and Data Flow Graph* (CDFG). This graph is a data flow graph extended with control edges denoting control dependencies between nodes. Some papers utilize other representations of the control dependencies, e.g. in [49, 27] a Hierarchical CDFG or Hierarchical Sequence Graph is used, which captures control constructs as nodes in a DFG. A loop then becomes a node in a DFG, while the loop body is represented as a DFG

on a lower level. Because of the presence of loops and branches, the run-time flow through a CDFG is not known in advance and estimation becomes more difficult. High level synthesis tools often use these representations because VHDL, C, and other imperative languages make use of these control constructs.

• STG Control Intensive designs often result in a non-trivial controller circuit. The impact of such a circuit on performance characteristics, like area and power, cannot be neglected anymore. Furthermore, the power consumption and speed of the data-path can vary significantly depending on the state of the controller. In [38] a State Transition Graph (STG) is used for modeling the controller in order to estimate the power consumption of the controller and the impact of the controller on data-path power consumption. Exact metrics are hard to determine, because of the significant data-dependencies inherent to control intensive designs. Therefore state transition probabilities are determined beforehand. This way the average characteristics can be determined.

#### • Others

Apart from the (C)DFG representations, some other data-structures exist that are less common in hardware estimation. In software estimation, for example, we find Call Graphs and Abstract Syntax Trees among others (AST), among others. However, these models, like CFGs, do not always directly represent data dependencies, which makes determining parallelism inaccurate.

#### 2.4.4 Strategies

Different strategies have been proposed for different data structures and models, but some approaches are more alike then others. It can be useful to group similar estimation algorithms into categories and characterize them. This section proposes several such categories, but does not aim to be an exhaustive list, nor are the categories mutually exclusive.

#### • Scheduling

Mainly applied in speed estimation, scheduling in estimation mostly provides the timing for nodes in e.g. a DFG. After scheduling an indication of the latency of a circuit can be obtained by finding the longest path. Scheduling in estimation is borrowed from actual synthesis in order to obtain more accurate speed estimates. There are many types of scheduling algorithms, like list scheduling and force-directed scheduling. While scheduling often produces good estimates of the latency of a design, it can be time consuming (optimal scheduling is NP-complete). Note that scheduling is also used in several papers to

acquire area estimates. Indeed, when scheduling without any bounds on resources, the maximum number of used resources for each resource type define the minimum required area.

#### • Allocation

Another technique borrowed from synthesis is allocation. By actually allocating variables and operators to registers and functional units respectively, an indication of the number of resources is obtained. One such allocation strategy often found in estimation and synthesis is weighted-bipartite graph matching [50]. Matching algorithms are used in estimation to mimic resource allocation of data paths during synthesis. The idea behind this approach is to find a matching, i.e. a set of edges without common vertices, on a bipartite graph with one set of vertices representing variables (or operations), the other set of vertices representing registers (or functional units), and the edges representing possible mappings. An advantage of using synthesis-like allocation in estimation is that separate estimates for registers, functional units, and possibly interconnect can be obtained with most allocation schemes.

#### • Weighted Sum/Hierarchical

One powerful template used in many algorithms is the Hierarchical approach. In estimation this is used especially in hierarchical models. By estimating metrics on subgraphs of a CDFG, for example, the next level in the CDFG hierarchy can be estimated more quickly. A commonly used Hierarchical approach is the weighted sum approach. In this approach the system is first divided in atomic parts, i.e. components in a library. Then the weighted sum of the parts indicates the estimate of the system. Weights can represent many aspects of the component like I/O bit-width, slack, and criticality. This approach is mostly used in area and power estimation.

#### • Neural