# The TM3270 Media-processor

Jan-Willem van de Waerdt

The work described in this thesis was carried out at Philips Semiconductors, San Jose, USA.

On the front cover: Realization of the TriMedia TM3270 media-processor in a 90

nm CMOS process technology.

On the back cover: Another important tape-out in the year 2005.

CIP-gegevens Koninklijke Bibliotheek, Den Haag van de Waerdt, Jan-Willem The TM3270 Media-processor Proefschrift Technische Universiteit Delft, - Met lit. opg. ISBN 90-9021060-1

Trefw.: Media-processor, processor design

©Philips Electronics N.V. 2006

All rights are reserved.

Reproduction in whole or in part is prohibited without the written consent of the copyright owner.

# The TM3270 Media-processor

### Proefschrift

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus prof.dr.ir. J.T. Fokkema, voorzitter van het College voor Promoties, in het openbaar te verdedigen op dinsdag 10 oktober 2006 om 15:00 uur door

#### Jan-Willem VAN DE WAERDT

informatica ingenieur geboren te Maarsbergen

### Dit proefschrift is goedgekeurd door de promotor:

#### Prof.dr. S. Vassiliadis

### Samenstelling promotiecommissie:

| Rector Magnificus          | Technische Universiteit Delft, voorzitter |

|----------------------------|-------------------------------------------|

| Prof.dr. S. Vassiliadis    | Technische Universiteit Delft, promotor   |

| Prof.dr. J.E. Smith        | University of Wisconsin-Madison           |

| Prof.dr. M.J. Flynn        | Stanford University                       |

| Prof.dr. P. Stenstrom      | Chalmers University of Technology         |

| Prof.dr. T.M. Conte        | North Carolina State University           |

| Prof.dr.ir. P. Van Mieghem | Technische Universiteit Delft             |

| Prof.dr.ir. P.M. Dewilde   | Technische Universiteit Delft             |

| Prof.dr. C.I.M. Beenakker  | Technische Universiteit Delft, reservelid |

# The TM3270 Media-processor

Jan-Willem van de Waerdt

### Abstract

**T** n this thesis, we present the TM3270 VLIW media-processor, the latest of TriMedia processors, and describe the innovations with respect to its predecessor: the TM3260. We describe enhancements to the load/store unit design, such as a new data prefetching technique, and architectural enhancements, such as additions to the TriMedia Instruction Set Architecture (ISA). Examples of ISA enhancements include collapsed load operations, two-slot operations and H.264 specific CABAC decoding operations. All of the TM3270 innovations contribute to a common goal: a balanced processor design in terms of silicon area and power consumption, which enables audio and standard resolution video processing for both the connected and portable markets. To measure the speedup of the individual innovations of the TM3270 design, we evaluate processor performance on a set of complete video applications: motion estimation, MPEG2 encoding and temporal upconversion. Each of these applications have been optimized to take advantage of the TM3270 enhancements, and the associated speedups have been measured to evaluate the impact of e.g. load/store unit improvements and new operations. We show that load/store unit improvements, such as data prefetching, may improve the dynamic performance complexity (processor cycle count) by more than a factor two, for larger off-chip memory latencies. The speedup of individual ISA enhancements are measured in terms of both static (VLIW instruction count) and dynamic (processor cycle count) performance complexity, and both at the level of individual kernels and complete applications. Combined, the TM3270 enhancements result in speedups of more than a factor two, for the evaluated video applications.

# Acknowledgements

This thesis describes the TriMedia TM3270 media-processor, as designed at Philips Semiconductors in San Jose, USA. Although the TM3270 design only spans the last two years (2004-2005), the knowledge build up to enable such an activity spans the last eight years of my working career. Processor design is not a one-person activity, but a collaborative effort of a team of people, and I would like to take this opportunity to thank them.

During my working career with Philips (first at Philips Research in Eindhoven, the Netherlands, and later at Philips Semiconductors in San Jose, USA), I had the opportunity to work with a series of individuals that contributed to my development as a processor designer. I would like to explicitly mention the following people: Pieter Struik, for the initial years at Philips Research and his efforts to familiarize me with real world programming languages and UNIX tools. Paul Stravers, for the introduction to processor architecture and implementation. Especially his explanation of the difference between a latch and a flip-flop is still greatly appreciated. It was also his advice to move to Silicon Valley that contributed to my further development. Gerrit Slavenburg, father of the TriMedia architecture, for forcing me to acquire knowledge in all domains of VLIW mediaprocessor design: processor, compiler, application and real-time operating system design. Furthermore, his daily enthusiasm about our work and his drive for excellence has greatly improved the quality of the TM3270 design as described in this thesis. Stamatis Vassiliadis for his academic guidance in writing the TM3270 related conference papers and this thesis. Furthermore, I enjoyed the discussions we had on the history of processor design in general and his experiences at IBM building real world processors. I hope that this thesis reflects that processor design is more than academic architectural evaluations of imaginative machines.

As mentioned, processor design is a team effort. In the case of the TM3270 design, the processor design team collaborated with application teams and those that are responsible for the toolchain. I would like to thank those in the Philips Semiconductors application and toolchain teams for their help in defining the TM3270 processor architecture. It is your work that enables the success of this processor

in the market place. Although I can take credit for the TM3270 as chief architect and as a designer, I am thankful for the help of my colleagues in the processor design team: Dinesh Amirtharaj, Carlos Basto, Sanjeev Das, Jean-Paul van Itegem, Kulbhushan Kalra, Sebastian Mirolo, Pedro Rodrigues, Chris Yen and Bill Zhong. Without you guys, the TM3270 and its predecessors would not have seen the light of day, and would have died at a conceptual PowerPoint level.

I also thank Hans van Antwerpen, Jos van Eijndhoven and Jan Hoogerbrugge for their suggestions and the discussions we had through the years.

Jan-Willem van de Waerdt

San Jose, USA, January 2006

# Contents

| 1        | Intr      | oduction                                          | 1  |

|----------|-----------|---------------------------------------------------|----|

|          | 1.1       | Background and related work                       | 2  |

|          |           | 1.1.1 Overview of media processing platforms      | 2  |

|          |           | 1.1.2 Strengths and weaknesses                    | 5  |

|          |           | 1.1.3 Positioning media-processors and the TM3270 | 8  |

|          | 1.2       | Main contributions                                | 10 |

|          | 1.3       | Overview of the thesis                            | 11 |

|          |           | 1.3.1 Structure of the thesis                     | 11 |

|          |           | 1.3.2 Performance evaluation environment          | 12 |

| <b>2</b> | Arc       | nitecture                                         | 15 |

|          | 2.1       | TM3260 overview                                   | 17 |

|          | 2.2       | TM3270 overview                                   | 20 |

|          | 2.3       |                                                   | 21 |

|          |           | 2.3.1 Non-aligned memory access                   | 22 |

|          |           | 2.3.2 Multiplication with rounding                | 24 |

|          |           | 2.3.3 Two-slot operations                         | 25 |

|          |           | 2.3.4 Collapsed load operations                   | 27 |

|          |           |                                                   | 27 |

|          |           | 2.3.6 Potpourri                                   | 29 |

|          | 2.4       | Instruction cache LRU update                      | 30 |

|          | 2.5       | Data prefetching                                  | 33 |

|          | 2.6       | Conclusions                                       | 35 |

| 3        | Imp       | lementation 3                                     | 37 |

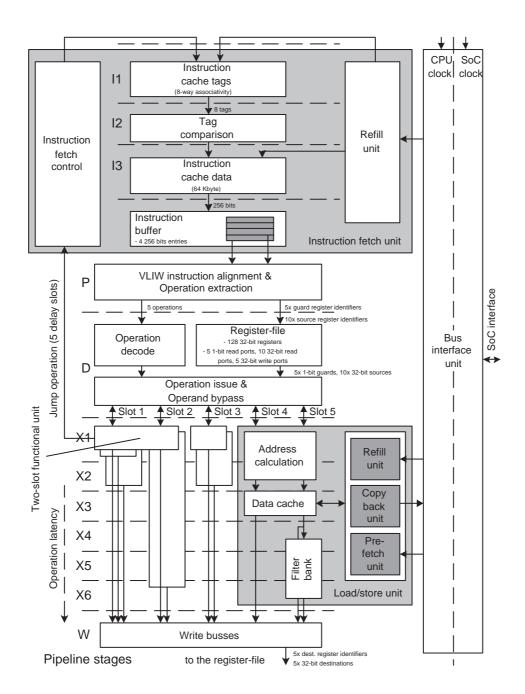

|          | $3.1^{-}$ | Processor pipeline                                | 37 |

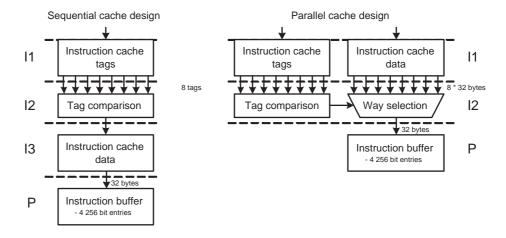

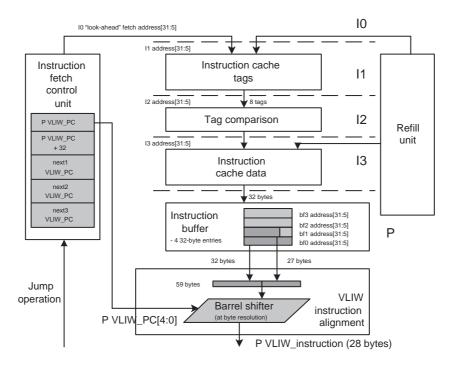

|          | 3.2       | Instruction fetch unit                            | 38 |

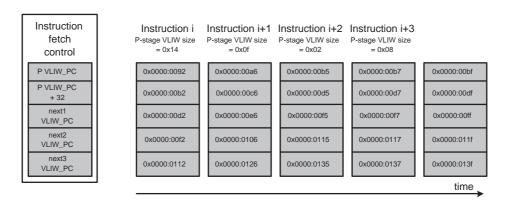

|          |           | 3.2.1 VLIW instruction encoding                   | 38 |

|          |           |                                                   | 19 |

iv Contents

|   | 3.3 | Load/store unit                     | 47        |

|---|-----|-------------------------------------|-----------|

|   |     | 3.3.1 Load/store unit pipeline      | 47        |

|   |     | 3.3.2 Memory organization           | 49        |

|   |     | 3.3.3 Memory arbitration            | 52        |

|   |     | 3.3.4 Data prefetching              | 54        |

|   | 3.4 | Conclusions                         | 56        |

| 4 | Rea | alization                           | <b>57</b> |

|   | 4.1 | CMOS realization                    | 57        |

|   | 4.2 | Power consumption                   | 60        |

|   | 4.3 | Performance                         | 64        |

|   |     | 4.3.1 MediaStone                    | 64        |

|   |     | 4.3.2 CABAC operations              | 66        |

|   | 4.4 | Conclusions                         | 68        |

| 5 | Mod | tion estimation                     | 71        |

| J | 5.1 | Description of the algorithm        | 72        |

|   | 9.1 | 5.1.1 The estimator                 | 72        |

|   |     | 5.1.2 Block-matching                | 75        |

|   | 5.2 | Block-matching implementations      | 76        |

|   | 0.2 | 5.2.1 Traditional block-matching    | 77        |

|   |     | 5.2.2 Down-sampled block-matching   | 81        |

|   |     | 5.2.3 Static performance complexity | 82        |

|   | 5.3 | Dynamic performance complexity      | 84        |

|   | 0.0 | 5.3.1 Comparing the implementations | 85        |

|   |     | 5.3.2 Memory latency                | 87        |

|   |     | 5.3.3 Data prefetching              | 88        |

|   | 5.4 | Conclusions                         | 89        |

| 6 | мр  | EG2 encoder                         | 93        |

| U | 6.1 | Description of the algorithm        | 94        |

|   | 6.2 | Motion estimator                    | 95        |

|   | 0.2 | 6.2.1 Macroblock matching           | 96        |

|   |     | 6.2.2 The estimator                 | 97        |

|   | 6.3 |                                     | 100       |

|   | 0.0 | 1 1                                 | 101       |

|   |     |                                     | 103       |

|   |     |                                     | 104       |

|   |     | •                                   | 106       |

|   |     | 9                                   | 106       |

Contents

|         |       | 6.3.6 Inverse discrete cosine transform | 107 |

|---------|-------|-----------------------------------------|-----|

|         |       | 6.3.7 Image reconstruction kernel       | 108 |

|         |       | 6.3.8 Putting it all together           | 109 |

|         | 6.4   | Bitstream generation                    | 111 |

|         | 6.5   | Dynamic performance complexity          | 113 |

|         | 6.6   | Conclusions                             | 114 |

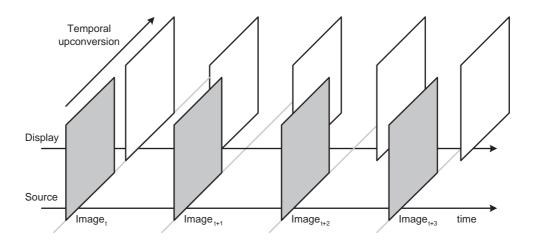

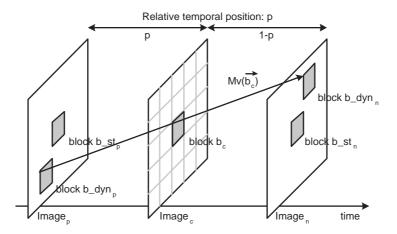

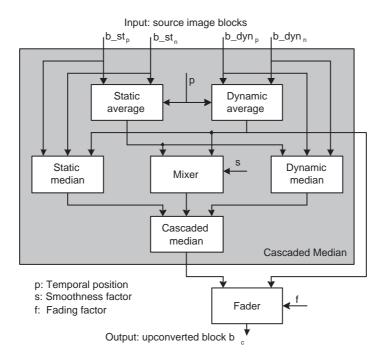

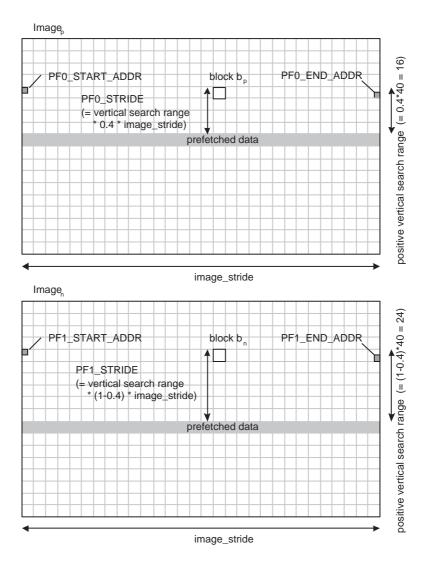

| 7       | Tem   | nporal upconversion                     | 117 |

|         | 7.1   | Description of the algorithm            | 118 |

|         | 7.2   | Implementation                          | 122 |

|         |       | 7.2.1 Six implementations               | 122 |

|         |       | 7.2.2 Static performance complexity     | 124 |

|         | 7.3   | Dynamic performance complexity          | 125 |

|         |       | 7.3.1 Comparing the implementations     | 127 |

|         |       | 7.3.2 Memory latency                    | 128 |

|         |       | 7.3.3 Data prefetching                  | 130 |

|         |       | 7.3.4 Write miss policy                 | 132 |

|         | 7.4   | Conclusions                             | 133 |

| 8       | Con   | aclusions                               | 135 |

|         | 8.1   | Summary of conclusions                  | 135 |

|         | 8.2   | Main contributions                      | 137 |

|         | 8.3   | Further research                        | 138 |

| Bi      | bliog | graphy                                  | 141 |

| ${f A}$ | New   | voperations                             | 149 |

|         | A.1   |                                         | 150 |

|         | A.2   | Two-slot operations                     | 155 |

|         | A.3   | CABAC operations                        | 162 |

| Sa      | men   | vatting                                 | 167 |

| Bi      | ograj | phy                                     | 169 |

## Chapter 1

## Introduction

Processor design has made considerable progress in the last half century. Increased circuit density allows for both higher performance integrated circuits and cheaper computers built from fewer components (as indicated by by G. Moore in [40, 41]). Furthermore, the use of CMOS process technology allows for low power implementations of these components [25].

In the cost-driven embedded consumer market, audio and video processing were initially addressed with dedicated hardware. Dedicated hardware could deliver the required performance at a lower price point than programmable processors. However, the increased complexity of audio and video standards made programmability attractive, and the increased performance of application domain specific processors made programmability a possibility. E.g., whereas video standards such as MPEG2 were initially performed by dedicated hardware, today's video standards such as H.264/AVC are performed by application (domain) specific processors [66, 20, 19]. As a result, today's consumer devices have more programmable processing capabilities than the mainframes of the 1960s. Low power processor implementations enable the application in the portable, battery-operated domain, e.g. mobile phones.

This thesis describes the design of the TM3270 media-processor, the latest processor of Philips Semiconductors' TriMedia architecture family. The TM3270 is an application domain specific processor, targeting both video and audio processing. It is intended as a programmable media-processing platform for the embedded consumer market.

The remainder of this chapter is organized as follows. Section 1.1 gives an overview of related work and provides a taxonomy of media processing platforms. Section 1.2 lists the main contribution of the thesis to the field of programmable media-processors. Section 1.3 completes this chapter with an overview of the thesis

and a description of the performance evaluation environment as used in the later chapters.

#### 1.1 Background and related work

A wide range of media processing platforms exists on which to implement video and audio processing. In this section we give an overview of these platforms, discuss their relative strengths and weaknesses and position media-processors in general and the TM3270 in particular.

#### 1.1.1 Overview of media processing platforms

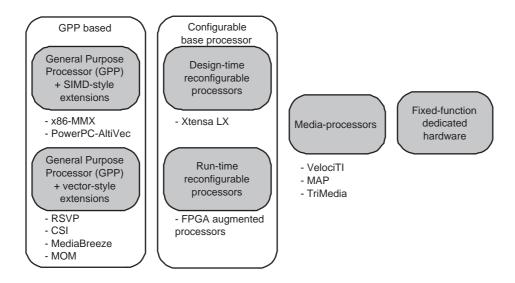

Figure 1.1 gives an overview of media processing platforms. General-Purpose Processors (GPPs), originally designed to accommodate generic program execution, have been extended with SIMD-style instructions to the instruction set architecture (ISA), to exploit intra-word parallelism (GPP+SIMD). E.g., Intel's x86 architecture family has been extended with MMX instructions [2] and IBM/Motorola's PowerPC architecture family has been extended with AltiVec instructions [12]. The SIMD-style extensions are typically generic media processing domain instructions, rather than application specific instructions targeting specific media kernels. These processors provide GPP functionality, e.g. a virtual memory management unit and user/protected modes for operating system support. However, media processing data movement support, such as non-aligned memory access and the streaming nature of media data types, is typically poorly addressed.

Multiple, mostly academic, approaches have been proposed to address the inefficient media processing data movement capabilities of the GPP+SIMD approach. These approaches extend a GPP with streaming vector capabilities (GPP+vector). The extension is tightly connected to the GPP: a single (vector) instruction sequence controls both the GPP and the vector unit. Typically, the vector unit has its own (vector) register-file, datapath and access path to data memory. The use of vector instructions, to exploit inter-word parallelism, and the support for strided memory access limits instruction fetch pressure, as many data movement instructions have become unnecessary. Examples of this approach are Motorola's reconfigurable streaming vector processor (RSVP) [7], the complex streamed instruction (CSI) set architecture from TU Delft [6] and the MediaBreeze architecture from Texas university [56]. The matrix oriented multimedia (MOM) approach from UPC in Barcelona [8] merges SIMD-style with vector-style extensions to create matrix-style instructions.

The efficiency of the GPP+vector approaches relies on a large amount of data level parallelism, regularity in memory accesses that can be expressed with stride

Figure 1.1: Media processing platforms for video and audio processing.

values and a stream-based processing of multimedia data. Whereas this may have been typical for older video codec standards, this assumption is less true for newer standards. As an example, consider the granularity at which video codecs use motion vector data. For MPEG2, a single motion vector is present for every 16x16 block of image pixels. For MPEG4, a motion vector may be present for every 8x8 block, and for H.264, a motion vector may be present for every 4x4 block. In general we can observe a decrease in block size and an increase in control overhead. Furthermore, the dependency between blocks is increasing, which limits the parallel processing of multiple blocks. E.g. for H.264, processing a 4x4 block may require that the blocks to its left and above it have already been processed. It could be stated that video codecs are getting more control intensive and offer less data level parallelism. As a result, approaches that solely rely on stream-based processing on large vectors of independent data elements become less efficient.

Rather than extending an established GPP architecture with fixed SIMD- or vector-style capabilities, processors can be extended with reconfigurable capabilities. The instruction set extensions of the GPP+SIMD and GPP+vector approaches are typically a common denominator of what is useful in the media processing domain, rather than application specific. Through reconfigurability, the extensions can be made a better fit in terms of cost and performance for a specific application. We distinguish two types of reconfigurability: design-time reconfigurability and run-time reconfigurability.

Design-time reconfigurable processors allow the user (in this case the recon-

figurable processor designer) to add application (domain) specific extensions to a base processor. An example of this approach is Tensilica's Xtensa LX configurable processor. A standard definition video decoder based on Tensilica's technology is described in [20]. To enable the required functionality, over 200 instructions were added to the ISA of the base processor. These new instructions are specific to the task of video decoding and as a result the processor's functionality is limited (additional operations need to be added to enable video encoding functionality).

Run-time reconfigurable processors allow the user (in this case the application designer) to add application (domain) specific extensions to a base processor. As opposed to design-time reconfigurability, these additions can be made after the processor has been created. In [51], a Philips Semiconductors' TriMedia processor is extended with a FPGA fabric, on which the user can implement specific instructions. In [70], the organization of a processor-FPGA hybrid design is described, including a description of the often neglected programming paradigm and compiler technology to address such a design. Other approaches limit the flexibility to a coarse grained reconfigurability, which may improve the cost efficiency of the approach. Run-time reconfigurable processors are like chameleons in the sense that they adapt their behavior to the application at hand. However, the cost of reconfigurability in terms of silicon area is likely to be higher than that of design-time reconfigurable processors.

In the 1990s, the need for an efficient programmable platform for video and audio processing led to the design of media-processors. These processors typically have a very long instruction word (VLIW) architecture to exploit instruction level parallelism [15], combined with SIMD-style instructions to exploit intra-word parallelism. Aggressive compiler technology combined with guarded execution of individual operations allows VLIW processors to extract more instruction level parallelism than traditional superscalar approaches [24, 21]. In [15], J.A. Fisher argues that through compiler techniques, such as trace scheduling, parallelism can be extracted from 100% of the code base for VLIW processors, whereas vector processing is typically applicable to only a fraction of the code base and requires hand optimization. Media-processors typically have a unified register-file for integer, floating point and SIMD-style operands, whereas GPPs typically have separate register-files. Furthermore, media-processor register-files tend to be larger than GPP register-files, such that a large data working set can be kept in registers, preventing the generation of load and store operations as a result of spilling due to register pressure. Media-processors typically support non-aligned memory access and the streaming nature of media data types through either data prefetching techniques or direct memory access (DMA) techniques [29]. Examples of mediaprocessors are Texas Instruments' VelociTI architecture family [47], Equator's MAP architecture family [1] and Philips Semiconductors' TriMedia architecture

family [43].

The last approach to be discussed in this overview is a fixed function dedicated hardware platform. This approach provides an application specific solution, without any flexibility in terms of programmability<sup>1</sup>, potentially at a lower price point than programmable approaches in terms of silicon area and power consumption. Dedicated hardware may be attractive to implement a well-defined video or audio processing task that has no need for flexibility.

One might argue that our partitioning of media processing platforms into five distinct approaches is somewhat artificial and indeed the best solution for a specific application (domain) may be a combination of approaches.

#### 1.1.2 Strengths and weaknesses

Whereas the previous section listed media processing platforms on which to implement video and audio processing, this section compares these platforms along the following axes:

- Application domain. This axis represents the width of the application domain that can be addressed with the platform.

- Cost. Cost is an important factor in the cost-driven embedded consumer market, and is a multi-facetted axis. We distinguish the development cost of the solution, the silicon area of the solution and the power consumption of the solution. Especially in the portable battery-operated market, power consumption is an important factor.

- Infrastructure. This axis takes on different forms for the different platforms. For the GPP-based and media-processor approaches it includes aspects such as the availability of toolchains (compiler, debugger), operating systems, off-the-shelf video codecs, etc. For reconfigurable processors it includes the processor development environment as offered by the reconfigurable processor company. For a dedicated hardware platform it includes the computer aided development environment.

- Performance. This axis represents the performance level that can be achieved with the approach. Performance level is measured in context of the target application. As an example, for video decoding the performance level can be expressed in terms of image resolution (e.g. CIF, standard definition, high definition).

$<sup>^1</sup>$ The dedicated hardware may have control/status registers to direct/observe its behavior from an external processor.

• *Time-to-market*. This axis expresses the speed with which an application can be introduced to the market place.

A comparison along these axes is by no means complete, but does give us the opportunity to highlight the relative strengths and weaknesses of the platforms. A choice for a specific platform will depend on the importance of the different axes for the application (domain) at hand; it is unlikely that a single approach is the best fit for all applications. The answer to the question "What is the best approach for a certain application (domain)?" is in the end defined by the success of the approach in the market place. Table 1.1 gives a summary of our perspective on the relative strengths and weaknesses, on which we elaborate in the following. Similar evaluations of media processing platforms can be found in [9, 48].

| Axis                     | GPP+SIMD | GPP+vector | Design-time reconf. | Run-time reconf. | Media-processor | Dedicated hardw. |

|--------------------------|----------|------------|---------------------|------------------|-----------------|------------------|

| Application domain       | ++       | ++         | -                   | +                | +               |                  |

| Cost - development       | ++       | ?          | -                   | -                | +               |                  |

| Cost - silicon area      |          | -          | +                   | -                | -/+             | ++               |

| Cost - power consumption |          |            | +                   | -/+              | -/+             | ++               |

| Infrastructure           | ++       | ?          | -                   | -                | +               |                  |

| Performance              | /+       | /+         | +                   | +                | -/+             | ++               |

| Time-to-market           | ++       | +          | -                   | +                | ++              |                  |

**Table 1.1:** Relative strengths and weaknesses of media processing platforms. '/' Indicates a range and '?' indicates a lack of data, as the solution has not yet been applied in the market.

Application domain. As GGPs were originally designed for general-purpose processing, it should come as no surprise that the GPP based approaches cover the widest application domain. Dedicated hardware typically offers an application specific solution. Similarly, design-time reconfigurable solutions are typically application (domain) specific (the instruction set extensions are limited to a certain application (domain)). Run-time reconfigurable solutions allow for customization of the instruction set, to adapt to new applications. Media-processors typically target the full range of video and audio processing, but are fixed after design, just like design-time reconfigurable solutions. However, their high instruction issue rate may offer enough raw computational performance to address new applications,

whereas design-time reconfigurable solutions typically have limited computational performance in application domains that are outside their original design scope.

Cost. In terms of development costs, the GPP+SIMD approach is attractive as a result of its wide application domain. Because of the market success of GPPs, it is highly likely that the required platform, including application software, exists for the target application (domain). This argument holds true, but to a lesser degree, for the media-processor approach. In terms of silicon area, dedicated hardware is to be preferred over the other approaches; unnecessary area overhead related to processor design can be eliminated for a fixed-function implementation. The GPP+SIMD approach tends to be larger than the other programmable approaches at a similar performance level, as the ISA is less specialized to a specific application domain and their media processing data movement support is limited. In terms of power consumption, the smaller approaches (in terms of silicon area) that perform the target application at a low operating frequency are preferable.

Infrastructure. Standardization is partly responsible for the market success of GPPs and media-processors. As a result, a wide range of compilers, operating systems and off-the-shelf codecs are available for these platforms, either from the processor provider or from third-party software providers. For reconfigurable processors, the user depends on the infrastructure of the reconfigurable processor provider. As these providers are not charitable institutions, the quality of their infrastructure most likely depends on the success of their solution in the market place; a reconfigurable processor company with a high-quality (costly) infrastructure but with a limited customer base is not a sustainable business in the long run. The dedicated hardware approach typically requires a "do it yourself" way of working.

Performance. Performance should be adequate to address the application (domain) at hand. Currently, this excludes some approaches for certain applications. E.g., it is unlikely that any of the programmable approaches can address the performance requirements of a high definition H.264 video encoder<sup>2</sup>. The GPP based approaches cover a relatively wide performance range: low cost solutions with limited performance and high cost solutions with more performance.

Time-to-market. The ideal solution in terms of silicon area and power consumption may be useless when it is late to the market. New markets may be best addressed with an acceptable solution that is readily available; to be later replaced by an area and power optimized solution. Time-to-market is heavily related to the width of the application domain and the quality of the infrastructure

<sup>&</sup>lt;sup>2</sup>Advances in processor design continuously improve performance levels, however, whenever a certain application becomes within reach, it is likely that a new application with higher performance requirements is introduced.

of the approach.

The relative strengths and weaknesses of the different approaches suggest that the best solution for a specific application (domain) may be a combination of approaches. As an example, consider a high definition H.264 video encoder application. Performance complexity may prohibit a programmable approach, but the standard's functional complexity may prohibit the development of a bug-free dedicated hardware implementation in a reasonable time frame. In this particular example, a combination of a programmable approach with dedicated hardware coprocessors may be a viable solution. The programmable component addresses the standard's functional complexity and the co-processors address the performance complexity of the standard's media kernels.

#### 1.1.3 Positioning media-processors and the TM3270

The TriMedia TM3270 processor is a media-processor targeting video and audio processing. Its positioning is a result of the strengths and weaknesses of the media-processor approach, as repeated in Table 1.2. The width of its application domain allows for the implementation of video, audio and general-purpose processing tasks. Its power consumption is acceptable to allow for application in the portable battery-operated market. This combination of a wide application domain and the ability to address both connected and portable markets positions the TM3270 as a standard media-processor that can rely on both Philips Semiconductors internal and external software suppliers.

| Axis                |     | Rationale                                                   |

|---------------------|-----|-------------------------------------------------------------|

| Application domain  | +   | Covers full range of video and audio processing.            |

| Cost - development  | +   | Hardware platform readily available, software potentially   |

|                     |     | available from provider or third-party software suppliers.  |

| Cost - silicon area | -/+ | Specialization for media processing (in terms of generic    |

|                     |     | media operations and data movement).                        |

| Cost - power cons.  | -/+ | Specialization for media processing makes it more efficient |

|                     |     | than a GPP+SIMD approach, but less efficient than more      |

|                     |     | application specific approaches.                            |

| Infrastructure      | +   | Standardization resulted in support in terms of compilers,  |

|                     |     | operating systems, codecs, etc.                             |

| Performance         | -/+ | Acceptable for audio and standard definition video          |

|                     |     | processing. High definition video processing may be out     |

|                     |     | of reach.                                                   |

| Time-to-market      | ++  | Hardware platform and potentially software available.       |

Table 1.2: Relative strengths and weaknesses of the TM3270 media-processor.

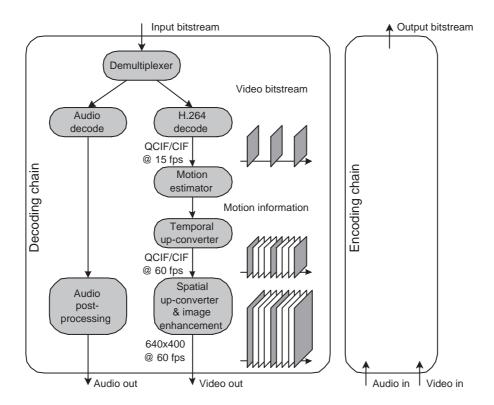

Figure 1.2 illustrates the advantage of a wide application domain. In 3G mobile

phones, the TM3270 may be used implement video telephony, performing both the video and audio processing. In the decoding chain, the TM3270 is used to demultiplex an incoming bitstream and to decode video and audio. The video decoding path starts with a H.264 decode (e.g. QCIF or CIF resolution at 15 frames/sec.). Next, a motion estimation algorithm is performed to identify object movement in the video stream. This motion information is used by a motion-compensated temporal up-converter, which adapts the frame rate of the incoming video (15 frames/sec.) to that of the phone display (e.g. 60 frames/sec.). In a last step, a spatial up-converter and image enhancement algorithm are performed to adapt the resolution of the incoming stream (QCIF or CIF) to that of the display (e.g. 640x400). The audio decoding path consists of an audio decode, which may be extended with a post-processing algorithm to enhance the sound quality. At the same time, the TM3270 is used to perform similar functionality in the encoding chain.

Figure 1.2: A possible use of the TM3270 in a 3G mobile phone.

The previous example gives an impression of the possibilities of the TM3270

media-processor. Other mobile phone design constraints such as the use of an established GPP (such as the ARM processor), power consumption and compartilization of functionality will most likely result in a partitioning of tasks over multiple processors. When considered in isolation, each of the tasks performed by the TM3270 is most likely more efficiently performed by dedicated hardware or application specific processors. However, the ability to time-share the TM3270 processor for multiple tasks make it an interesting platform in terms of silicon area and offers flexibility to address future standards [50].

#### 1.2 Main contributions

As will be described in the remainder of this section, the TM3270 media-processor design has a series of innovations that distinguish it from other media-processors. These innovations are driven by the need to address both the connected and portable markets, the need for a balanced design in terms of silicon area and performance level and the requirements of the latest video processing algorithms.

The TM3270 design provides enough performance to address the requirements of standard and some high definition video processing algorithms in the connected market, such as high-end TV sets. At the same time, its low power consumption enables successful application in portable battery-operated markets. The processor's pipeline partitioning and the design of individual units, such as the instruction fetch unit and the load/store unit, are a result of a trade-off between performance, power and silicon area.

The instruction fetch unit implements a sequential instruction cache design to limit power consumption and supports a cache line replacement policy that prevents cache trashing as a result of code sequences with limited temporal locality.

The load/store unit design provides high performance through a semi multiported cache, providing high data bandwidth to the data cache, at a limited area penalty when compared to a single-ported cache. The cache sustains a high store bandwidth by allowing two operations per VLIW instruction and a high load bandwidth by sustaining a single load operation per VLIW instruction with a bandwidth of twice the datapath size. All load and store operations support non-aligned memory access, without incurring any processor stall cycles. To our knowledge, the particular implementation of the data cache is unprecedented. Furthermore, a new data prefetching technique is introduced. From an architectural perspective the technique provides limited overhead to the programmer and from an implementation perspective it adds limited overhead to the design in terms of silicon area.

The TM3270 extends the TriMedia ISA with a series of new operations. Col-

lapsed load operations combine the functionality of a traditional load operation with that of a 2-taps filter function. These operations are particular useful to perform horizontal fractional pixel calculations in video processing algorithms. The TM3270 is the first processor in the market to support two-slot operations, which were introduced in [68]. These operations are executed by functional units that are situated in two neighboring VLIW issue slots, and as a result have twice the register-file bandwidth: two-slot operations may consume up to four 32-bit sources, and produce up to two 32-bit results. CABAC decoding operations address the specific requirements of the H.264 standard's Context-based Adaptive Binary Arithmetic Coding (CABAC) decoding process. These new operations allow the TM3270 to decode a standard definition H.264 video bitstream in real-time.

The individual innovations all contribute to a common goal: a balanced processor design in terms of silicon area and power consumption, which enables audio and standard resolution video processing for both the connected and portable markets.

#### 1.3 Overview of the thesis

The thesis can be roughly divided in three parts. The first part covers Chapters 2, 3 and 4, and describes the TM3270 media-processor design. The second part covers Chapters 5, 6 and 7, each of these chapters presents the performance evaluation of a different video application. The third part is Appendix A, which defines some of the new TM3270 operations. Section 1.3.1 briefly discusses the content of the individual chapters. Section 1.3.2 describes the performance evaluation environment that is used in Chapters 5, 6 and 7.

#### 1.3.1 Structure of the thesis

In Chapter 2 we describe the architecture of the TM3270 TriMedia media-processor. We start with the main design targets of the TM3270 and give an overview of its predecessor: the TM3260. Next, we describe those architectural functions that the TM3270 processor adds with respect to the TM3260. These additions include ISA extensions, a new cache line replacement algorithm for the instruction cache and a new data prefetching technique for the load/store unit.

Chapter 3 describes the implementation of the TM3270. Again, the focus is on those aspects of processor design that distinguish the TM3270 from its predecessor. We describe the processor pipeline and give an overview of the units that make up the processor implementation. The instruction fetch unit and load/store unit are discussed in greater detail.

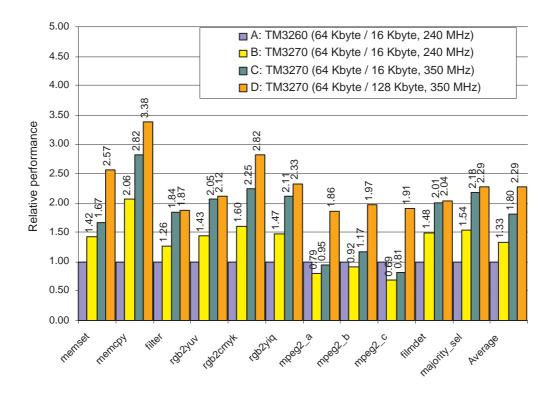

Chapter 4 describes the realization of the TM3270 in a low power CMOS process technology, with a 90 nm feature size. In particular, we describe the physical

realization (with floorplan and area data) and power consumption. Furthermore, we present performance data that compares the TM3270 to the TM3260 on a series of video processing algorithms and kernels. We also present performance data of a standard definition H.264 video decoder, and quantify the speedup of the new CABAC decoding operations (as described in Chapter 2).

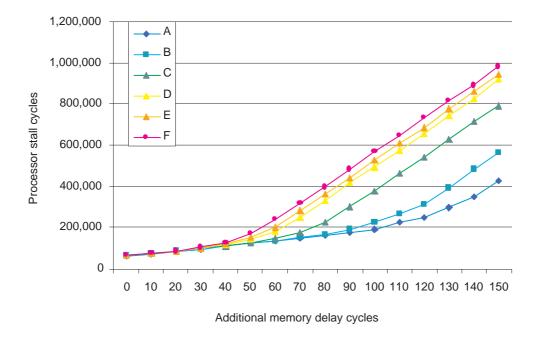

Chapter 5 evaluates the TM3270 performance on a motion estimator. Motion estimation has multiple applications; e.g. it is part of video encoders such as the MPEG2 encoder (as described in Chapter 6) and it is a prerequisite of motion-compensated temporal upconverter algorithms (as described in Chapter 7). We describe different implementations of a motion estimation algorithm that take advantage of TM3270 enhancements to the TriMedia architecture, such as new operations and non-aligned memory access. We evaluate the static performance complexity of these implementations to determine the speedup of the individual enhancements. Furthermore, we measure the dynamic performance complexity of these implementations to determine the effect of the new data prefetching technique and the sensitivity of processor performance to off-chip memory latency.

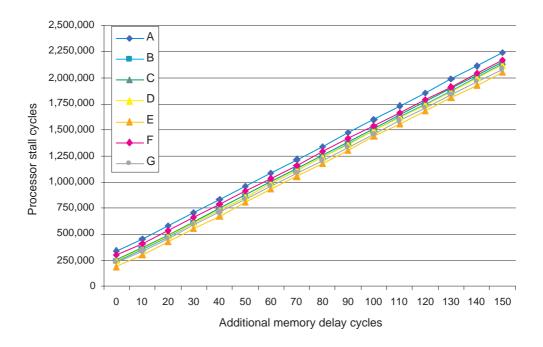

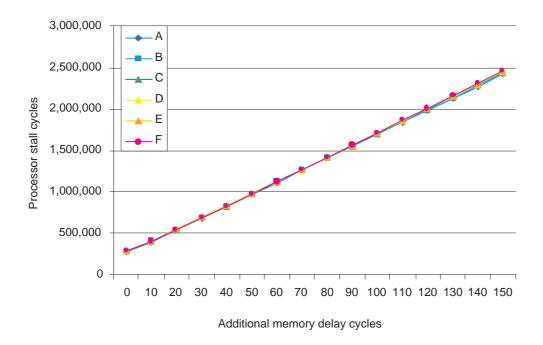

Chapter 6 evaluates the TM3270 performance on a MPEG2 video encoder. We describe how new TM3270 operations are used to speedup the individual kernels of the MPEG2 encoder texture pipeline. Furthermore, we discuss the dynamic performance complexity of the complete MPEG2 encoder, including an analysis of the sensitivity of processor performance to off-chip memory latency.

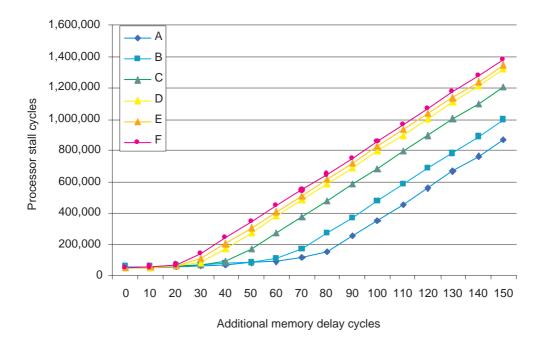

Chapter 7 evaluates the TM3270 performance on a motion-compensated temporal upconverter. We describe different implementations of the algorithm that take advantage of TM3270 enhancements to the TriMedia architecture, such as new operations and non-aligned memory access. We evaluate the static performance complexity of these implementations to determine the speedup of the individual enhancements. Furthermore, we measure the dynamic performance complexity of these implementations to determine the effect of the new data prefetching technique, data cache write miss policy and the sensitivity of processor performance to off-chip memory latency.

Finally, Chapter 8 concludes the thesis, summarizing our main contributions and findings, and proposing areas for further research.

Appendix A describes in detail the new TM3270 operations.

#### 1.3.2 Performance evaluation environment

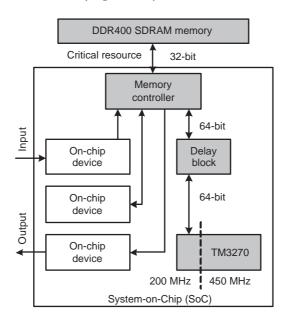

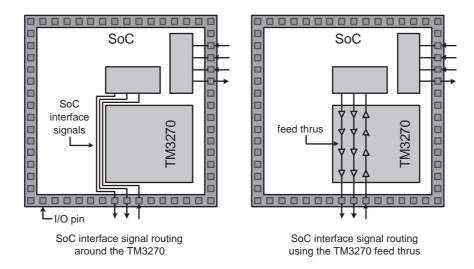

To evaluate the dynamic performance complexity (including processor stall cycles as a result of cache misses) of the video applications in Chapters 5, 6 and 7, a performance evaluation environment is used that represents realistic System-on-Chip processor behavior. Most of today's SoCs in the embedded consumer

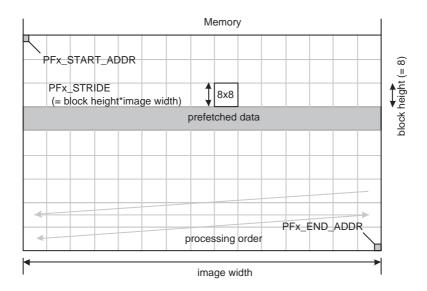

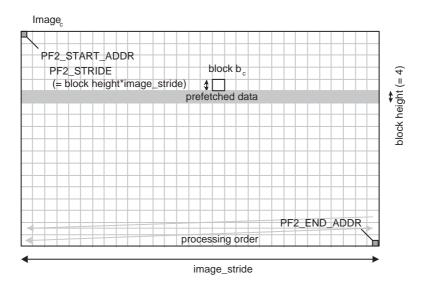

market have a unified memory architecture; i.e. the off-chip SDRAM memory is shared between the TM3270 and other on-chip devices to reduce cost. The environment consists of the TM3270 media-processor operating at 450 MHz, a 32-bit DDR SDRAM controller operating at 200 MHz and a delay block in the on-chip interconnect structure (Figure 1.3).

Figure 1.3: Performance evaluation environment.

The TM3270 Verilog HDL model is used for simulation to guarantee a 100% accurate representation of processor and cache behavior. The processor has an asynchronous clock domain transfer, which allows for independent processor and memory clock frequencies (the performance evaluations use a 450 MHz processor clock and a 200 MHz memory clock). The on-chip memory interconnect has a datapath width of 64-bit and the off-chip DDR SDRAM interconnect has a datapath width of 32-bit<sup>3</sup>. Typically, the off-chip SDRAM bandwidth is a critical resource (if it is not, cost reduction is possible by limiting the amount of SDRAM data pins or by using lower frequency (lower cost) SDRAM memories). As other on-chip devices consume more SDRAM bandwidth, the SDRAM latency as observed by the processor increases and so does the processor cache miss penalty. To mimic this behavior, a delay block is used to artificially delay memory traffic between the TM3270 and the off-chip SDRAM. By changing the delay, we can measure

$<sup>^3</sup>$ The off-chip SDRAM interconnect operates at a double data rate, effectively doubling the 32-bit data transmission frequency to 400 MHz.

the dependency of processor performance on off-chip SDRAM latency. The delay block is located in the  $200~\mathrm{MHz}$  memory clock domain: one delay cycle represents  $2.25~\mathrm{processor}$  delay cycles.

## Chapter 2

# Architecture

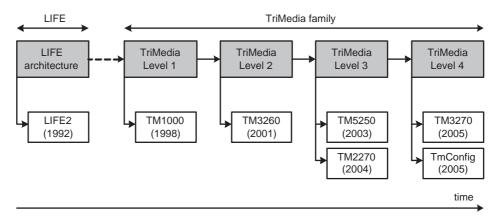

The TM3270 is a member of the Philips Semiconductors' TriMedia architecture family of media-processors [43, 46]. The architecture finds its origin in the LIFE research project, which was executed at Philips Research in Palo Alto [32, 31]. To avoid misunderstandings in this thesis, we assume the terminology and definitions of [3] as related to computer architecture, implementation and realization:

Architecture concerns the specification of the function that is provided to the programmer, such as addressing, addition, interruption, and input/output (I/O). Implementation concerns the method that is used to achieve this function, such as parallel datapath and microprogrammed control. Realization concerns the means used to materialize this method, such as electrical, magnetic, mechanical and optical devices and the powering and packaging for them. (G.A. Blaauw and F.P. Brooks jr., "Computer Architecture, Concepts and Evolution").

In this chapter, we describe the TM3270 architecture. Obviously, an architecture can have multiple implementations, and an implementation can have multiple realizations. Besides, processor architectures change over time, e.g. their most prominent function, the *Instruction Set Architecture (ISA)*, evolves to include new instructions that were deemed necessary by the architect to better address the processor application domain. Typically, architectural changes are incremental to ensure backward compatibility; i.e. programs that run on an older architecture will also run on a newer architecture of the same processor family. In the case of the TriMedia architecture family, compatibility is defined at program source-level, rather than binary-level. The transformation of program source code into binary code is assumed to be performed by a compiler/scheduler, rather than by the pro-

grammer directly. This provides us with additional freedom when implementing the processor architecture. In the spirit of Blaauw's definition of architecture, this excludes the set of compiler writers from the set of programmers; programmers work with the architecture, whereas the VLIW compiler writer requires knowledge of the architecture's implementation. The evolution of the TriMedia architecture family is illustrated in Figure 2.1. Four separate architecture levels and their processor members are identified; with each level a super-set of a lower level.

Figure 2.1: Evolution of the TriMedia architecture family.

In general, the TriMedia architecture family targets the multimedia application domain. Originally, this domain included the 3D graphics processing subdomain [14]. However, the increased computational demands of this domain has led to the design of specific graphics processors [39]. Therefore, TriMedia processors have focused on the video and audio processing subdomains. In particular, the TM3270 media-processor was designed with the following main targets (all of which impact processor architecture, implementation and realization):

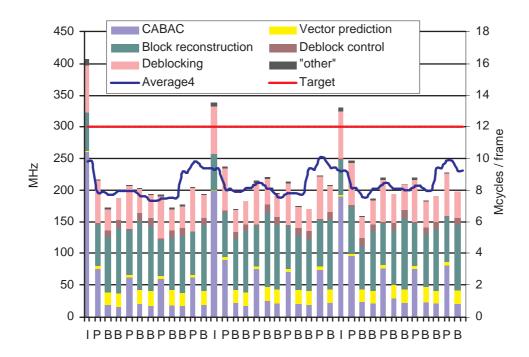

- Application domain. In line with the TriMedia architecture family, the TM3270 targets video and audio processing. With video processing being the most computationally demanding, most of the design choices are made to address video processing requirements. A specific video requirement is the ability to perform main profile H.264 decoding at main level [44] at a sustained bitrate of 2.5 Mbits/s with a maximum dynamic performance complexity of 300 MHz. This performance requirement sets a lower bound on the processor's acceptable performance level.

- Area. Consumer markets, such as the portable battery-operated, set-top box and television markets, require a low-cost realization in terms of silicon area.

- Power. The portable battery-operated market requires low power consumption to allow for longer "playing time". Indirectly, power consumption is related to cost, e.g. high power consumption may require more expensive IC packages or active cooling techniques.

- Synthesizable. To allow for cheap and fast migration of a processor implementation from one CMOS process technology to another, a synthesizable processor design is preferred.

This chapter describes the architecture of the TM3270. We found that a clean separation between architectural function and implementation method is hard to maintain. For embedded processors, implementation aspects related to performance efficiency and cache design are sometimes found to be exposed to the programmer at the architectural level. As a result, the description of some architectural functions will be related to the specific implementation method. We focus on those architectural functions that the TM3270 processor adds with respect to its predecessor: the TM3260. Section 2.1 gives an overview of the TM3260 architecture. For a complete description of the TM3260 architecture, the reader is referred to [46]. An overview of the TM3270 architecture, implementation and realization was earlier published as [66]. Section 2.2 gives an overview of the TM3270 architecture. Section 2.3 describes TM3270 ISA additions to the TriMedia architecture. Section 2.4 describes the new cache line replacement algorithm for the instruction cache. Section 2.5 describes the new data prefetching approach. Finally, Section 2.6 presents a summary and some conclusions.

#### 2.1 TM3260 overview

The TM3260 processor is the first TriMedia processor that has a fully synthesizable design. It is binary-level backward compatible with its predecessor, the TM1000, and adds 13 new operations to the ISA. Like all other TriMedia processors it is a five-issue very long instruction word (VLIW) processor. It supports a 32-bit address space (4 Gbyte of addressable memory), and has a 32-bit datapath. The processor has 128 32-bit general-purpose registers, r0, ..., r127, organized in a unified register-file structure. Register r0 always contains the integer value 0, register r1 always contains the integer value 1. The TM3260 issues one VLIW instruction every cycle. Each instruction may contain up to five operations and each of the operations may be guarded; i.e. their execution can be made conditional based on the value of the least significant bit of the operation's guard register. This allows the compiler/scheduler to perform aggressive speculation/predication to exploit parallelism in the source code [24], to achieve high processor performance.

All of the general-purpose registers can be used as guard register. The following gives an example of a VLIW instruction with five operations (operations in issue slots 1, 3, and 4 are guarded):

```

IF r7

IADD

r4 r5 -> r8,

// issue slot 1

UTMM

0x12345678 \rightarrow r13.

// issue slot 2

IF r10

FMUL

r21 r22 -> r23,

// issue slot 3

IF r30

STD32D(0) r31 r32,

// issue slot 4

LD32D(0) r41 -> r43;

// issue slot 5

```

Each operation has a fixed latency in terms of VLIW instructions, which is known by the compiler/scheduler at compile time. For example, the IADD operation has a latency of 1 instruction, thus the result of the IADD operation may be used as a source operand to an operation in the next VLIW instruction. In general, the result of an operation with latency i issued in VLIW instruction j may be used as a source operand to an operation in VLIW instruction j+i. Conditional and unconditional jump operations have 3 delay slots; i.e. when a jump is taken in VLIW instruction j, the operations in the next three sequential VLIW instructions j+1, j+2 and j+3 are executed.

Operations are executed by functional units and certain restrictions exist in how operations can be packed into a VLIW instruction. For example, load operations are executed by the load/store unit, which is only available in issue slots 4 and 5. An overview of the available functional units, their latency, and example operations is given in Table 2.1. Furthermore, no more than five results (of previously issued operations) can be written to the register-file in the same cycle. Typically, the packing of operations into VLIW instructions is not done by the programmer, but by the scheduler, which takes care of the mentioned operation restrictions.

Unlike traditional processor architectures, the TriMedia architecture only allows for special event handling (such as interrupts and exceptions) during interruptible jump operations, e.g. IJMPI. To support this event handling model, most operations either do not generate exception conditions, e.g. IADD, or set silent exception flags, e.g. FMUL or FADD. Silent exception flags and pending interrupt flags are only considered during interruptible jump operations. The limitation of special event handling to specific points in the scheduled code has several advantages. Firstly, the compiler/scheduler limits the use of general-purpose registers at these points, such that less architectural state needs to be saved before special event handling can commence. Secondly, the compiler/scheduler may perform more aggressive speculative scheduling, by ignoring the silent exception flags related to wrongly speculated operations [36].

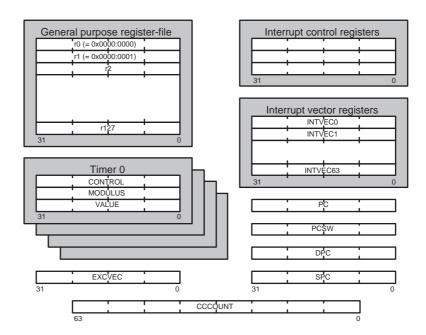

In addition to the general-purpose registers, there are special purpose registers: PC (Program Counter), PCSW (Program Control and Status Word), DPC (Des-

| Name       | Latency | Issue slots |   |   | Example operations |   |                           |

|------------|---------|-------------|---|---|--------------------|---|---------------------------|

| CONST      | 1       | 1           | 2 | 3 | 4                  | 5 | IIMM,                     |

| ALU        | 1       | 1           | 2 | 3 | 4                  | 5 | IADD, ISUB,               |

| SHIFTER    | 1       | 1           | 2 | 3 | 4                  | 5 | ASL, ASR, ROL,            |

| JUMP       | 3       |             | 2 | 3 | 4                  |   | JMPI, JMPT, IJMPI, IJMPT, |

| DSPALU     | 2       | 1           |   | 3 |                    | 5 | DSPIDUALADD,              |

| IMUL       | 3       |             | 2 | 3 |                    |   | UMUL, UMULM, DUALIMUL,    |

| FALU       | 3       | 1           |   |   | 4                  |   | FADD, FSUB,               |

| FMUL       | 3       |             | 2 | 3 |                    |   | FMUL,                     |

| FCMP       | 1       |             | 2 | 3 |                    |   | FGTR, FGEQ, FEQL,         |

| FTOUGH     | 17      |             | 2 |   |                    |   | FDIV, FSQRT,              |

| LS         | 3       |             |   |   | 4                  | 5 | ST32D, LD32D,             |

| LS_SPECIAL | -       |             |   |   |                    | 5 | DINVALID, PREF, DCB,      |

**Table 2.1:** TM3260 functional units. All functional units, except for the FTOUGH unit, are fully pipelined. The floating-point units FALU, FMUL, FCMP and FTOUGH are single precision IEEE-754 compliant.

tination Program Counter), SPC (Source Program Counter) and CCCOUNT (Clock Cycle Counter). The PC register gives the program counter of the VLIW instruction that is currently issued by the processor. The PCSW register is a selection of control fields (e.g. endianness and floating point rounding) and status fields (e.g. silent exception flags). The DPC and SPC registers are related to special event handling. The DPC register is updated during every taken interruptible jump, with the target address of the jump operation. The SPC register is updated during every taken interruptible jump that is not interrupted by a special event handler. The handler uses SPC to determine the start of a VLIW instruction sequence in which the special event occurred and uses DPC as return address to resume the program, after the special event has been taken care of by the handler. Special event handling is supported by a dedicated exception vector address EXCVEC and 64 separate interrupt vector addresses INTVECn (n = 0, 1, ..., 63). The CCCOUNT register is a 64-bit counter, which can be set to increment on either every issued VLIW instruction or every processor cycle. Furthermore, the TM3260 processor includes a series of peripherals, most notably the four 32-bit timers. An overview of the TM3260 architectural state is given in Figure 2.2.

The TM3260 has a 64 Kbyte instruction cache (8-way set-associativity, 64 byte line size and a hierarchical least-recently used replacement algorithm) and a 16 Kbyte data cache (8-way set-associativity, 64 byte line size and a hierarchical least-recently used replacement algorithm). The data cache is dual-ported; a single VLIW instruction may contain two load operations, two store operations, or one load and one store operation. The TM3260 does not support non-aligned memory access. The TM3260 does not support hardware memory coherency. It is the

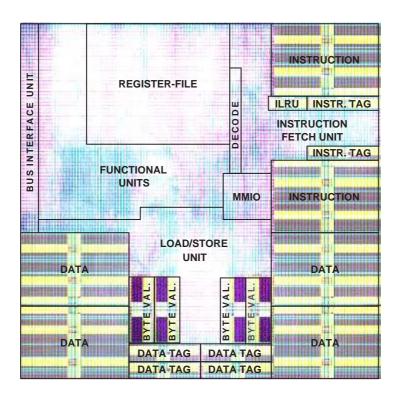

Figure 2.2: Architectural state overview of the TM3260.

responsibility of the programmer to use dedicated cache coherency operations, e.g. DINVALID (invalidate a cache line), DCB (victimize a dirty cache line), etc., to ensure SoC level coherency.

#### 2.2 TM3270 overview

The TM3270 processor is the most recent TriMedia processor. It has a fully synthesizable design and is source-level backward compatible with its predecessors. It adds several architectural features to the TriMedia architecture. This section gives an overview of the TM3270 functional units and their latencies. The following sections describe other differences and additions in greater detail. To accommodate the need for speed, the TM3270 is deeper pipelined than the TM3260. This is reflected by the longer latencies of some of the functional units and the increased jump latency (Table 2.2). E.g., multiplication and load operations have a four cycle latency, whereas the TM3260 performed these operations with a three cycle latency. Although deeper pipelining has a negative impact on the cycles / VLIW instructions ratio (CPI), it allows for a higher frequency design.

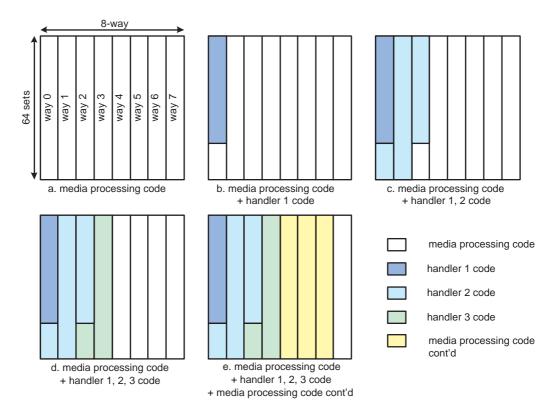

The TM3270 has a 64 Kbyte instruction cache (8-way set-associativity, 128 byte line size and a LRU replacement algorithm). To improve the instruction cache hit

| Name         | Latency |     | Iss | ue si | lots |     | Example operations        |

|--------------|---------|-----|-----|-------|------|-----|---------------------------|

| CONST        | 1       | 1   | 2   | 3     | 4    | 5   | IIMM,                     |

| ALU          | 1       | 1   | 2   | 3     | 4    | 5   | IADD, ISUB,               |

| SHIFTER      | 1       | 1   | 2   | 3     | 4    | 5   | ASL, ASR, ROL,            |

| JUMP         | 5       |     | 2   |       | 4    |     | JMPI, JMPT, IJMPI, IJMPT, |

| DSPALU       | 2       | 1   |     | 3     | 4    |     | DSPIDUALADD,              |

| IMUL         | 4       |     | 2   | 3     |      |     | UMUL, UMULM, DUALIMUL,    |

| FALU         | 4       | 1   |     |       | 4    |     | FADD, FSUB,               |

| FMUL         | 4       |     | 2   | 3     |      |     | FMUL,                     |

| FCMP         | 2       |     | 2   | 3     |      |     | FGTR, FGEQ, FEQL,         |

| FTOUGH       | 17      |     | 2   |       |      |     | FDIV, FSQRT,              |

| LS_ST        | -       |     |     |       | 4    | 5   | ST32D,                    |

| LS_LD        | 3       |     |     |       |      | 5   | LD32D,                    |

| LS_SPECIAL   | -       |     |     |       |      | 5   | DINVALID, PREF, DCB,      |

| LS_FRAC      | 6       |     |     |       |      | 5   | LD_FRAC8,                 |

| SUPER_ALU    | 1       | 1 - | + 2 | 3 -   | + 4  |     | SUPER_PACKMSBYTES,        |

| SUPER_DSPALU | 2       | 1 - | + 2 | 3 -   | + 4  |     | SUPER_DUALIMEDIAN,        |

| SUPER_IMUL   | 4       |     | 2 - | ⊦ 3   |      |     | SUPER_IFIR16,             |

| SUPER_CABAC  | 4       |     | 2 - | ⊦ 3   |      |     | SUPER_CABAC_STR,          |

| SUPER_LS_LD  | 4       |     |     |       | 4 -  | ⊦ 5 | SUPER_LD32D,              |

Table 2.2: TM3270 functional units.

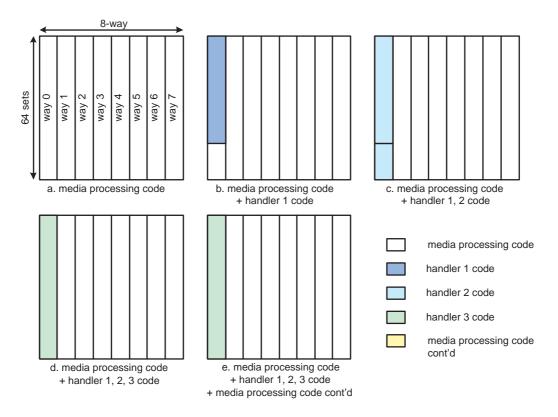

rate, the TM3270 has a full LRU replacement scheme, rather than the TM3260 hierarchical LRU scheme. The TM3270 has a 128 Kbyte data cache (4-way set-associativity, 128 byte line size and a LRU replacement algorithm). The data cache is *pseudo* dual-ported, a single VLIW instruction may contain one load operations, two store operations, or one load and one store operation. The TM3270 supports non-aligned memory access. The data cache size is increased from 16 Kbyte for the TM3260 to 128 Kbyte for the TM3270. The increased capacity is able to capture the data working set of most video algorithms operating at a standard definition (SD) resolution (NTSC: 720\*480, PAL: 720\*576). To limit the area impact associated with the increased cache size, the TM3270 data cache is pseudo dual-ported, rather than the TM3260 fully dual-ported data cache, which allows for a more area efficient implementation.

#### 2.3 ISA enhancements

The TM3270 targets video and audio processing. Given the higher computational requirements of video processing, most new operations find application in this domain. Although we investigated new operations addressing the video application domain, we do not want to end up with an ISA that is application specific; i.e. we do not intend to build an application specific processor. While identifying

potentially interesting operations, we applied certain selection rules:

- Fits the processor architecture. It is probably subjective to assign a precise meaning to the word "fits". However, this rule reflects our intention to keep the architecture as clean as possible. The ISA should have a certain consistency. We identified the following restrictions to ensure consistency:

- No operations with architectural state. This excludes e.g. the use of multipliers with accumulator values that are not transferred through operation operands.

- Operations are limited to up to two issue slots.

- Operations should support guarding.

- For SIMD operations, the operands are partitioned into sub-operand fields. The sub-operand sizes and semantics should preferably be the same.

- Reuse of available processor resources. New operations typically add functionality to the existing datapath. It is the intent to restrict the additional silicon area to a minimum, to allow for a low-cost implementation of the architecture.

- Applicability in multiple domains. This reduces the risk that one ends up with operations that provide a solution within the scope of a specific kernel, but have no applicability outside this scope.

- Significant performance enhancement. New operations should improve performance. Performance improvement should be measured at the application level, rather than the kernel level; i.e. the contribution of a kernel to the application should be taken into account.

It is the interplay of the selection rules that decides whether a new operation is useful or not; i.e. an operation that adds a significant amount of silicon area may be justified due to wide applicability and significant performance enhancement of the operation. An expert in the areas of processor architecture and video processing should preferably judge the ISA enhancement as obvious. Having set the stage for the selection of operations, some of the new operations are described in the following sections.

#### 2.3.1 Non-aligned memory access

The TM3270 supports non-aligned memory access for load and store operations that target the processor's memory aperture. The TM3260 does not support this

feature: least significant bits of a memory access address A[31:0] (bits 1 and 0 for 32-bit accesses, and bit 0 for 16-bit accesses) are discarded and the memory access is performed as if these bits were '0'. In case of address miss-alignment (A[1:0]  $\neq$  "00" for 32-bit accesses, and A[0]  $\neq$  '0' for 16-bit accesses) a silent exception status bit is set. Traditional control processor architectures, such as the MIPS architecture [28, 54], typically generate an address miss-alignment exception under this condition.

The MIPS architecture supports non-aligned memory access in software with dedicated operation, such as the LWL and LWR operations to retrieve 32-bit data elements. A non-aligned 32-bit data element is retrieved by a pair of these operations, LWL retrieves the byte elements left of the 32-bit address boundary, and LWR retrieves the byte elements right of the 32-bit address and merges these bytes with the LWL retrieved bytes. Texas Instruments' VelociTI media-processor architecture [47] supports non-aligned memory access in hardware. Normal load and store operations are used to access miss-aligned data elements. This approach eliminates the need for dedicated operations and when compared to the MIPS approach eliminates an operation to access a miss-aligned data element. However, a miss-aligned memory access may incur a stall cycle, which has a negative impact on processor performance. Similar to the VelociTI architecture, the TM3270 supports non-aligned memory access in hardware with normal load and store operations. The TM3270 does not incur any stall cycles for a miss-aligned memory access.

SIMD processing partitions operation operands into multiple sub-operands that are operated upon in a similar manner. Non-aligned memory access efficiently extends traditional SIMD computational processing, e.g. QUADADD or DUAL-MUL, to the memory access domain. Without non-aligned memory access, the potential gain of SIMD computational processing may be lost when the sub-operands that are operated upon cannot be efficiently accessed in memory. Consider a fourway 8-bit SIMD addition QUADADD of two operands, one located in processor register r2 and the other located in memory at address A. Without non-aligned memory access support, the code sequence looks like:

Whereas, with non-aligned memory access support, the code sequence looks like:

```

result = QUADADD (r2, Mem[A]); // possible miss-aligned memory access

```

Non-aligned memory access has the obvious advantage of using fewer operations, which improves processor performance. As a result of using less operations, non-aligned memory access reduces the code size and when code size is at the boundary of instruction cache capacity, a small reduction may result in a significant performance gain due to the elimination of instruction fetch unit stall cycles as a result of cache misses. Another side effect of using fewer operations is a potential reduction in register-file pressure. For code with a large amount of parallelism, high register-file pressure may result in spilling of register operands. Spill code adds additional operations to move operands between the register-file and memory, potentially degrading processor performance [73].

#### 2.3.2 Multiplication with rounding

The TriMedia architecture multiplication operations have no architectural state (such as the accumulator register employed by the MIPS architecture). Stateless multiplication simplifies the exploitation of instruction level parallelism in multi-issue processors, especially when multiple multiplications can be issued simultaneously [52]. Furthermore, limitation of architectural state simplifies context save and restore in the case of interrupt or exception handling.

Multiplications promote the data type of the source operands, e.g. when multiplying two 16-bit sources, a 32-bit result is produced. In case of two-way 16-bit SIMD multiplication, the two 32-bit results cannot be represented within a single 32-bit destination register. Multiple approaches exist to address this problem. Saturation clips the results of an arithmetic operation to a range that can be represented within the operation destination, e.g. the result of a 16x16 bit signed multiplication may be clipped to the two-complement 16-bit signed integer range of [0x8000, 0x7fff]. Truncation throws away some of the lower bits of the operation, e.g. the lower 16 bits of the result of a 16x16 bit signed multiplication may be thrown away, at a loss of precision (truncation is similar to post-normalization as employed by floating point operations). Rather than simply throwing away least significant bits from a certain "cut-off" bit position, rounding may be performed. E.g., a 16x16 bit signed multiplication with a 32-bit result of 0x1234:8765 may be truncated with rounding to a 16-bit result of 0x1235 (assuming a rounding to the nearest representable integer), rather than truncated to a 16-bit result of 0x1234. Especially for code sequences with multiplications in which the truncation error accumulates, rounding may provide the additional precision to guarantee algorithm compliancy (e.g. MPEG2 8x8 DCT/IDCT kernels).

The TM3270 adds several multiplication operations to the TriMedia ISA that support saturation, truncation and rounding. To illustrate the functionality, we

describe the DUALISCALEUI\_RNINT operation. This two-way 16-bit SIMD multiplication calculates two 16-bit signed results, each a product of a 16-bit unsigned and 16-bit signed value:

#### 2.3.3 Two-slot operations

Two-slot or super operations were first proposed in [68], but only find first employment in the TM3270. Two-slot operations are executed by functional units that are situated in two neighboring issue slots. As a result, these functional units have twice the register-file bandwidth: operations may consume up to four 32-bit sources and produce up to two 32-bit results. To illustrate the ability of two-slot operations, we describe the SUPER\_DUALIMEDIAN and SUPER\_LD32R operations.

The SUPER\_DUALIMEDIAN operation has three sources and a single destination. This two-way 16-bit SIMD operation calculates a 3-taps median filter on two-way 16-bit signed inputs:

Without the new operation, two DUALIMIN and two DUALIMAX operations are required to implement the same functionality (both operations are available in the TriMedia ISA). This implementation occupies four issue slots, whereas the two-slot operation occupies only two issue slots, a reduction of a factor two. Furthermore, the SUPER\_DUALIMEDIAN, DUALIMIN and DUALIMAX operations all have a latency of two cycles. The DUALIMIN and DUALIMAX implementation has a compound latency of six cycles, whereas the two-slot operation has a latency of two cycles, a reduction of a factor three. As the 3-taps median filter is a basic building block of many video algorithms, e.g. the temporal upconversion algorithm (Chapter 7), performance is significantly improved when the SUPER\_DUALIMEDIAN operation is used.

The SUPER\_LD32R operation has two sources and two destinations. The operation retrieves two consecutive 32-bit values from memory:

```

SUPER_LD32R src3 src4 -> dst1 dst2

A = src3+src4;  // calculate the memory address dst1[31:24] = Mem[A];  // big endian mode assumed dst1[23:16] = Mem[A+1]; dst1[15:8] = Mem[A+2]; dst1[7:0] = Mem[A+3]; dst2[31:24] = Mem[A+4]; dst2[23:16] = Mem[A+5]; dst2[15:8] = Mem[A+6]; dst2[7:0] = Mem[A+7];

```

The source operands are taken from the second operation in the operation pair, which explains why sources src3 and src4, rather than sources src1 and src2 are used, to calculate the memory address<sup>1</sup>. The new operation doubles the load bandwidth, when compared to a traditional LD32R operation. The restriction to consecutive memory address locations limits the applicability of the new operation, when compared to two separate LD32R operations. However, the SUPER\_LD32R is efficiently supported by the TM3270 data cache organization, whereas the support for two separate LD32R operations would be more expensive or would produce more unpredictable execution behavior [45]. Texas Instruments' VelociTI architecture includes a similar load operation: LDDW, it also loads two 32-bit values from consecutive memory addresses [49]. However, its destination

<sup>&</sup>lt;sup>1</sup>The rationale for this decision is given in Section 3.3.1

registers are restricted to a neighboring register pair, which limits the freedom of the scheduler's register allocator.

### 2.3.4 Collapsed load operations

Collapsed load operations with interpolation combine the functionality of a load operation, with that of a 2-taps filter function. Collapsed load operations [59] are a new type of operations that involves memory collapsing rather than the ALU collapsing presented in [69]. To illustrate the ability of collapsed load operations, we describe the LD\_FRAC8 operation:

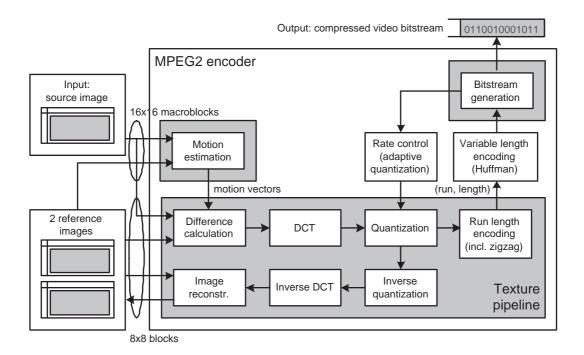

The operation retrieves five bytes from consecutive memory addresses, and performs a 2-taps filter function on neighboring bytes to produce a four-way 8-bit SIMD result. Note that a more traditional 32-bit architecture requires two loads to retrieve the five bytes and potentially multiple operations to perform the filter function. The LD\_FRAC8 operation allows for efficient implementation of horizontal fractional 8-bit pixel calculation. This function is a basic building block of motion estimation (Chapter 5), which constitutes a significant computational part of video encoders, such as MPEG2 (Chapter 6) and H.264/AVC [44].

### 2.3.5 CABAC operations

Context-based Adaptive Binary Arithmetic Coding (CABAC) [38, 23] constitutes a significant part of a H.264/AVC video decoder [44, 72]. The intrinsic sequential behavior of the CABAC decoding process prohibits an efficient implementation on a multi-issue processor. Performance evaluations of a decoder indicated that as much as 50% of the overall decoding time may be spent in the CABAC process, when no specific operation support for CABAC decoding is provided (Section 4.3.2). The TM3270 adds specific CABAC operations to the TriMedia ISA to reduce these computational requirements [62, 66]. The following code sequence gives the definition of biari\_decode\_symbol function, which decodes a single binary value bit from a CABAC coded bitstream:

```

LpsRangeTable[64][4]

// range table for least probable symbol (LPS)

MpsNextStateTable[64]

// MPS state transition table

LpsNextStateTable[64]

// LPS state transition table

biari_decode_symbol ( // decodes a single binary value "bit" from the CABAC coded stream

inout value,

// coding value, 10-bit value

inout range,

// coding range, 9-bit value

inout state,

// modeling context state, 6-bit

// modeling context MPS, 1-bit

inout mps,

in stream_data,

// bitstream data

inout stream_bit_position, // bit position in "stream_data"

// decoded binary value

out bit)

stream_data_aligned = stream_data << stream_bit_position;</pre>

= LpsRangeTable[state][(range >> 6) & 3)];

range_lps

temp_range

= range - range_lps

if (value < temp_range) {</pre>

// MPS: most probable symbol

value = value;

range = temp_range;

bit = mps;

= mps;

state = MpsNextStateTable[state];

mps

} else {

// LPS: least probable symbol

value = value - temp_range; range = range_lps;

bit = !mps;

mps = mps ^ (state != 0); state = LpsNextStateTable[state];

while (range < 256) { // renormalization, at most 8 bits can be consumed

value

(value << 1)

| ((stream_data_aligned >> 31) & 1);

range

<<= 1:

stream_data_aligned <<= 1;

stream_bit_position += 1;

}

```

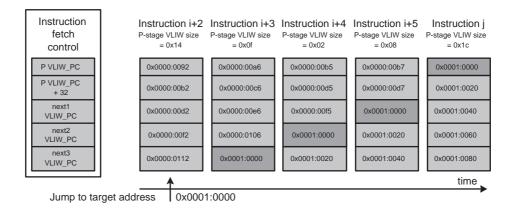

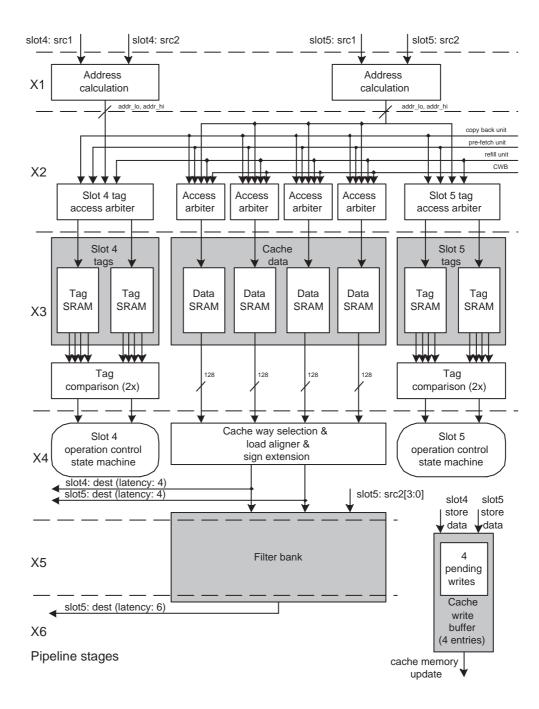

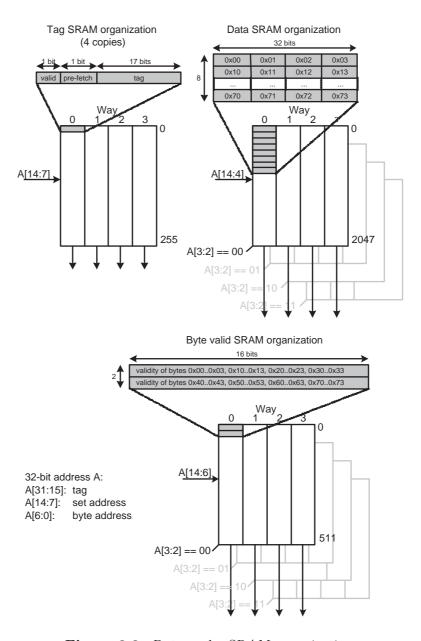

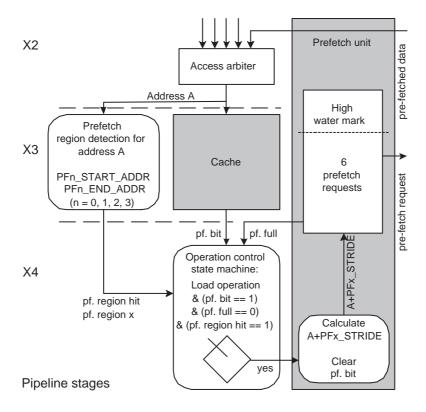

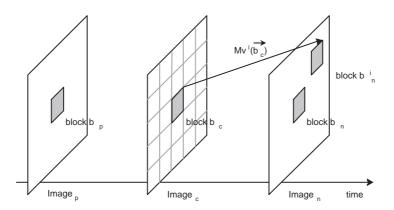

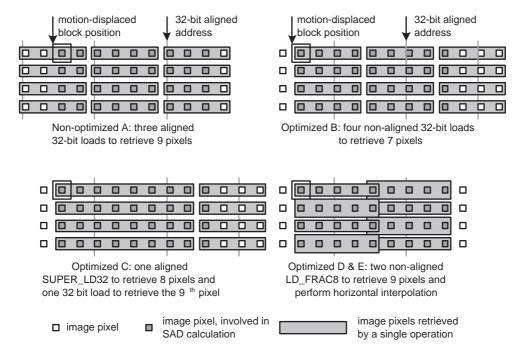

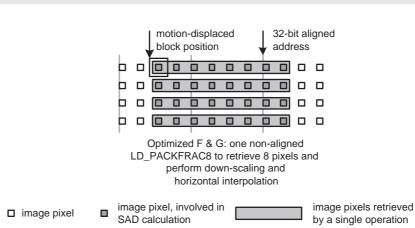

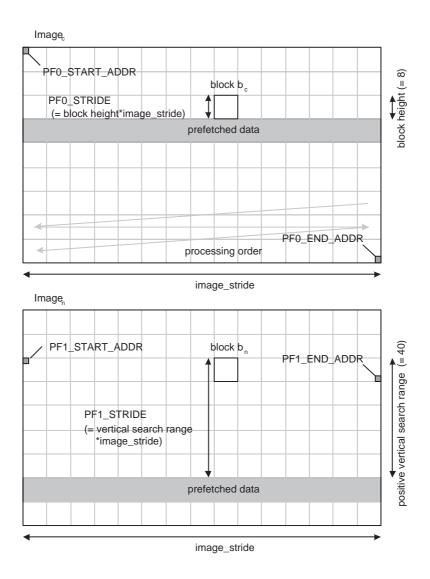

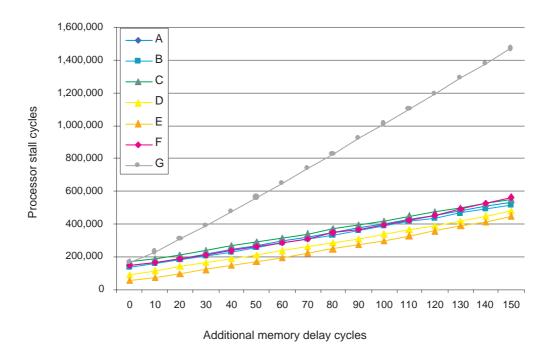

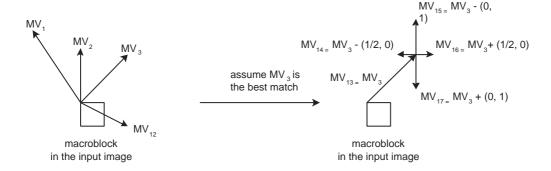

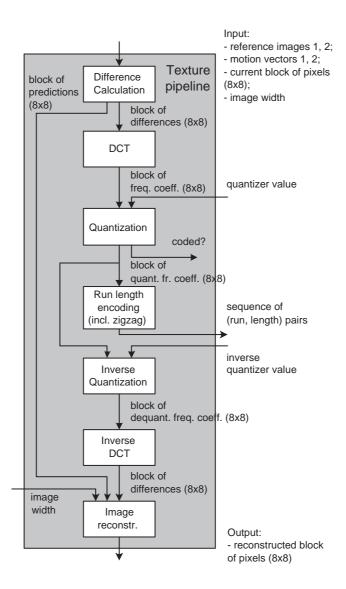

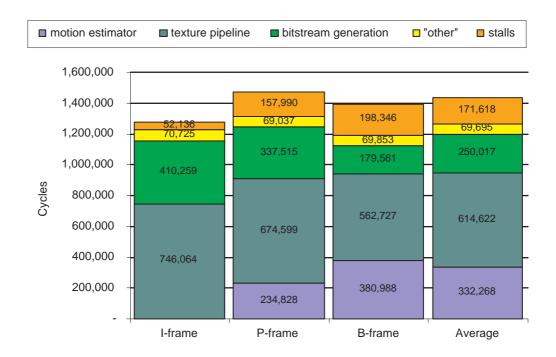

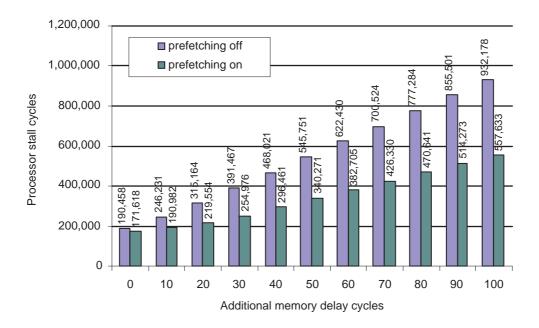

The biari\_decode\_symbol function constitutes a significant part of the computational complexity of the CABAC decoding process. The conditional constructs, table lookups, and limited parallelism result in a relative long VLIW schedule length. The use of TM3270 operations (such as the CLSAME operation to efficiently implement the renormalization) shortens the VLIW schedule length, but does not bring it down to an acceptable level.